|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

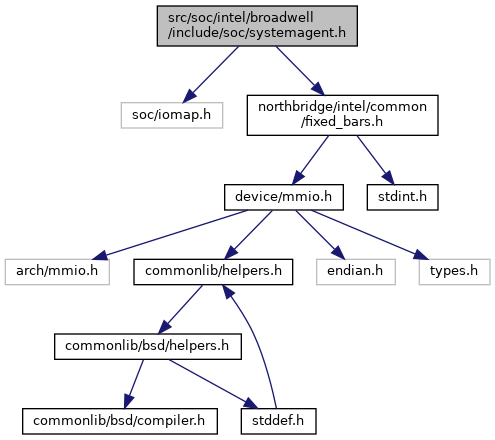

Go to the source code of this file.

Macros | |

| #define | SA_IGD_OPROM_VENDEV 0x80860406 |

| #define | IGD_HASWELL_ULT_GT1 0x0a06 |

| #define | IGD_HASWELL_ULT_GT2 0x0a16 |

| #define | IGD_HASWELL_ULT_GT3 0x0a26 |

| #define | IGD_HASWELL_ULX_GT1 0x0a0e |

| #define | IGD_HASWELL_ULX_GT2 0x0a1e |

| #define | IGD_BROADWELL_U_GT1 0x1606 |

| #define | IGD_BROADWELL_U_GT2 0x1616 |

| #define | IGD_BROADWELL_U_GT3_15W 0x1626 |

| #define | IGD_BROADWELL_U_GT3_28W 0x162b |

| #define | IGD_BROADWELL_Y_GT2 0x161e |

| #define | IGD_BROADWELL_H_GT2 0x1612 |

| #define | IGD_BROADWELL_H_GT3 0x1622 |

| #define | MCH_BROADWELL_ID_U_Y 0x1604 |

| #define | MCH_BROADWELL_REV_D0 0x06 |

| #define | MCH_BROADWELL_REV_E0 0x08 |

| #define | MCH_BROADWELL_REV_F0 0x09 |

| #define | EPBAR 0x40 |

| #define | MCHBAR 0x48 |

| #define | GGC 0x50 /* GMCH Graphics Control */ |

| #define | DEVEN 0x54 /* Device Enable */ |

| #define | DEVEN_D7EN (1 << 14) |

| #define | DEVEN_D4EN (1 << 7) |

| #define | DEVEN_D3EN (1 << 5) |

| #define | DEVEN_D2EN (1 << 4) |

| #define | DEVEN_D1F0EN (1 << 3) |

| #define | DEVEN_D1F1EN (1 << 2) |

| #define | DEVEN_D1F2EN (1 << 1) |

| #define | DEVEN_D0EN (1 << 0) |

| #define | DPR 0x5c |

| #define | DPR_EPM (1 << 2) |

| #define | DPR_PRS (1 << 1) |

| #define | DPR_SIZE_MASK 0xff0 |

| #define | PCIEXBAR 0x60 |

| #define | DMIBAR 0x68 |

| #define | MESEG_BASE 0x70 /* Management Engine Base. */ |

| #define | MESEG_LIMIT 0x78 /* Management Engine Limit. */ |

| #define | PAM0 0x80 |

| #define | PAM1 0x81 |

| #define | PAM2 0x82 |

| #define | PAM3 0x83 |

| #define | PAM4 0x84 |

| #define | PAM5 0x85 |

| #define | PAM6 0x86 |

| #define | SMRAM 0x88 /* System Management RAM Control */ |

| #define | D_OPEN (1 << 6) |

| #define | D_CLS (1 << 5) |

| #define | D_LCK (1 << 4) |

| #define | G_SMRAME (1 << 3) |

| #define | C_BASE_SEG ((0 << 2) | (1 << 1) | (0 << 0)) |

| #define | REMAPBASE 0x90 /* Remap base. */ |

| #define | REMAPLIMIT 0x98 /* Remap limit. */ |

| #define | TOM 0xa0 /* Top of DRAM in memory controller space. */ |

| #define | TOUUD 0xa8 /* Top of Upper Usable DRAM */ |

| #define | BDSM 0xb0 /* Base Data Stolen Memory */ |

| #define | BGSM 0xb4 /* Base GTT Stolen Memory */ |

| #define | TSEG 0xb8 /* TSEG base */ |

| #define | TOLUD 0xbc /* Top of Low Used Memory */ |

| #define | SKPAD 0xdc /* Scratchpad Data */ |

| #define | CAPID0_A 0xe4 |

| #define | VTD_DISABLE (1 << 23) |

| #define | ARCHDIS 0xff0 /* DMA Remap Engine Policy Control */ |

| #define | DMAR_LCKDN (1 << 31) |

| #define | PRSCAPDIS (1 << 2) |

| #define | NUM_CHANNELS 2 |

| #define | MAD_CHNL 0x5000 |

| #define | MAD_DIMM(ch) (0x5004 + 4 * (ch)) |

| #define | MRC_REVISION 0x5034 |

| #define | GFXVTBAR 0x5400 |

| #define | EDRAMBAR 0x5408 |

| #define | VTVC0BAR 0x5410 |

| #define | MCH_PAIR 0x5418 |

| #define | GDXCBAR 0x5420 |

| #define | MCH_DDR_POWER_LIMIT_LO 0x58e0 |

| #define | MCH_DDR_POWER_LIMIT_HI 0x58e4 |

| #define | MCH_PKG_POWER_LIMIT_LO 0x59a0 |

| #define | MCH_PKG_POWER_LIMIT_HI 0x59a4 |

| #define | BIOS_MAILBOX_DATA 0x5da0 |

| #define | BIOS_MAILBOX_INTERFACE 0x5da4 |

| #define | MAILBOX_RUN_BUSY (1 << 31) |

| #define | MAILBOX_BIOS_CMD_READ_PCS 1 |

| #define | MAILBOX_BIOS_CMD_WRITE_PCS 2 |

| #define | MAILBOX_BIOS_CMD_READ_CALIBRATION 0x509 |

| #define | MAILBOX_BIOS_CMD_FSM_MEASURE_INTVL 0x909 |

| #define | MAILBOX_BIOS_CMD_READ_PCH_POWER 0xa |

| #define | MAILBOX_BIOS_CMD_READ_PCH_POWER_EXT 0xb |

| #define | MAILBOX_BIOS_CMD_READ_C9C10_VOLTAGE 0x26 |

| #define | MAILBOX_BIOS_CMD_WRITE_C9C10_VOLTAGE 0x27 |

| #define | MAILBOX_BIOS_ERROR_NONE 0 |

| #define | MAILBOX_BIOS_ERROR_INVALID_COMMAND 1 |

| #define | MAILBOX_BIOS_ERROR_TIMEOUT 2 |

| #define | MAILBOX_BIOS_ERROR_ILLEGAL_DATA 3 |

| #define | MAILBOX_BIOS_ERROR_RESERVED 4 |

| #define | MAILBOX_BIOS_ERROR_ILLEGAL_VR_ID 5 |

| #define | MAILBOX_BIOS_ERROR_VR_INTERFACE_LOCKED 6 |

| #define | MAILBOX_BIOS_ERROR_VR_ERROR 7 |

| #define | BIOS_RESET_CPL 0x5da8 |

| #define | MC_BIOS_DATA 0x5e04 |

Functions | |

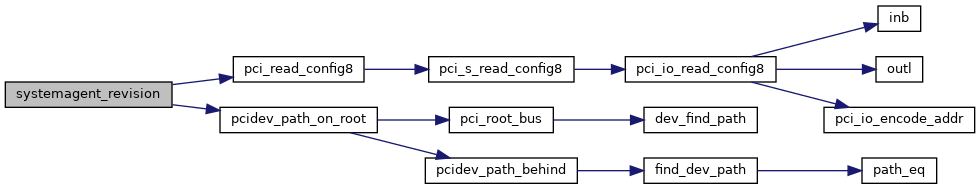

| u8 | systemagent_revision (void) |

| #define ARCHDIS 0xff0 /* DMA Remap Engine Policy Control */ |

Definition at line 80 of file systemagent.h.

| #define BDSM 0xb0 /* Base Data Stolen Memory */ |

Definition at line 71 of file systemagent.h.

| #define BGSM 0xb4 /* Base GTT Stolen Memory */ |

Definition at line 72 of file systemagent.h.

| #define BIOS_MAILBOX_DATA 0x5da0 |

Definition at line 108 of file systemagent.h.

| #define BIOS_MAILBOX_INTERFACE 0x5da4 |

Definition at line 110 of file systemagent.h.

| #define BIOS_RESET_CPL 0x5da8 |

Definition at line 131 of file systemagent.h.

| #define C_BASE_SEG ((0 << 2) | (1 << 1) | (0 << 0)) |

Definition at line 65 of file systemagent.h.

| #define CAPID0_A 0xe4 |

Definition at line 77 of file systemagent.h.

| #define D_CLS (1 << 5) |

Definition at line 62 of file systemagent.h.

| #define D_LCK (1 << 4) |

Definition at line 63 of file systemagent.h.

| #define D_OPEN (1 << 6) |

Definition at line 61 of file systemagent.h.

| #define DEVEN 0x54 /* Device Enable */ |

Definition at line 33 of file systemagent.h.

| #define DEVEN_D0EN (1 << 0) |

Definition at line 41 of file systemagent.h.

| #define DEVEN_D1F0EN (1 << 3) |

Definition at line 38 of file systemagent.h.

| #define DEVEN_D1F1EN (1 << 2) |

Definition at line 39 of file systemagent.h.

| #define DEVEN_D1F2EN (1 << 1) |

Definition at line 40 of file systemagent.h.

| #define DEVEN_D2EN (1 << 4) |

Definition at line 37 of file systemagent.h.

| #define DEVEN_D3EN (1 << 5) |

Definition at line 36 of file systemagent.h.

| #define DEVEN_D4EN (1 << 7) |

Definition at line 35 of file systemagent.h.

| #define DEVEN_D7EN (1 << 14) |

Definition at line 34 of file systemagent.h.

| #define DMAR_LCKDN (1 << 31) |

Definition at line 81 of file systemagent.h.

| #define DMIBAR 0x68 |

Definition at line 47 of file systemagent.h.

| #define DPR 0x5c |

Definition at line 42 of file systemagent.h.

| #define DPR_EPM (1 << 2) |

Definition at line 43 of file systemagent.h.

| #define DPR_PRS (1 << 1) |

Definition at line 44 of file systemagent.h.

| #define DPR_SIZE_MASK 0xff0 |

Definition at line 45 of file systemagent.h.

| #define EDRAMBAR 0x5408 |

Definition at line 96 of file systemagent.h.

| #define EPBAR 0x40 |

Definition at line 30 of file systemagent.h.

| #define G_SMRAME (1 << 3) |

Definition at line 64 of file systemagent.h.

| #define GDXCBAR 0x5420 |

Definition at line 99 of file systemagent.h.

| #define GFXVTBAR 0x5400 |

Definition at line 95 of file systemagent.h.

| #define GGC 0x50 /* GMCH Graphics Control */ |

Definition at line 32 of file systemagent.h.

| #define IGD_BROADWELL_H_GT2 0x1612 |

Definition at line 20 of file systemagent.h.

| #define IGD_BROADWELL_H_GT3 0x1622 |

Definition at line 21 of file systemagent.h.

| #define IGD_BROADWELL_U_GT1 0x1606 |

Definition at line 15 of file systemagent.h.

| #define IGD_BROADWELL_U_GT2 0x1616 |

Definition at line 16 of file systemagent.h.

| #define IGD_BROADWELL_U_GT3_15W 0x1626 |

Definition at line 17 of file systemagent.h.

| #define IGD_BROADWELL_U_GT3_28W 0x162b |

Definition at line 18 of file systemagent.h.

| #define IGD_BROADWELL_Y_GT2 0x161e |

Definition at line 19 of file systemagent.h.

| #define IGD_HASWELL_ULT_GT1 0x0a06 |

Definition at line 10 of file systemagent.h.

| #define IGD_HASWELL_ULT_GT2 0x0a16 |

Definition at line 11 of file systemagent.h.

| #define IGD_HASWELL_ULT_GT3 0x0a26 |

Definition at line 12 of file systemagent.h.

| #define IGD_HASWELL_ULX_GT1 0x0a0e |

Definition at line 13 of file systemagent.h.

| #define IGD_HASWELL_ULX_GT2 0x0a1e |

Definition at line 14 of file systemagent.h.

| #define MAD_CHNL 0x5000 |

Definition at line 90 of file systemagent.h.

Definition at line 91 of file systemagent.h.

| #define MAILBOX_BIOS_CMD_FSM_MEASURE_INTVL 0x909 |

Definition at line 115 of file systemagent.h.

| #define MAILBOX_BIOS_CMD_READ_C9C10_VOLTAGE 0x26 |

Definition at line 118 of file systemagent.h.

| #define MAILBOX_BIOS_CMD_READ_CALIBRATION 0x509 |

Definition at line 114 of file systemagent.h.

| #define MAILBOX_BIOS_CMD_READ_PCH_POWER 0xa |

Definition at line 116 of file systemagent.h.

| #define MAILBOX_BIOS_CMD_READ_PCH_POWER_EXT 0xb |

Definition at line 117 of file systemagent.h.

| #define MAILBOX_BIOS_CMD_READ_PCS 1 |

Definition at line 112 of file systemagent.h.

| #define MAILBOX_BIOS_CMD_WRITE_C9C10_VOLTAGE 0x27 |

Definition at line 119 of file systemagent.h.

| #define MAILBOX_BIOS_CMD_WRITE_PCS 2 |

Definition at line 113 of file systemagent.h.

| #define MAILBOX_BIOS_ERROR_ILLEGAL_DATA 3 |

Definition at line 125 of file systemagent.h.

| #define MAILBOX_BIOS_ERROR_ILLEGAL_VR_ID 5 |

Definition at line 127 of file systemagent.h.

| #define MAILBOX_BIOS_ERROR_INVALID_COMMAND 1 |

Definition at line 123 of file systemagent.h.

| #define MAILBOX_BIOS_ERROR_NONE 0 |

Definition at line 122 of file systemagent.h.

| #define MAILBOX_BIOS_ERROR_RESERVED 4 |

Definition at line 126 of file systemagent.h.

| #define MAILBOX_BIOS_ERROR_TIMEOUT 2 |

Definition at line 124 of file systemagent.h.

| #define MAILBOX_BIOS_ERROR_VR_ERROR 7 |

Definition at line 129 of file systemagent.h.

| #define MAILBOX_BIOS_ERROR_VR_INTERFACE_LOCKED 6 |

Definition at line 128 of file systemagent.h.

| #define MAILBOX_RUN_BUSY (1 << 31) |

Definition at line 111 of file systemagent.h.

| #define MC_BIOS_DATA 0x5e04 |

Definition at line 133 of file systemagent.h.

| #define MCH_BROADWELL_ID_U_Y 0x1604 |

Definition at line 23 of file systemagent.h.

| #define MCH_BROADWELL_REV_D0 0x06 |

Definition at line 24 of file systemagent.h.

| #define MCH_BROADWELL_REV_E0 0x08 |

Definition at line 25 of file systemagent.h.

| #define MCH_BROADWELL_REV_F0 0x09 |

Definition at line 26 of file systemagent.h.

| #define MCH_DDR_POWER_LIMIT_HI 0x58e4 |

Definition at line 102 of file systemagent.h.

| #define MCH_DDR_POWER_LIMIT_LO 0x58e0 |

Definition at line 101 of file systemagent.h.

| #define MCH_PAIR 0x5418 |

Definition at line 98 of file systemagent.h.

| #define MCH_PKG_POWER_LIMIT_HI 0x59a4 |

Definition at line 105 of file systemagent.h.

| #define MCH_PKG_POWER_LIMIT_LO 0x59a0 |

Definition at line 104 of file systemagent.h.

| #define MCHBAR 0x48 |

Definition at line 31 of file systemagent.h.

| #define MESEG_BASE 0x70 /* Management Engine Base. */ |

Definition at line 49 of file systemagent.h.

| #define MESEG_LIMIT 0x78 /* Management Engine Limit. */ |

Definition at line 50 of file systemagent.h.

| #define MRC_REVISION 0x5034 |

Definition at line 93 of file systemagent.h.

| #define NUM_CHANNELS 2 |

Definition at line 88 of file systemagent.h.

| #define PAM0 0x80 |

Definition at line 52 of file systemagent.h.

| #define PAM1 0x81 |

Definition at line 53 of file systemagent.h.

| #define PAM2 0x82 |

Definition at line 54 of file systemagent.h.

| #define PAM3 0x83 |

Definition at line 55 of file systemagent.h.

| #define PAM4 0x84 |

Definition at line 56 of file systemagent.h.

| #define PAM5 0x85 |

Definition at line 57 of file systemagent.h.

| #define PAM6 0x86 |

Definition at line 58 of file systemagent.h.

| #define PCIEXBAR 0x60 |

Definition at line 46 of file systemagent.h.

| #define PRSCAPDIS (1 << 2) |

Definition at line 82 of file systemagent.h.

| #define REMAPBASE 0x90 /* Remap base. */ |

Definition at line 67 of file systemagent.h.

| #define REMAPLIMIT 0x98 /* Remap limit. */ |

Definition at line 68 of file systemagent.h.

| #define SA_IGD_OPROM_VENDEV 0x80860406 |

Definition at line 8 of file systemagent.h.

| #define SKPAD 0xdc /* Scratchpad Data */ |

Definition at line 75 of file systemagent.h.

| #define SMRAM 0x88 /* System Management RAM Control */ |

Definition at line 60 of file systemagent.h.

| #define TOLUD 0xbc /* Top of Low Used Memory */ |

Definition at line 74 of file systemagent.h.

Definition at line 69 of file systemagent.h.

| #define TOUUD 0xa8 /* Top of Upper Usable DRAM */ |

Definition at line 70 of file systemagent.h.

| #define TSEG 0xb8 /* TSEG base */ |

Definition at line 73 of file systemagent.h.

| #define VTD_DISABLE (1 << 23) |

Definition at line 78 of file systemagent.h.

| #define VTVC0BAR 0x5410 |

Definition at line 97 of file systemagent.h.

Definition at line 18 of file northbridge.c.

References pci_read_config8(), PCI_REVISION_ID, pcidev_path_on_root(), and SA_DEVFN_ROOT.

Referenced by igd_init().