|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

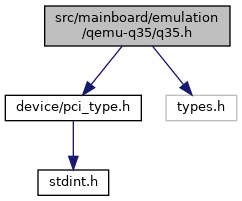

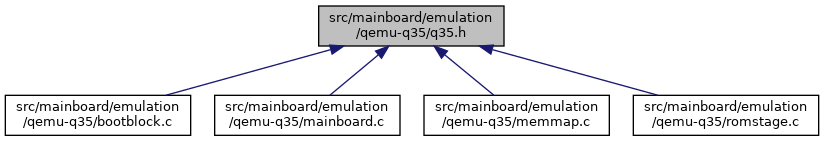

Go to the source code of this file.

Macros | |

| #define | HOST_BRIDGE PCI_DEV(0, 0, 0) |

| #define | D0F0_PCIEXBAR_LO 0x60 |

| #define | D0F0_PCIEXBAR_HI 0x64 |

| #define | D0F0_PAM(x) (0x90 + (x)) /* 0-6 */ |

| #define | SMRAMC 0x9d |

| #define | G_SMRAME (1 << 3) |

| #define | D_LCK (1 << 4) |

| #define | D_CLS (1 << 5) |

| #define | D_OPEN (1 << 6) |

| #define | ESMRAMC 0x9e |

| #define | T_EN (1 << 0) |

| #define | TSEG_SZ_MASK (3 << 1) |

| #define | H_SMRAME (1 << 7) |

Functions | |

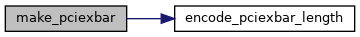

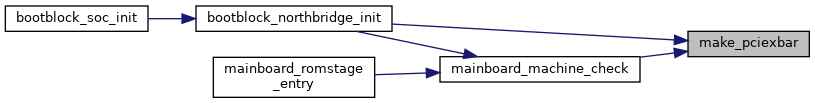

| uint32_t | make_pciexbar (void) |

| void | mainboard_machine_check (void) |

Definition at line 31 of file memmap.c.

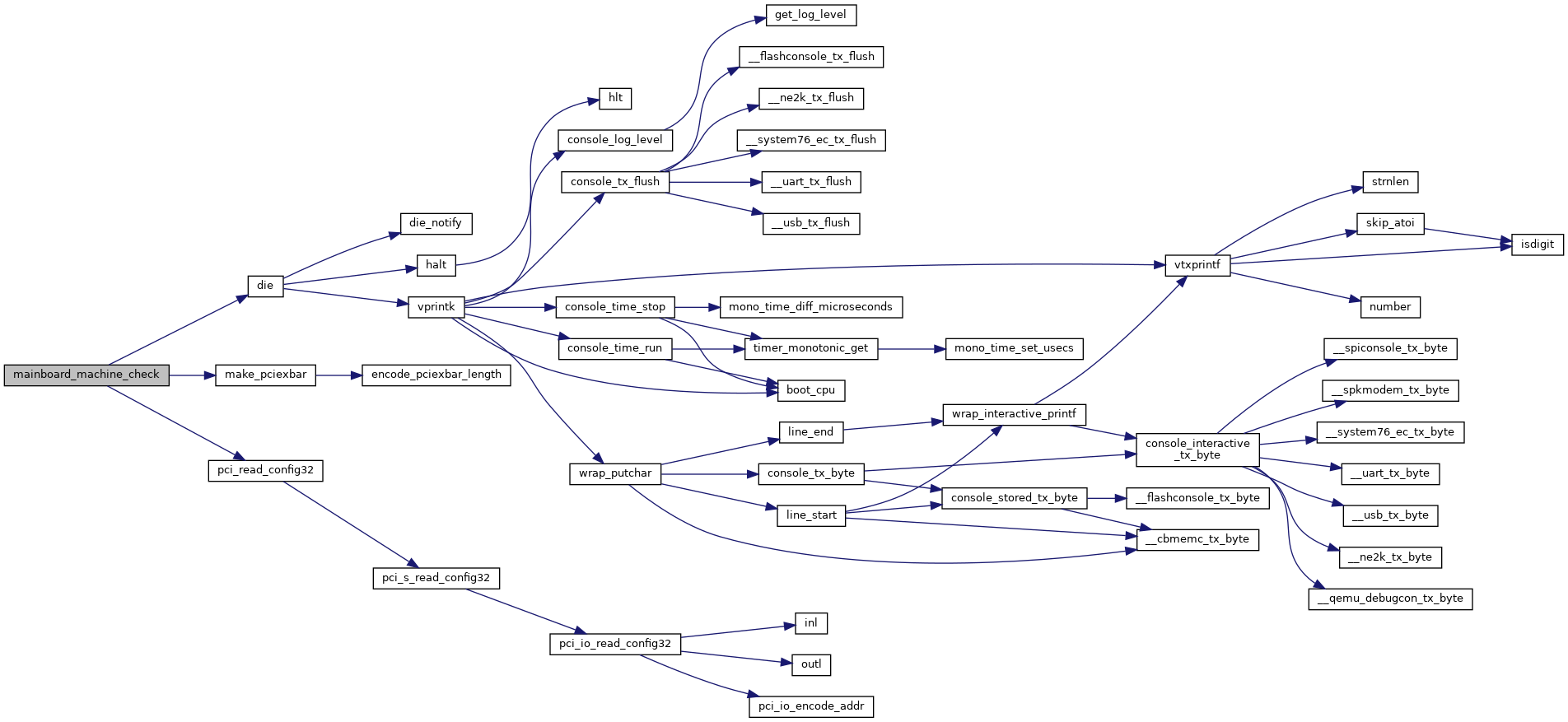

References D0F0_PCIEXBAR_LO, die(), HOST_BRIDGE, make_pciexbar(), and pci_read_config32().

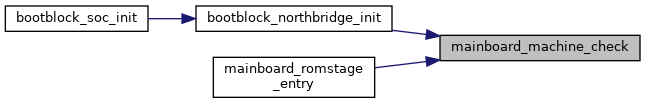

Referenced by bootblock_northbridge_init(), and mainboard_romstage_entry().

Definition at line 25 of file memmap.c.

References encode_pciexbar_length().

Referenced by bootblock_northbridge_init(), and mainboard_machine_check().