|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

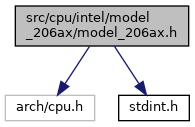

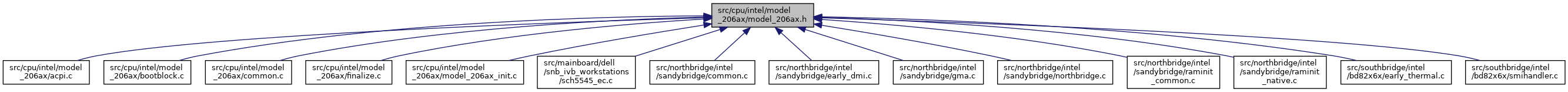

Go to the source code of this file.

Macros | |

| #define | SNB_STEP_B2 2 |

| #define | SNB_STEP_C0 3 |

| #define | SNB_STEP_D0 5 /* Also J0 */ |

| #define | SNB_STEP_D1 6 |

| #define | SNB_STEP_D2 7 /* Also J1/Q0 */ |

| #define | IVB_STEP_A0 0 |

| #define | IVB_STEP_B0 2 |

| #define | IVB_STEP_C0 4 |

| #define | IVB_STEP_K0 5 |

| #define | IVB_STEP_D0 6 |

| #define | IVB_STEP_E0 8 |

| #define | IVB_STEP_E1 9 |

| #define | IS_SANDY_CPU(x) ((x & 0xffff0) == 0x206a0) |

| #define | IS_SANDY_CPU_C(x) ((x & 0xf) == 4) |

| #define | IS_SANDY_CPU_D0(x) ((x & 0xf) == 5) |

| #define | IS_SANDY_CPU_D1(x) ((x & 0xf) == 6) |

| #define | IS_SANDY_CPU_D2(x) ((x & 0xf) == 7) |

| #define | IS_IVY_CPU(x) ((x & 0xffff0) == 0x306a0) |

| #define | IS_IVY_CPU_C(x) ((x & 0xf) == 4) |

| #define | IS_IVY_CPU_K(x) ((x & 0xf) == 5) |

| #define | IS_IVY_CPU_D(x) ((x & 0xf) == 6) |

| #define | IS_IVY_CPU_E(x) ((x & 0xf) >= 8) |

| #define | SANDYBRIDGE_BCLK 100 |

| #define | MSR_CORE_THREAD_COUNT 0x35 |

| #define | MSR_FEATURE_CONFIG 0x13c |

| #define | MSR_FLEX_RATIO 0x194 |

| #define | FLEX_RATIO_LOCK (1 << 20) |

| #define | FLEX_RATIO_EN (1 << 16) |

| #define | MSR_TEMPERATURE_TARGET 0x1a2 |

| #define | MSR_LT_LOCK_MEMORY 0x2e7 |

| #define | MSR_PLATFORM_INFO 0xce |

| #define | PLATFORM_INFO_SET_TDP (1 << 29) |

| #define | MSR_MISC_PWR_MGMT 0x1aa |

| #define | MISC_PWR_MGMT_EIST_HW_DIS (1 << 0) |

| #define | MSR_TURBO_RATIO_LIMIT 0x1ad |

| #define | MSR_POWER_CTL 0x1fc |

| #define | MSR_PKGC3_IRTL 0x60a |

| #define | MSR_PKGC6_IRTL 0x60b |

| #define | MSR_PKGC7_IRTL 0x60c |

| #define | IRTL_VALID (1 << 15) |

| #define | IRTL_1_NS (0 << 10) |

| #define | IRTL_32_NS (1 << 10) |

| #define | IRTL_1024_NS (2 << 10) |

| #define | IRTL_32768_NS (3 << 10) |

| #define | IRTL_1048576_NS (4 << 10) |

| #define | IRTL_33554432_NS (5 << 10) |

| #define | IRTL_RESPONSE_MASK (0x3ff) |

| #define | MSR_PKG_POWER_LIMIT 0x610 |

| #define | PKG_POWER_LIMIT_MASK 0x7fff |

| #define | PKG_POWER_LIMIT_EN (1 << 15) |

| #define | PKG_POWER_LIMIT_CLAMP (1 << 16) |

| #define | PKG_POWER_LIMIT_TIME_SHIFT 17 |

| #define | PKG_POWER_LIMIT_TIME_MASK 0x7f |

| #define | MSR_PP0_CURRENT_CONFIG 0x601 |

| #define | PP0_CURRENT_LIMIT (112 << 3) /* 112 A */ |

| #define | MSR_PP1_CURRENT_CONFIG 0x602 |

| #define | PP1_CURRENT_LIMIT_SNB (35 << 3) /* 35 A */ |

| #define | PP1_CURRENT_LIMIT_IVB (50 << 3) /* 50 A */ |

| #define | MSR_PKG_POWER_SKU_UNIT 0x606 |

| #define | MSR_PKG_POWER_SKU 0x614 |

| #define | MSR_PP0_POWER_LIMIT 0x638 |

| #define | MSR_PP1_POWER_LIMIT 0x640 |

| #define | IVB_CONFIG_TDP_MIN_CPUID 0x306a2 |

| #define | MSR_CONFIG_TDP_NOMINAL 0x648 |

| #define | MSR_CONFIG_TDP_LEVEL1 0x649 |

| #define | MSR_CONFIG_TDP_LEVEL2 0x64a |

| #define | MSR_CONFIG_TDP_CONTROL 0x64b |

| #define | MSR_TURBO_ACTIVATION_RATIO 0x64c |

| #define | PSS_MAX_ENTRIES 8 |

| #define | PSS_RATIO_STEP 2 |

| #define | PSS_LATENCY_TRANSITION 10 |

| #define | PSS_LATENCY_BUSMASTER 10 |

Functions | |

| void | intel_model_206ax_finalize_smm (void) |

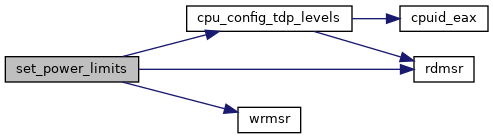

| void | set_power_limits (u8 power_limit_1_time) |

| int | cpu_config_tdp_levels (void) |

| int | get_platform_id (void) |

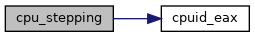

| static u8 | cpu_stepping (void) |

| #define FLEX_RATIO_EN (1 << 16) |

Definition at line 44 of file model_206ax.h.

| #define FLEX_RATIO_LOCK (1 << 20) |

Definition at line 43 of file model_206ax.h.

| #define IRTL_1024_NS (2 << 10) |

Definition at line 61 of file model_206ax.h.

| #define IRTL_1048576_NS (4 << 10) |

Definition at line 63 of file model_206ax.h.

| #define IRTL_1_NS (0 << 10) |

Definition at line 59 of file model_206ax.h.

| #define IRTL_32768_NS (3 << 10) |

Definition at line 62 of file model_206ax.h.

| #define IRTL_32_NS (1 << 10) |

Definition at line 60 of file model_206ax.h.

| #define IRTL_33554432_NS (5 << 10) |

Definition at line 64 of file model_206ax.h.

| #define IRTL_RESPONSE_MASK (0x3ff) |

Definition at line 65 of file model_206ax.h.

| #define IRTL_VALID (1 << 15) |

Definition at line 58 of file model_206ax.h.

Definition at line 31 of file model_206ax.h.

Definition at line 32 of file model_206ax.h.

Definition at line 34 of file model_206ax.h.

Definition at line 35 of file model_206ax.h.

Definition at line 33 of file model_206ax.h.

Definition at line 25 of file model_206ax.h.

Definition at line 26 of file model_206ax.h.

Definition at line 27 of file model_206ax.h.

Definition at line 28 of file model_206ax.h.

Definition at line 29 of file model_206ax.h.

| #define IVB_CONFIG_TDP_MIN_CPUID 0x306a2 |

Definition at line 85 of file model_206ax.h.

| #define IVB_STEP_A0 0 |

Definition at line 17 of file model_206ax.h.

| #define IVB_STEP_B0 2 |

Definition at line 18 of file model_206ax.h.

| #define IVB_STEP_C0 4 |

Definition at line 19 of file model_206ax.h.

| #define IVB_STEP_D0 6 |

Definition at line 21 of file model_206ax.h.

| #define IVB_STEP_E0 8 |

Definition at line 22 of file model_206ax.h.

| #define IVB_STEP_E1 9 |

Definition at line 23 of file model_206ax.h.

| #define IVB_STEP_K0 5 |

Definition at line 20 of file model_206ax.h.

| #define MISC_PWR_MGMT_EIST_HW_DIS (1 << 0) |

Definition at line 51 of file model_206ax.h.

| #define MSR_CONFIG_TDP_CONTROL 0x64b |

Definition at line 89 of file model_206ax.h.

| #define MSR_CONFIG_TDP_LEVEL1 0x649 |

Definition at line 87 of file model_206ax.h.

| #define MSR_CONFIG_TDP_LEVEL2 0x64a |

Definition at line 88 of file model_206ax.h.

| #define MSR_CONFIG_TDP_NOMINAL 0x648 |

Definition at line 86 of file model_206ax.h.

| #define MSR_CORE_THREAD_COUNT 0x35 |

Definition at line 40 of file model_206ax.h.

| #define MSR_FEATURE_CONFIG 0x13c |

Definition at line 41 of file model_206ax.h.

| #define MSR_FLEX_RATIO 0x194 |

Definition at line 42 of file model_206ax.h.

| #define MSR_LT_LOCK_MEMORY 0x2e7 |

Definition at line 46 of file model_206ax.h.

| #define MSR_MISC_PWR_MGMT 0x1aa |

Definition at line 50 of file model_206ax.h.

| #define MSR_PKG_POWER_LIMIT 0x610 |

Definition at line 68 of file model_206ax.h.

| #define MSR_PKG_POWER_SKU 0x614 |

Definition at line 81 of file model_206ax.h.

| #define MSR_PKG_POWER_SKU_UNIT 0x606 |

Definition at line 80 of file model_206ax.h.

| #define MSR_PKGC3_IRTL 0x60a |

Definition at line 55 of file model_206ax.h.

| #define MSR_PKGC6_IRTL 0x60b |

Definition at line 56 of file model_206ax.h.

| #define MSR_PKGC7_IRTL 0x60c |

Definition at line 57 of file model_206ax.h.

| #define MSR_PLATFORM_INFO 0xce |

Definition at line 47 of file model_206ax.h.

| #define MSR_POWER_CTL 0x1fc |

Definition at line 53 of file model_206ax.h.

| #define MSR_PP0_CURRENT_CONFIG 0x601 |

Definition at line 75 of file model_206ax.h.

| #define MSR_PP0_POWER_LIMIT 0x638 |

Definition at line 82 of file model_206ax.h.

| #define MSR_PP1_CURRENT_CONFIG 0x602 |

Definition at line 77 of file model_206ax.h.

| #define MSR_PP1_POWER_LIMIT 0x640 |

Definition at line 83 of file model_206ax.h.

| #define MSR_TEMPERATURE_TARGET 0x1a2 |

Definition at line 45 of file model_206ax.h.

| #define MSR_TURBO_ACTIVATION_RATIO 0x64c |

Definition at line 90 of file model_206ax.h.

| #define MSR_TURBO_RATIO_LIMIT 0x1ad |

Definition at line 52 of file model_206ax.h.

| #define PKG_POWER_LIMIT_CLAMP (1 << 16) |

Definition at line 71 of file model_206ax.h.

| #define PKG_POWER_LIMIT_EN (1 << 15) |

Definition at line 70 of file model_206ax.h.

| #define PKG_POWER_LIMIT_MASK 0x7fff |

Definition at line 69 of file model_206ax.h.

| #define PKG_POWER_LIMIT_TIME_MASK 0x7f |

Definition at line 73 of file model_206ax.h.

| #define PKG_POWER_LIMIT_TIME_SHIFT 17 |

Definition at line 72 of file model_206ax.h.

| #define PLATFORM_INFO_SET_TDP (1 << 29) |

Definition at line 48 of file model_206ax.h.

| #define PP0_CURRENT_LIMIT (112 << 3) /* 112 A */ |

Definition at line 76 of file model_206ax.h.

| #define PP1_CURRENT_LIMIT_IVB (50 << 3) /* 50 A */ |

Definition at line 79 of file model_206ax.h.

| #define PP1_CURRENT_LIMIT_SNB (35 << 3) /* 35 A */ |

Definition at line 78 of file model_206ax.h.

| #define PSS_LATENCY_BUSMASTER 10 |

Definition at line 96 of file model_206ax.h.

| #define PSS_LATENCY_TRANSITION 10 |

Definition at line 95 of file model_206ax.h.

| #define PSS_MAX_ENTRIES 8 |

Definition at line 93 of file model_206ax.h.

| #define PSS_RATIO_STEP 2 |

Definition at line 94 of file model_206ax.h.

| #define SANDYBRIDGE_BCLK 100 |

Definition at line 38 of file model_206ax.h.

| #define SNB_STEP_B2 2 |

Definition at line 10 of file model_206ax.h.

| #define SNB_STEP_C0 3 |

Definition at line 11 of file model_206ax.h.

| #define SNB_STEP_D0 5 /* Also J0 */ |

Definition at line 12 of file model_206ax.h.

| #define SNB_STEP_D1 6 |

Definition at line 13 of file model_206ax.h.

| #define SNB_STEP_D2 7 /* Also J1/Q0 */ |

Definition at line 14 of file model_206ax.h.

| int cpu_config_tdp_levels | ( | void | ) |

Definition at line 300 of file haswell_init.c.

Definition at line 120 of file model_206ax.h.

References cpuid_eax().

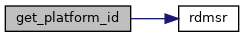

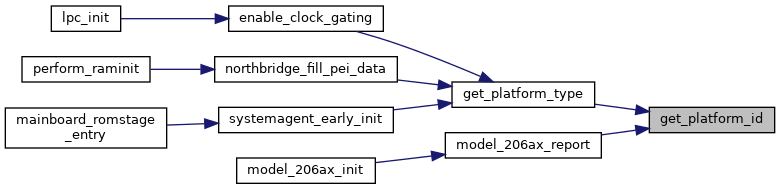

| int get_platform_id | ( | void | ) |

Definition at line 6 of file common.c.

References msr_struct::hi, IA32_PLATFORM_ID, and rdmsr().

Referenced by get_platform_type(), and model_206ax_report().

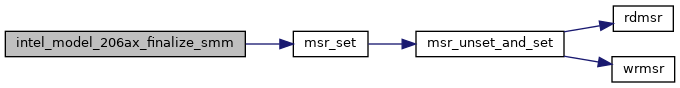

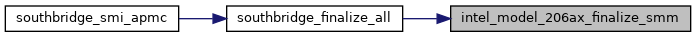

Definition at line 13 of file finalize.c.

References BIT, MSR_LT_LOCK_MEMORY, MSR_MISC_PWR_MGMT, and msr_set().

Referenced by southbridge_finalize_all().

Definition at line 313 of file haswell_init.c.

References ARRAY_SIZE, BIOS_DEBUG, cpu_config_tdp_levels(), msr_struct::hi, msr_struct::lo, MSR_CONFIG_TDP_NOMINAL, MSR_PKG_POWER_LIMIT, MSR_PKG_POWER_SKU, MSR_PKG_POWER_SKU_UNIT, MSR_PLATFORM_INFO, MSR_TURBO_ACTIVATION_RATIO, PKG_POWER_LIMIT_EN, PKG_POWER_LIMIT_MASK, PKG_POWER_LIMIT_TIME_MASK, PKG_POWER_LIMIT_TIME_SHIFT, PLATFORM_INFO_SET_TDP, power_limit_time_msr_to_sec, power_limit_time_sec_to_msr, printk, rdmsr(), and wrmsr().