|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

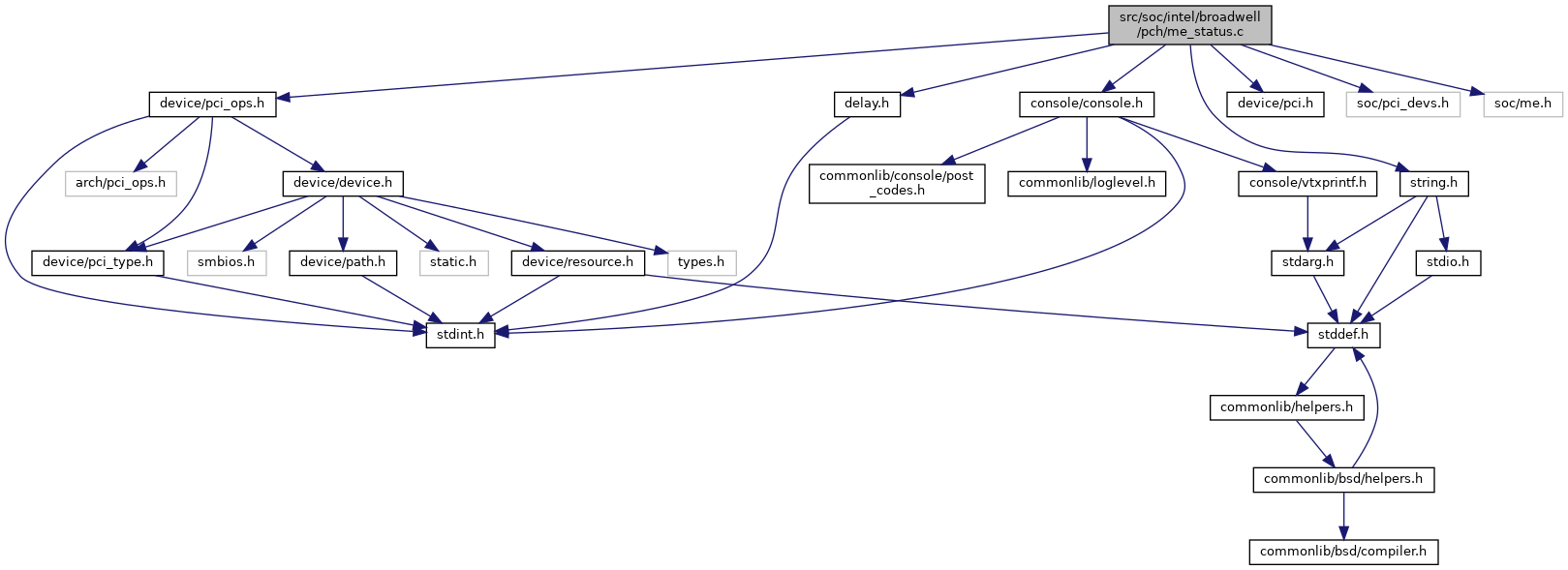

#include <device/pci_ops.h>#include <console/console.h>#include <device/pci.h>#include <string.h>#include <soc/pci_devs.h>#include <soc/me.h>#include <delay.h>

Go to the source code of this file.

Macros | |

| #define | ARRAY_TO_ELEMENT(__array__, __index__, __default__) |

Functions | |

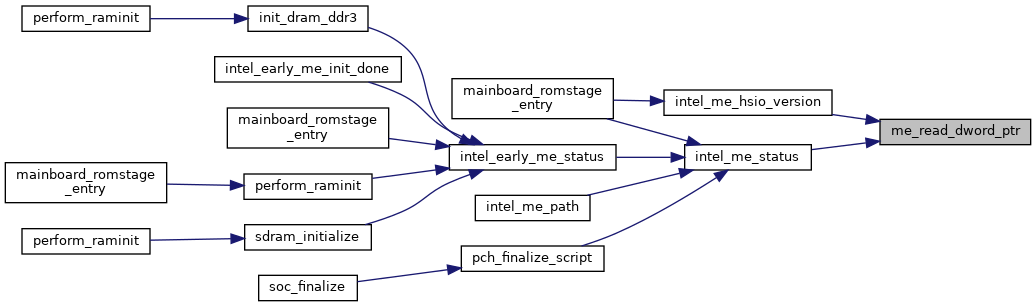

| static void | me_read_dword_ptr (void *ptr, int offset) |

| void | intel_me_status (void) |

| void | intel_me_hsio_version (uint16_t *version, uint16_t *checksum) |

Variables | |

| static const char * | me_cws_values [] |

| static const char * | me_opstate_values [] |

| static const char * | me_opmode_values [] |

| static const char * | me_error_values [] |

| static const char * | me_progress_values [] |

| static const char * | me_pmevent_values [] |

| static const char * | me_progress_rom_values [] |

| static const char * | me_progress_bup_values [] |

| static const char * | me_progress_policy_values [] |

| #define ARRAY_TO_ELEMENT | ( | __array__, | |

| __index__, | |||

| __default__ | |||

| ) |

Definition at line 11 of file me_status.c.

Definition at line 292 of file me_status.c.

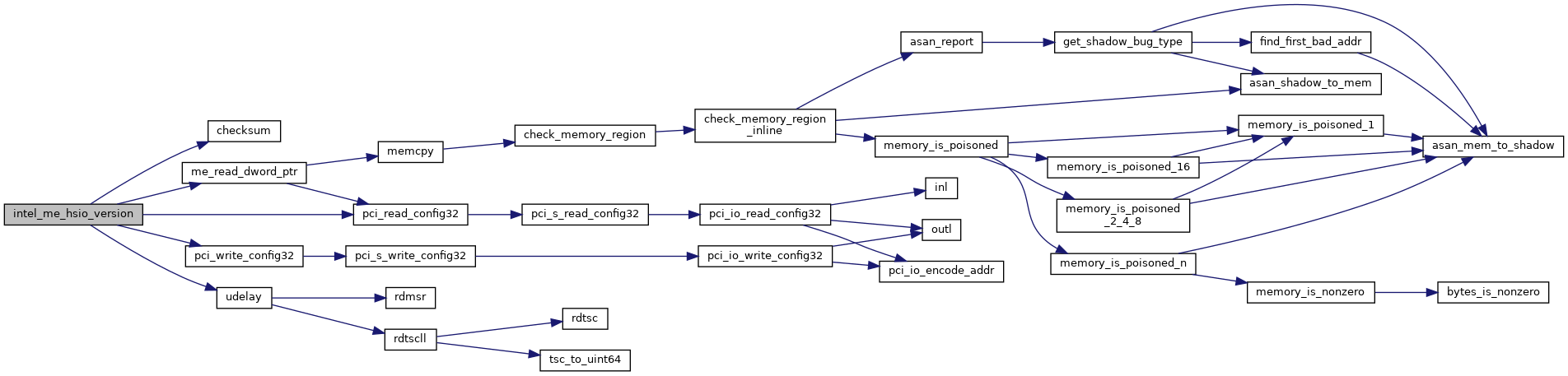

References BIOS_DEBUG, BIOS_ERR, me_hfs::bios_msg_ack, checksum(), count, ME_DELAY, ME_HSIO_CMD_GETHSIOVER, ME_HSIO_MESSAGE, me_read_dword_ptr(), ME_RETRY, PCH_DEV_ME, PCI_ME_H_GS, PCI_ME_HFS, PCI_ME_HFS5, pci_read_config32(), pci_write_config32(), printk, udelay(), and version.

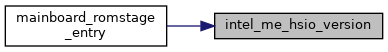

Referenced by mainboard_romstage_entry().

Definition at line 194 of file me_status.c.

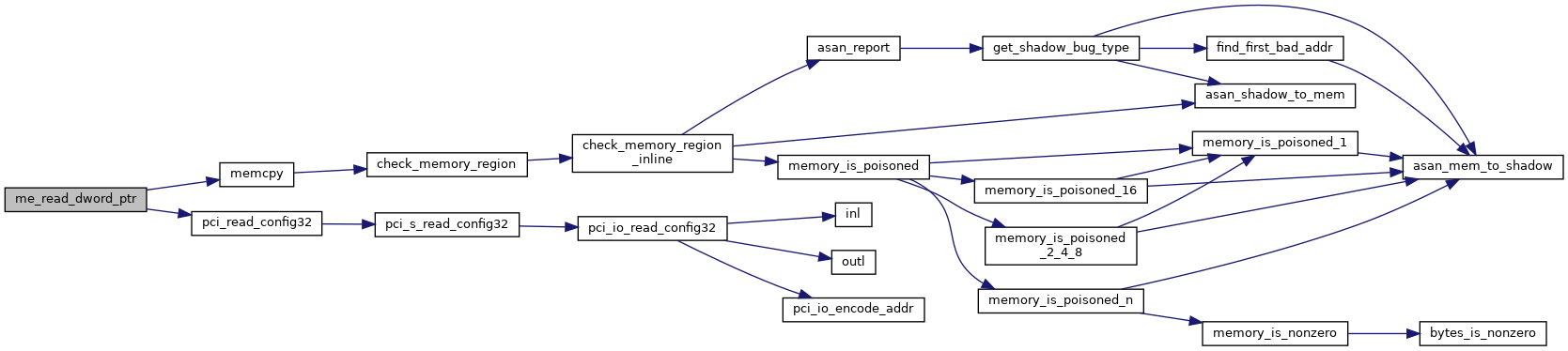

Definition at line 16 of file me_status.c.

References memcpy(), offset, PCH_DEV_ME, and pci_read_config32().

Referenced by intel_me_hsio_version(), and intel_me_status().

|

static |

Definition at line 23 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 62 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 53 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 43 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 81 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 117 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 171 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 111 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 70 of file me_status.c.

Referenced by intel_me_status().