|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

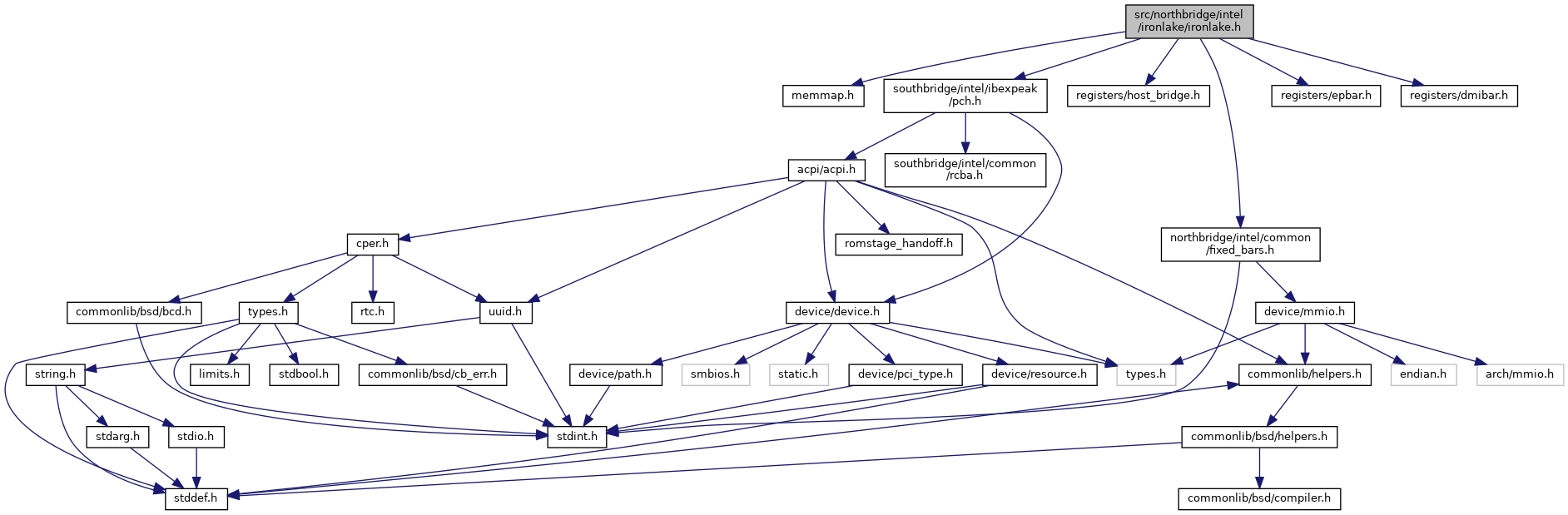

#include "memmap.h"#include <southbridge/intel/ibexpeak/pch.h>#include "registers/host_bridge.h"#include <northbridge/intel/common/fixed_bars.h>#include "registers/epbar.h"#include "registers/dmibar.h"

Go to the source code of this file.

Macros | |

| #define | PEG_CAP 0xa2 |

| #define | SLOTCAP 0xb4 |

| #define | PEGLC 0xec |

| #define | D1F0_VCCAP 0x104 |

| #define | D1F0_VC0RCTL 0x114 |

| #define | IRONLAKE_MOBILE 0 |

| #define | IRONLAKE_DESKTOP 1 |

| #define | IRONLAKE_SERVER 2 |

| #define | QUICKPATH_BUS (CONFIG_ECAM_MMCONF_BUS_NUMBER - 1) |

| #define | QPI_NON_CORE PCI_DEV(QUICKPATH_BUS, 0, 0) |

| #define | MAX_RTIDS 0x60 |

| #define | DESIRED_CORES 0x80 |

| #define | MIRROR_PORT_CTL 0xd0 |

| #define | QPI_SAD PCI_DEV(QUICKPATH_BUS, 0, 1) |

| #define | QPD0F1_PAM(x) (0x40 + (x)) /* 0-6 */ |

| #define | QPD0F1_SMRAM 0x4d /* System Management RAM Control */ |

| #define | SAD_PCIEXBAR 0x50 |

| #define | SAD_DRAM_RULE(x) (0x80 + 4 * (x)) /* 0-7 */ |

| #define | SAD_INTERLEAVE_LIST(x) (0xc0 + 4 * (x)) /* 0-7 */ |

| #define | QPI_LINK_0 PCI_DEV(QUICKPATH_BUS, 2, 0) |

| #define | QPI_QPILCP 0x40 /* QPI Link Capability */ |

| #define | QPI_QPILCL 0x48 /* QPI Link Control */ |

| #define | QPI_QPILS 0x50 /* QPI Link Status */ |

| #define | QPI_DEF_RMT_VN_CREDITS 0x58 /* Default Available Remote Credits */ |

| #define | QPI_PHY_0 PCI_DEV(QUICKPATH_BUS, 2, 1) |

| #define | QPI_PLL_STATUS 0x50 |

| #define | QPI_PLL_RATIO 0x54 |

| #define | QPI_PHY_CAPABILITY 0x68 /* QPI Phys. Layer Capability */ |

| #define | QPI_PHY_CONTROL 0x6c /* QPI Phys. Layer Control */ |

| #define | QPI_PHY_INIT_STATUS 0x80 /* QPI Phys. Layer Initialization Status */ |

| #define | QPI_PHY_PRIM_TIMEOUT 0x94 /* QPI Phys. Layer Primary Timeout Value */ |

| #define | QPI_PHY_PWR_MGMT 0xd0 /* QPI Phys. Layer Power Management */ |

| #define | QPI_PHY_EP_SELECT 0xe0 /* QPI Phys. Layer Electrical Parameter Select */ |

| #define | QPI_PHY_EP_MCTR 0xf4 /* QPI Phys. Layer Electrical Parameter Misc. Control */ |

| #define | MSAC 0x62 /* Multi Size Aperture Control */ |

Functions | |

| void | intel_ironlake_finalize_smm (void) |

| int | bridge_silicon_revision (void) |

| void | ironlake_early_initialization (int chipset_type) |

| void | ironlake_late_initialization (void) |

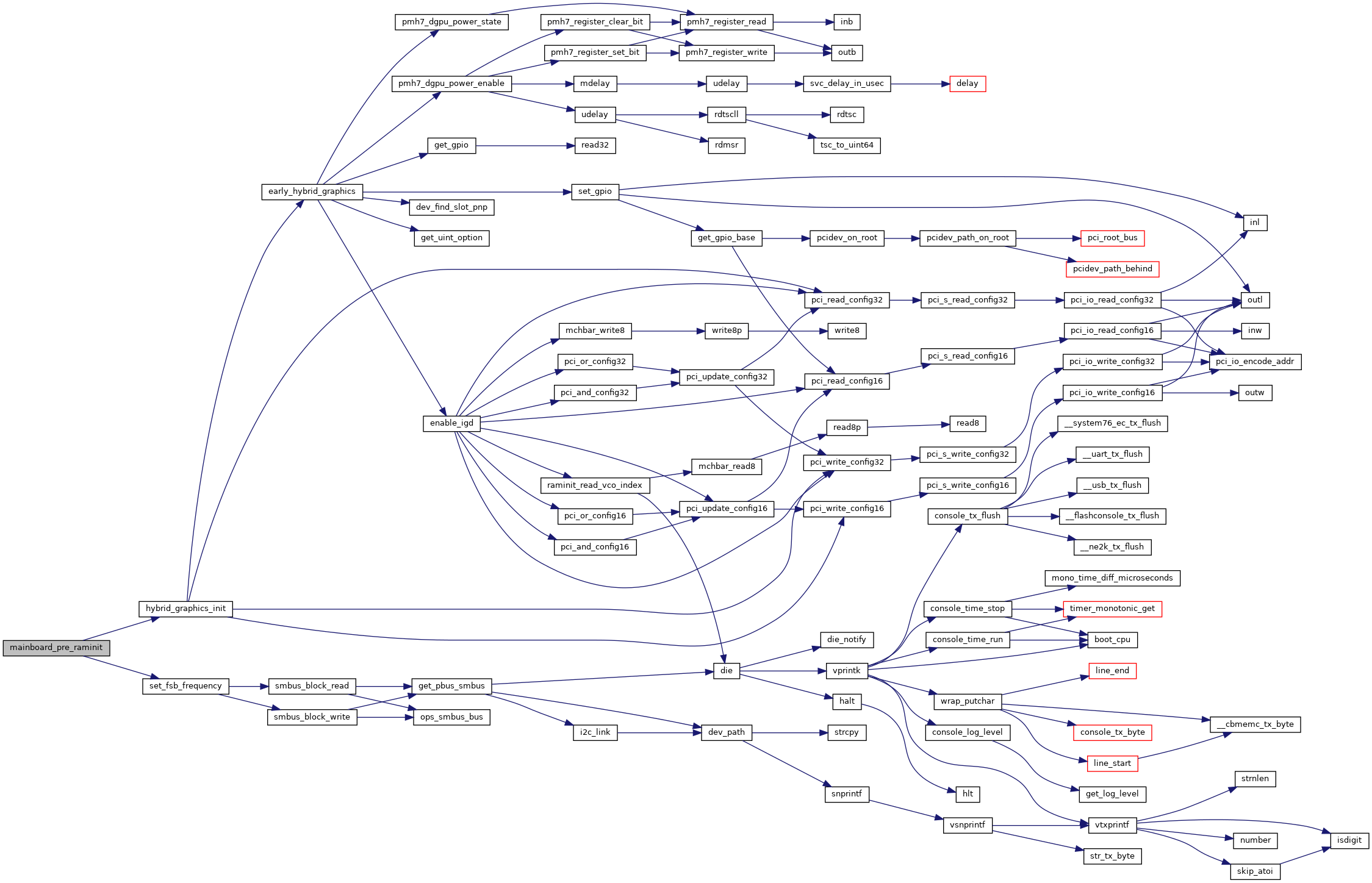

| void | mainboard_pre_raminit (void) |

| void | mainboard_get_spd_map (u8 *spd_addrmap) |

| #define D1F0_VC0RCTL 0x114 |

Definition at line 13 of file ironlake.h.

| #define D1F0_VCCAP 0x104 |

Definition at line 12 of file ironlake.h.

| #define DESIRED_CORES 0x80 |

Definition at line 39 of file ironlake.h.

| #define IRONLAKE_DESKTOP 1 |

Definition at line 17 of file ironlake.h.

| #define IRONLAKE_MOBILE 0 |

Definition at line 16 of file ironlake.h.

| #define IRONLAKE_SERVER 2 |

Definition at line 18 of file ironlake.h.

| #define MAX_RTIDS 0x60 |

Definition at line 38 of file ironlake.h.

| #define MIRROR_PORT_CTL 0xd0 |

Definition at line 40 of file ironlake.h.

| #define MSAC 0x62 /* Multi Size Aperture Control */ |

Definition at line 83 of file ironlake.h.

| #define PEG_CAP 0xa2 |

Definition at line 9 of file ironlake.h.

| #define PEGLC 0xec |

Definition at line 11 of file ironlake.h.

Definition at line 47 of file ironlake.h.

| #define QPD0F1_SMRAM 0x4d /* System Management RAM Control */ |

Definition at line 48 of file ironlake.h.

| #define QPI_DEF_RMT_VN_CREDITS 0x58 /* Default Available Remote Credits */ |

Definition at line 63 of file ironlake.h.

| #define QPI_LINK_0 PCI_DEV(QUICKPATH_BUS, 2, 0) |

Definition at line 58 of file ironlake.h.

| #define QPI_NON_CORE PCI_DEV(QUICKPATH_BUS, 0, 0) |

Definition at line 36 of file ironlake.h.

| #define QPI_PHY_0 PCI_DEV(QUICKPATH_BUS, 2, 1) |

Definition at line 68 of file ironlake.h.

| #define QPI_PHY_CAPABILITY 0x68 /* QPI Phys. Layer Capability */ |

Definition at line 72 of file ironlake.h.

| #define QPI_PHY_CONTROL 0x6c /* QPI Phys. Layer Control */ |

Definition at line 73 of file ironlake.h.

| #define QPI_PHY_EP_MCTR 0xf4 /* QPI Phys. Layer Electrical Parameter Misc. Control */ |

Definition at line 78 of file ironlake.h.

| #define QPI_PHY_EP_SELECT 0xe0 /* QPI Phys. Layer Electrical Parameter Select */ |

Definition at line 77 of file ironlake.h.

| #define QPI_PHY_INIT_STATUS 0x80 /* QPI Phys. Layer Initialization Status */ |

Definition at line 74 of file ironlake.h.

| #define QPI_PHY_PRIM_TIMEOUT 0x94 /* QPI Phys. Layer Primary Timeout Value */ |

Definition at line 75 of file ironlake.h.

| #define QPI_PHY_PWR_MGMT 0xd0 /* QPI Phys. Layer Power Management */ |

Definition at line 76 of file ironlake.h.

| #define QPI_PLL_RATIO 0x54 |

Definition at line 71 of file ironlake.h.

| #define QPI_PLL_STATUS 0x50 |

Definition at line 70 of file ironlake.h.

| #define QPI_QPILCL 0x48 /* QPI Link Control */ |

Definition at line 61 of file ironlake.h.

| #define QPI_QPILCP 0x40 /* QPI Link Capability */ |

Definition at line 60 of file ironlake.h.

| #define QPI_QPILS 0x50 /* QPI Link Status */ |

Definition at line 62 of file ironlake.h.

| #define QPI_SAD PCI_DEV(QUICKPATH_BUS, 0, 1) |

Definition at line 45 of file ironlake.h.

| #define QUICKPATH_BUS (CONFIG_ECAM_MMCONF_BUS_NUMBER - 1) |

Definition at line 22 of file ironlake.h.

Definition at line 52 of file ironlake.h.

Definition at line 53 of file ironlake.h.

| #define SAD_PCIEXBAR 0x50 |

Definition at line 50 of file ironlake.h.

| #define SLOTCAP 0xb4 |

Definition at line 10 of file ironlake.h.

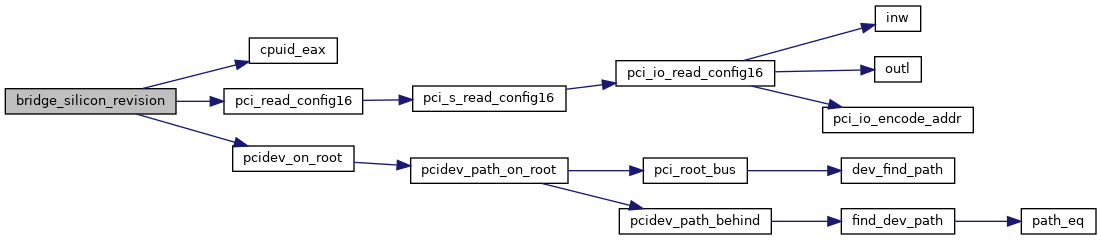

| int bridge_silicon_revision | ( | void | ) |

Definition at line 19 of file northbridge.c.

References bridge_revision_id, cpuid_eax(), PCI_DEVICE_ID, pci_read_config16(), pcidev_on_root(), and stepping.

Definition at line 5 of file finalize.c.

Referenced by southbridge_finalize_all().

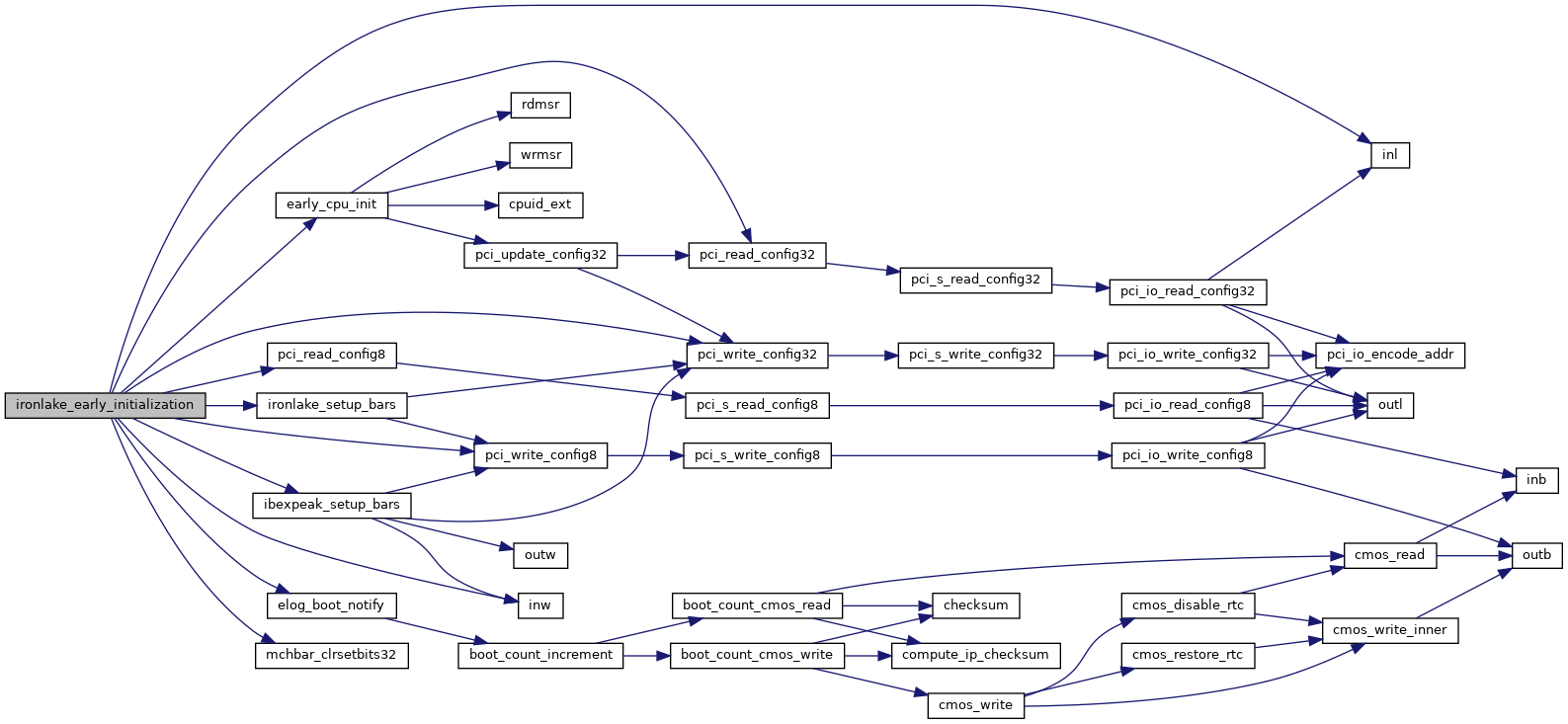

| void ironlake_early_initialization | ( | int | chipset_type | ) |

Definition at line 77 of file early_init.c.

References DEFAULT_PMBASE, DEVEN, DEVEN_HOST, DEVEN_IGD, DEVEN_PEG10, early_cpu_init(), elog_boot_notify(), ibexpeak_setup_bars(), inl(), inw(), IRONLAKE_MOBILE, ironlake_setup_bars(), mchbar_clrsetbits32(), PCI_DEV, pci_read_config32(), pci_read_config8(), pci_write_config32(), pci_write_config8(), PM1_CNT, PM1_STS, SLP_TYP_S3, and WAK_STS.

Referenced by mainboard_romstage_entry().

Definition at line 55 of file romstage.c.

Referenced by mainboard_romstage_entry().

Definition at line 50 of file romstage.c.

References hybrid_graphics_init(), and set_fsb_frequency().