|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

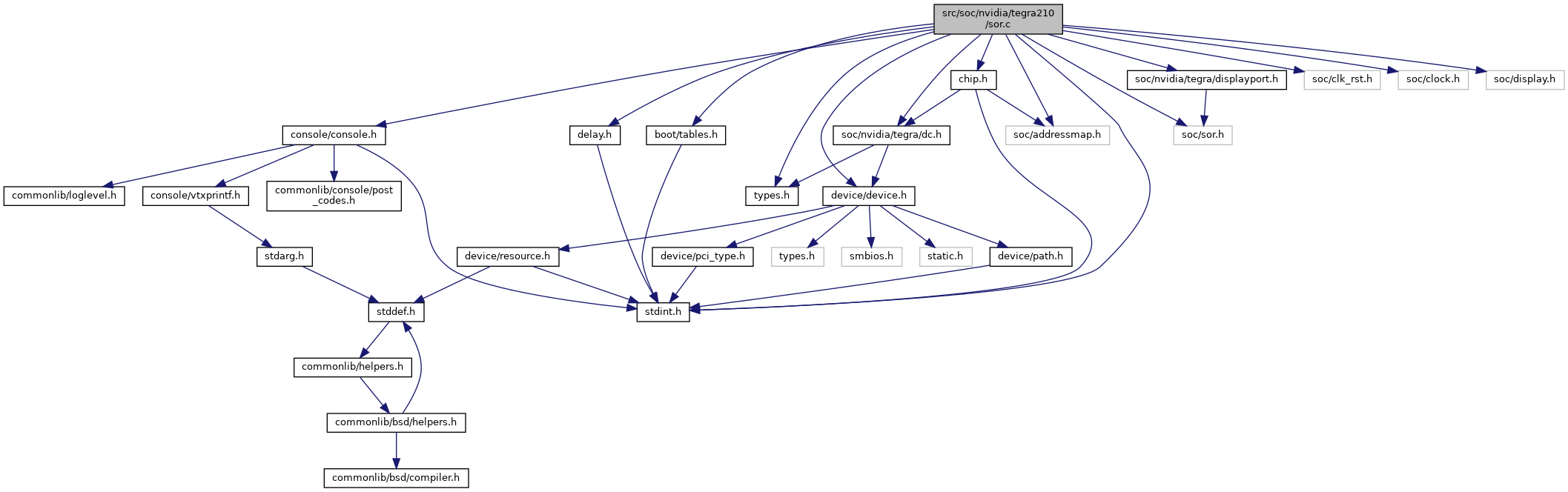

#include <console/console.h>#include <stdint.h>#include <delay.h>#include <soc/addressmap.h>#include <device/device.h>#include <boot/tables.h>#include <soc/nvidia/tegra/dc.h>#include <soc/nvidia/tegra/types.h>#include <soc/sor.h>#include <soc/nvidia/tegra/displayport.h>#include <soc/clk_rst.h>#include <soc/clock.h>#include "chip.h"#include <soc/display.h>

Go to the source code of this file.

Macros | |

| #define | DEBUG_SOR 0 |

| #define | APBDEV_PMC_DPD_SAMPLE (0x20) |

| #define | APBDEV_PMC_DPD_SAMPLE_ON_DISABLE (0) |

| #define | APBDEV_PMC_DPD_SAMPLE_ON_ENABLE (1) |

| #define | APBDEV_PMC_SEL_DPD_TIM (0x1c8) |

| #define | APBDEV_PMC_SEL_DPD_TIM_SEL_DPD_TIM_DEFAULT (0x7f) |

| #define | APBDEV_PMC_IO_DPD2_REQ (0x1c0) |

| #define | APBDEV_PMC_IO_DPD2_REQ_LVDS_SHIFT (25) |

| #define | APBDEV_PMC_IO_DPD2_REQ_LVDS_OFF (0 << 25) |

| #define | APBDEV_PMC_IO_DPD2_REQ_LVDS_ON (1 << 25) |

| #define | APBDEV_PMC_IO_DPD2_REQ_CODE_SHIFT (30) |

| #define | APBDEV_PMC_IO_DPD2_REQ_CODE_DEFAULT_MASK (0x3 << 30) |

| #define | APBDEV_PMC_IO_DPD2_REQ_CODE_IDLE (0 << 30) |

| #define | APBDEV_PMC_IO_DPD2_REQ_CODE_DPD_OFF (1 << 30) |

| #define | APBDEV_PMC_IO_DPD2_REQ_CODE_DPD_ON (2 << 30) |

| #define | APBDEV_PMC_IO_DPD2_STATUS (0x1c4) |

| #define | APBDEV_PMC_IO_DPD2_STATUS_LVDS_SHIFT (25) |

| #define | APBDEV_PMC_IO_DPD2_STATUS_LVDS_OFF (0 << 25) |

| #define | APBDEV_PMC_IO_DPD2_STATUS_LVDS_ON (1 << 25) |

| #define | DC_N_WINDOWS 5 |

Variables | |

| static struct tegra_dc_mode | min_mode |

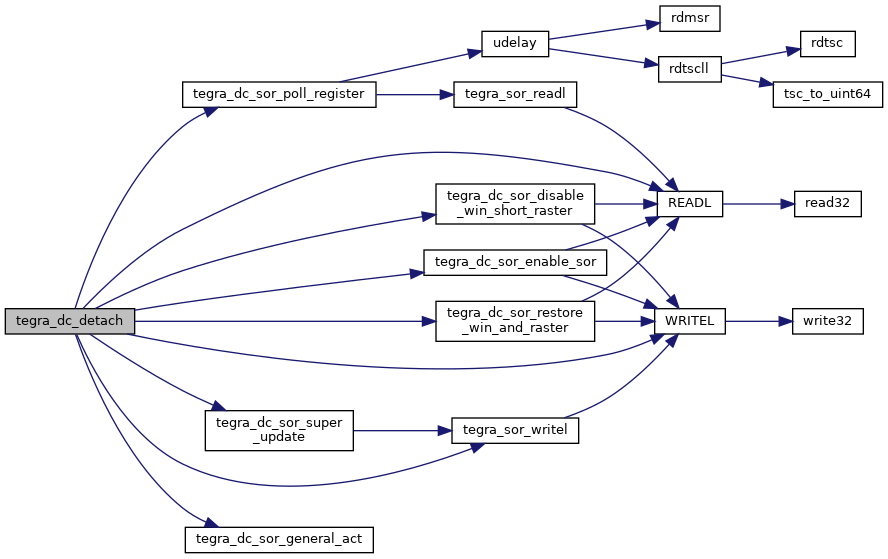

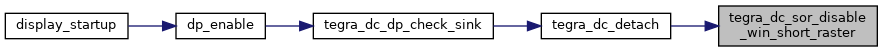

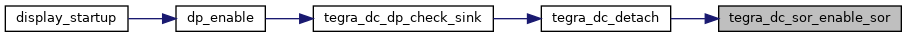

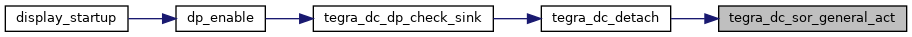

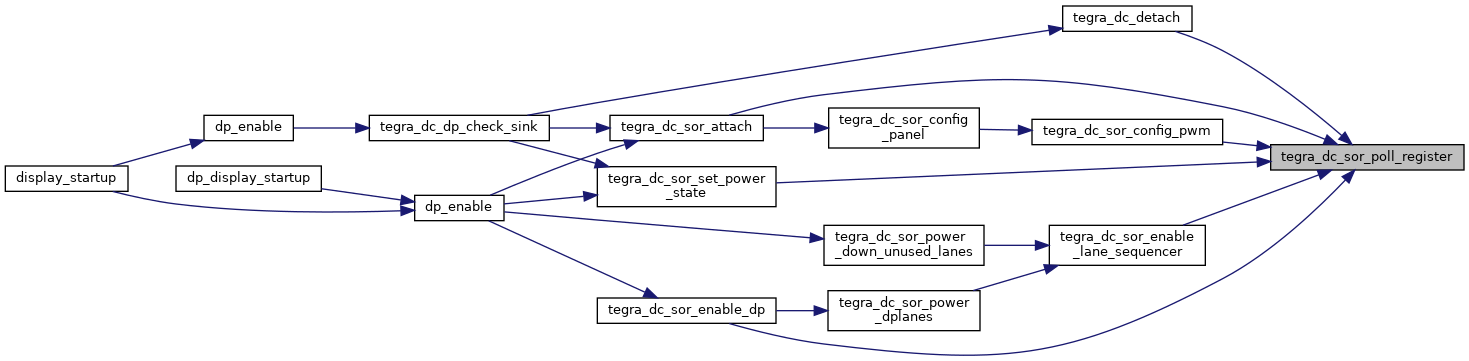

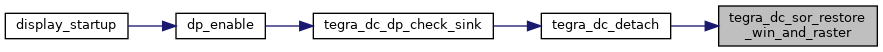

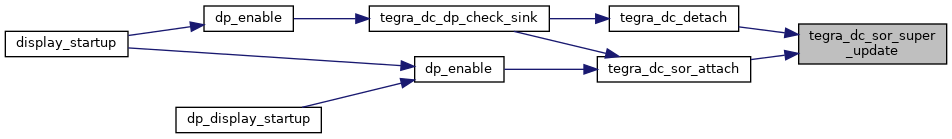

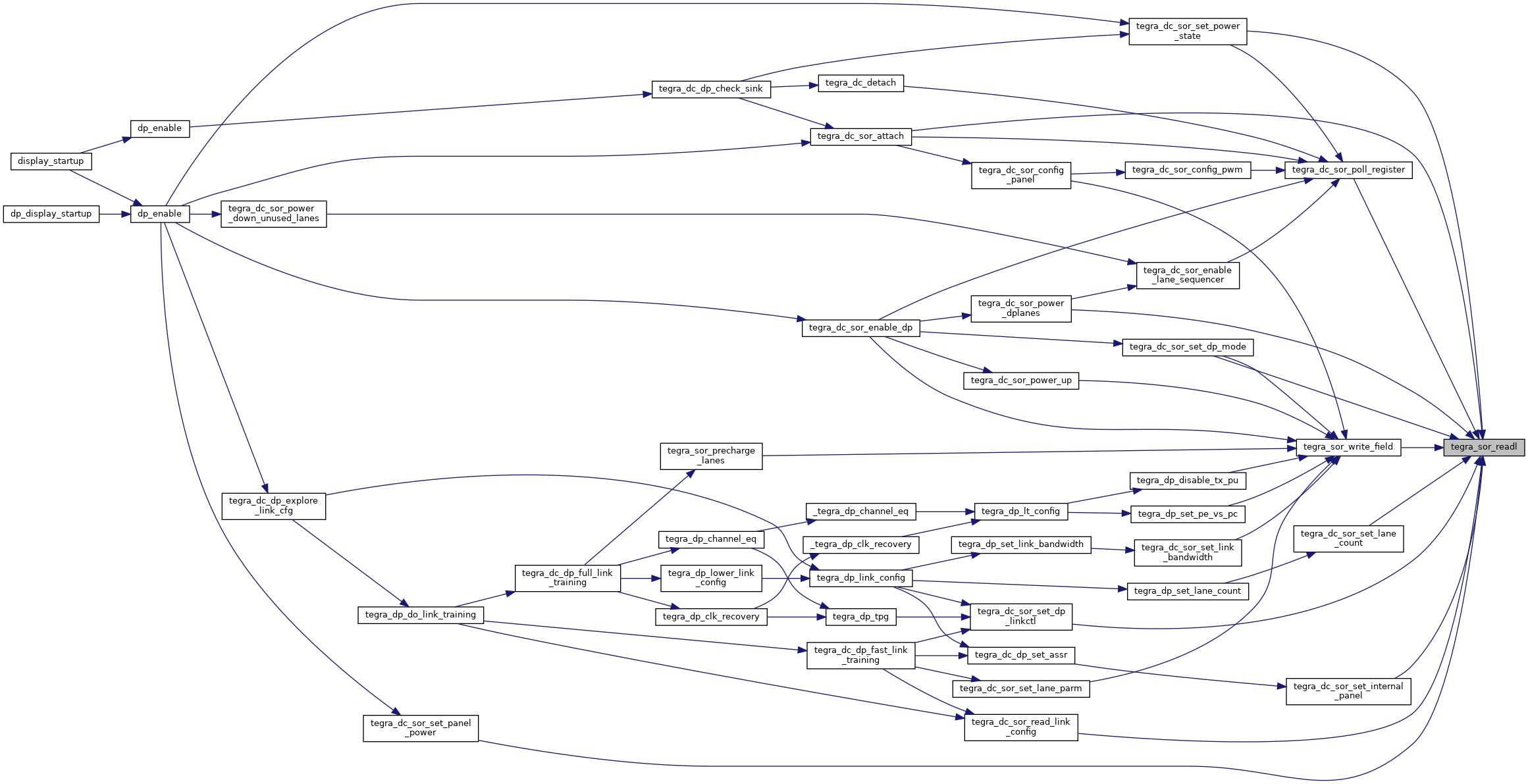

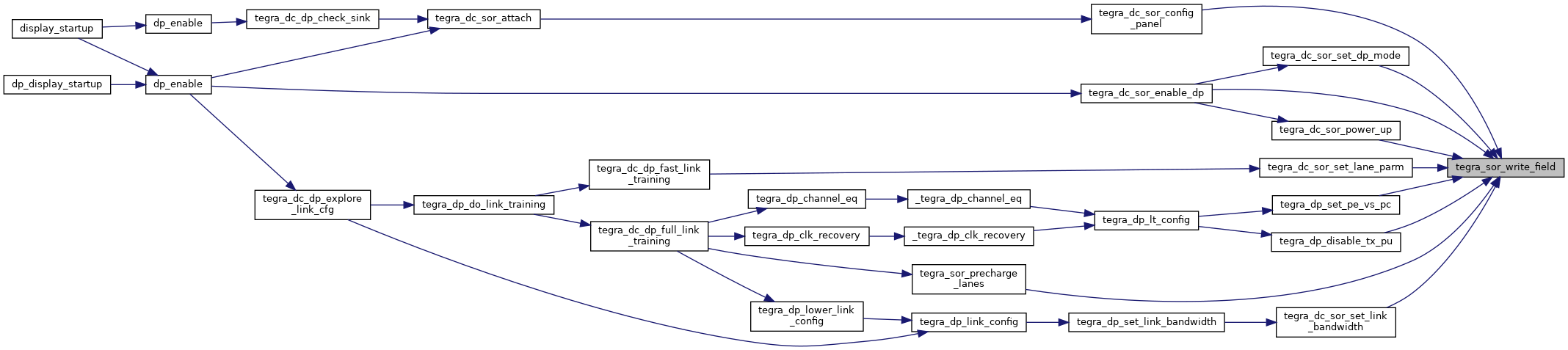

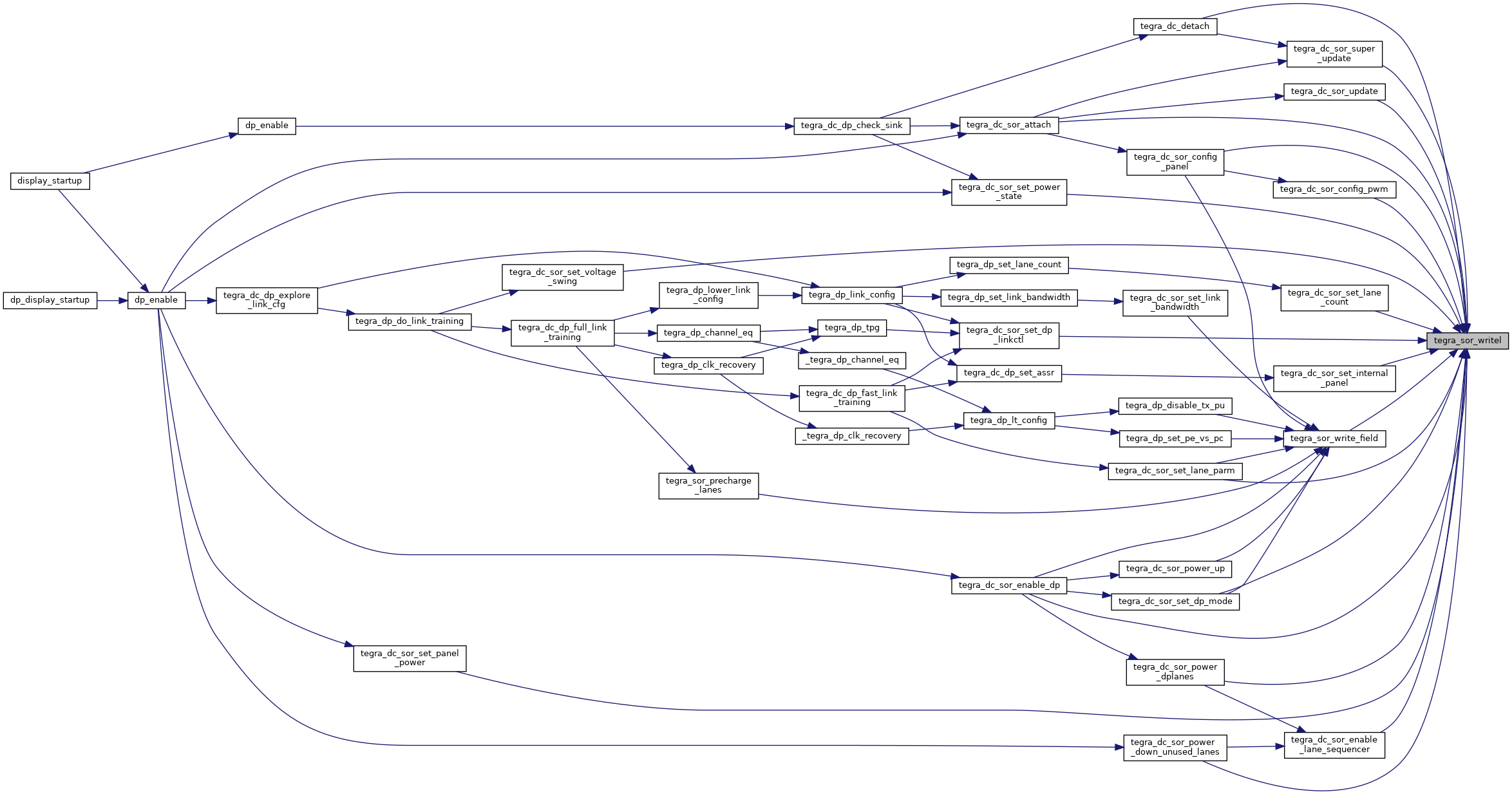

| void tegra_dc_detach | ( | struct tegra_dc_sor_data * | sor | ) |

Definition at line 1039 of file sor.c.

References tegra_dc::base, BIOS_ERR, display_controller::cmd, tegra_dc_sor_data::dc, DC_N_WINDOWS, dc_cmd_reg::disp_cmd, DISP_CTRL_MODE_STOP, dc_cmd_reg::int_mask, NV_SOR_SUPER_STATE1, NV_SOR_SUPER_STATE1_ASY_HEAD_OP_SLEEP, NV_SOR_SUPER_STATE1_ASY_ORMODE_SAFE, NV_SOR_SUPER_STATE1_ATTACHED_NO, NV_SOR_SUPER_STATE1_ATTACHED_YES, NV_SOR_TEST, NV_SOR_TEST_ACT_HEAD_OPMODE_DEFAULT_MASK, NV_SOR_TEST_ACT_HEAD_OPMODE_SLEEP, printk, READL(), tegra_dc_sor_disable_win_short_raster(), tegra_dc_sor_enable_sor(), tegra_dc_sor_general_act(), tegra_dc_sor_poll_register(), tegra_dc_sor_restore_win_and_raster(), tegra_dc_sor_super_update(), TEGRA_SOR_ATTACH_TIMEOUT_MS, tegra_sor_writel(), and WRITEL().

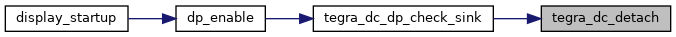

Referenced by tegra_dc_dp_check_sink().

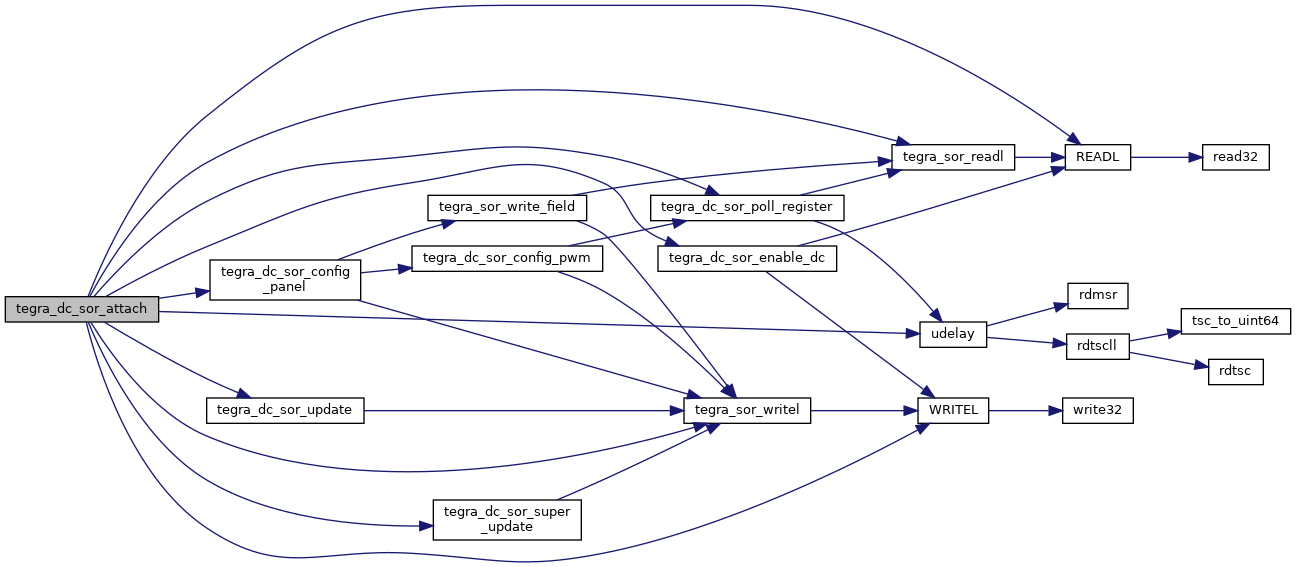

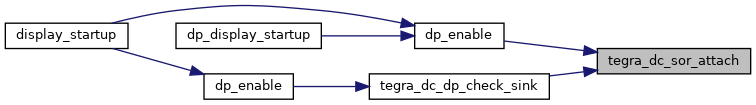

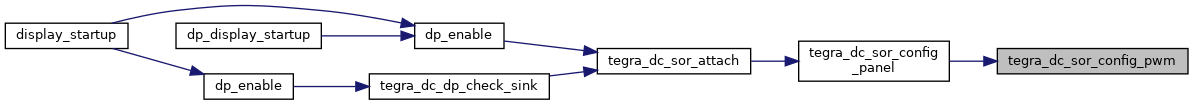

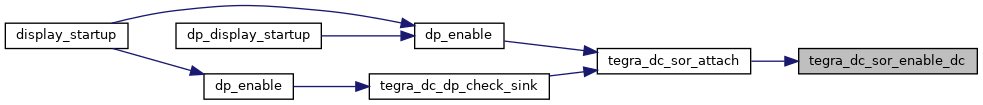

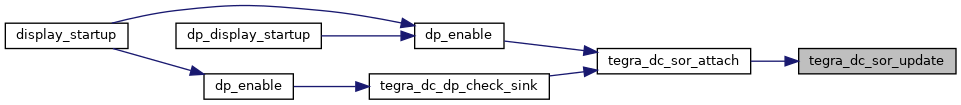

| void tegra_dc_sor_attach | ( | struct tegra_dc_sor_data * | sor | ) |

Definition at line 722 of file sor.c.

References tegra_dc::base, BIOS_ERR, BIOS_INFO, display_controller::cmd, tegra_dc_sor_data::dc, display_controller::disp, dc_cmd_reg::disp_cmd, DISP_CTRL_MODE_C_DISPLAY, dc_cmd_reg::disp_pow_ctrl, dc_disp_reg::disp_win_opt, FRAME_IN_MS, GENERAL_ACT_REQ, NV_SOR_SUPER_STATE1, NV_SOR_SUPER_STATE1_ASY_HEAD_OP_AWAKE, NV_SOR_SUPER_STATE1_ASY_ORMODE_NORMAL, NV_SOR_SUPER_STATE1_ATTACHED_NO, NV_SOR_SUPER_STATE1_ATTACHED_YES, NV_SOR_TEST, NV_SOR_TEST_ACT_HEAD_OPMODE_AWAKE, NV_SOR_TEST_ACT_HEAD_OPMODE_DEFAULT_MASK, NV_SOR_TEST_ATTACHED_TRUE, PM0_ENABLE, PM1_ENABLE, printk, PW0_ENABLE, PW1_ENABLE, PW2_ENABLE, PW3_ENABLE, PW4_ENABLE, READ_MUX_ACTIVE, READL(), SOR_ENABLE, dc_cmd_reg::state_access, dc_cmd_reg::state_ctrl, tegra_dc_sor_config_panel(), tegra_dc_sor_enable_dc(), tegra_dc_sor_poll_register(), tegra_dc_sor_super_update(), tegra_dc_sor_update(), TEGRA_SOR_ATTACH_TIMEOUT_MS, tegra_sor_readl(), tegra_sor_writel(), udelay(), WRITE_MUX_ACTIVE, and WRITEL().

Referenced by dp_enable(), and tegra_dc_dp_check_sink().

|

static |

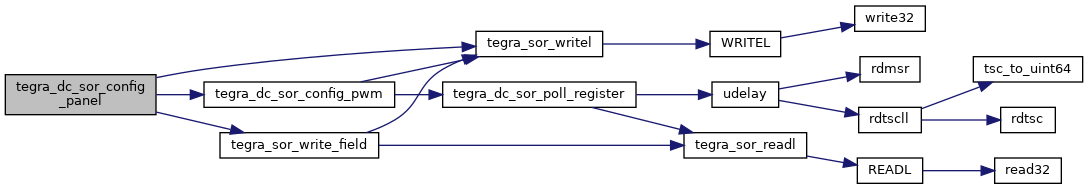

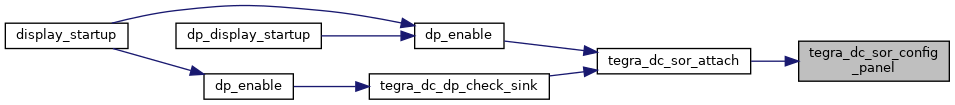

Definition at line 586 of file sor.c.

References tegra_dc_dp_link_config::bits_per_pixel, config, tegra_dc::config, tegra_dc_dp_data::dc, tegra_dc_sor_data::dc, hsync_end, htotal, tegra_dc_dp_data::link_cfg, NV_HEAD_STATE1, NV_HEAD_STATE1_HTOTAL_SHIFT, NV_HEAD_STATE1_VTOTAL_SHIFT, NV_HEAD_STATE2, NV_HEAD_STATE2_HSYNC_END_SHIFT, NV_HEAD_STATE2_VSYNC_END_SHIFT, NV_HEAD_STATE3, NV_HEAD_STATE3_HBLANK_END_SHIFT, NV_HEAD_STATE3_VBLANK_END_SHIFT, NV_HEAD_STATE4, NV_HEAD_STATE4_HBLANK_START_SHIFT, NV_HEAD_STATE4_VBLANK_START_SHIFT, NV_HEAD_STATE5, NV_SOR_CSTM, NV_SOR_CSTM_LVDS_EN_DISABLE, NV_SOR_CSTM_LVDS_EN_ENABLE, NV_SOR_CSTM_ROTCLK_DEFAULT_MASK, NV_SOR_CSTM_ROTCLK_SHIFT, NV_SOR_STATE1, NV_SOR_STATE1_ASY_CRCMODE_COMPLETE_RASTER, NV_SOR_STATE1_ASY_HSYNCPOL_NEGATIVE_TRUE, NV_SOR_STATE1_ASY_OWNER_HEAD0, NV_SOR_STATE1_ASY_PIXELDEPTH_BPP_18_444, NV_SOR_STATE1_ASY_PIXELDEPTH_BPP_24_444, NV_SOR_STATE1_ASY_PROTOCOL_DP_A, NV_SOR_STATE1_ASY_PROTOCOL_LVDS_CUSTOM, NV_SOR_STATE1_ASY_SUBOWNER_NONE, NV_SOR_STATE1_ASY_VSYNCPOL_NEGATIVE_TRUE, tegra_dc::out, tegra_dc_sor_config_pwm(), tegra_sor_write_field(), tegra_sor_writel(), and vtotal.

Referenced by tegra_dc_sor_attach().

|

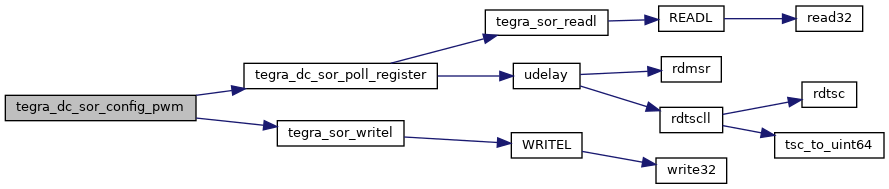

static |

Definition at line 259 of file sor.c.

References BIOS_ERR, NV_SOR_PWM_CTL, NV_SOR_PWM_CTL_DUTY_CYCLE_MASK, NV_SOR_PWM_CTL_SETTING_NEW_DONE, NV_SOR_PWM_CTL_SETTING_NEW_SHIFT, NV_SOR_PWM_CTL_SETTING_NEW_TRIGGER, NV_SOR_PWM_DIV, printk, tegra_dc_sor_poll_register(), TEGRA_SOR_TIMEOUT_MS, and tegra_sor_writel().

Referenced by tegra_dc_sor_config_panel().

|

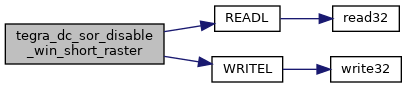

static |

Definition at line 961 of file sor.c.

References dc_disp_reg::back_porch, display_controller::cmd, DC_N_WINDOWS, display_controller::disp, dc_disp_reg::disp_active, dc_cmd_reg::disp_win_header, dc_disp_reg::front_porch, GENERAL_ACT_REQ, tegra_dc_mode::h_active, tegra_dc_mode::h_back_porch, tegra_dc_mode::h_front_porch, tegra_dc_mode::h_ref_to_sync, tegra_dc_mode::h_sync_width, min_mode, READL(), dc_disp_reg::ref_to_sync, dc_cmd_reg::state_ctrl, dc_disp_reg::sync_width, tegra_dc_mode::v_active, tegra_dc_mode::v_back_porch, tegra_dc_mode::v_front_porch, tegra_dc_mode::v_ref_to_sync, tegra_dc_mode::v_sync_width, display_controller::win, WIN_A_ACT_REQ, dc_win_reg::win_opt, WINDOW_A_SELECT, and WRITEL().

Referenced by tegra_dc_detach().

|

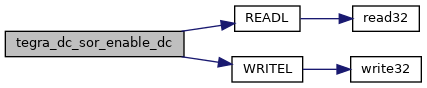

static |

Definition at line 651 of file sor.c.

References tegra_dc::base, display_controller::cmd, tegra_dc_sor_data::dc, display_controller::disp, dc_cmd_reg::disp_cmd, DISP_CTRL_MODE_C_DISPLAY, dc_disp_reg::disp_timing_opt, READL(), dc_cmd_reg::state_access, VSYNC_H_POSITION, WRITE_MUX_ACTIVE, and WRITEL().

Referenced by tegra_dc_sor_attach().

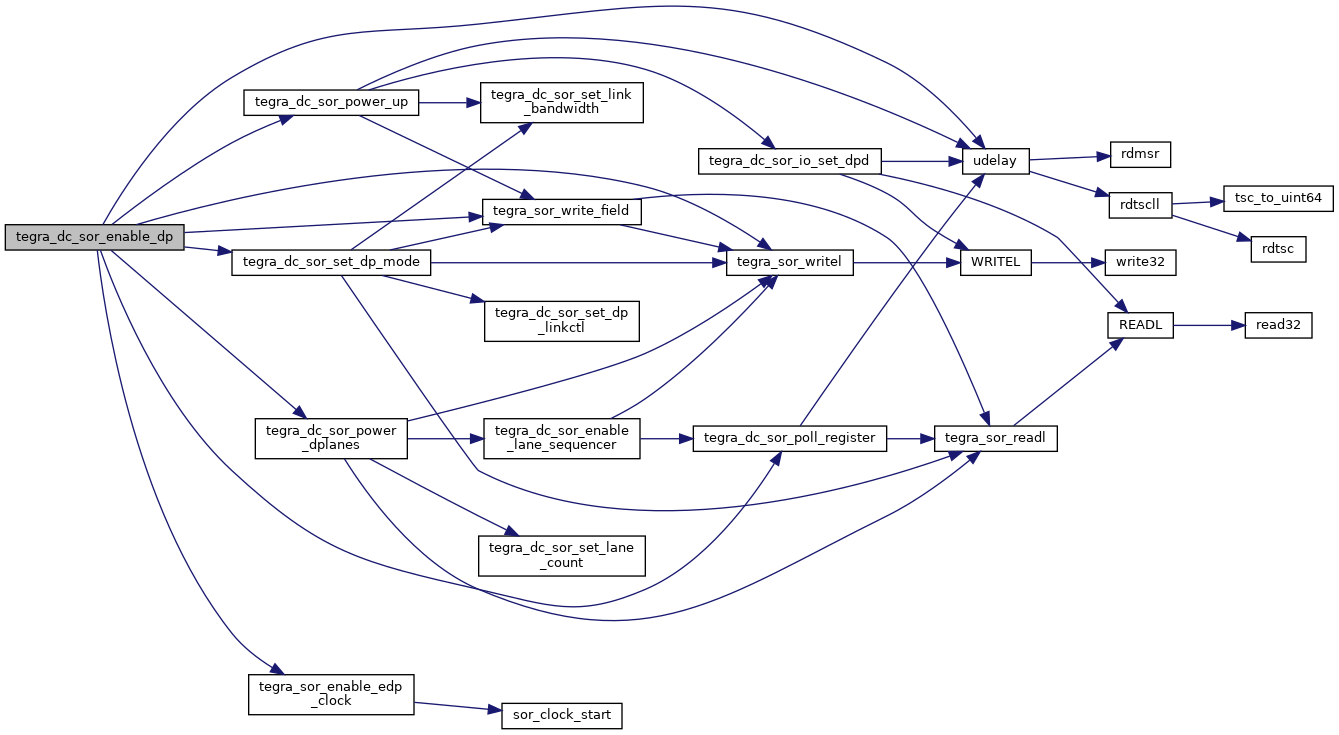

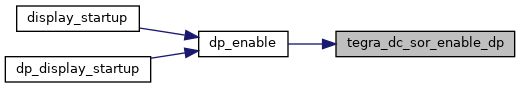

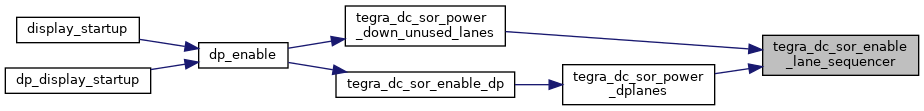

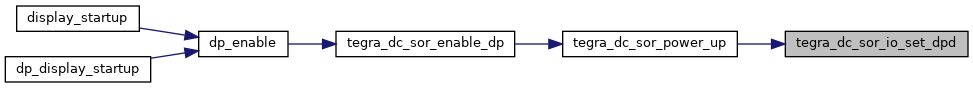

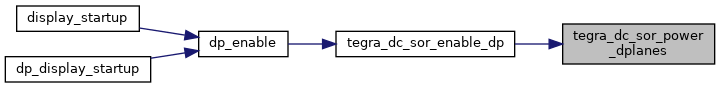

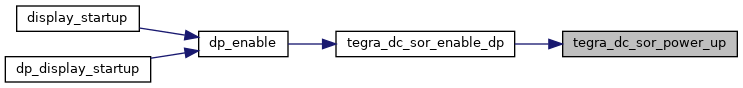

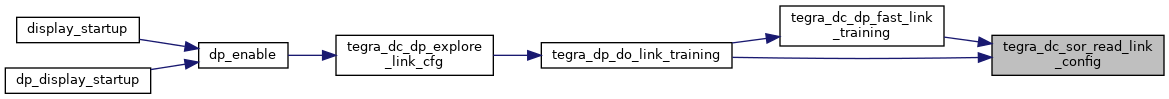

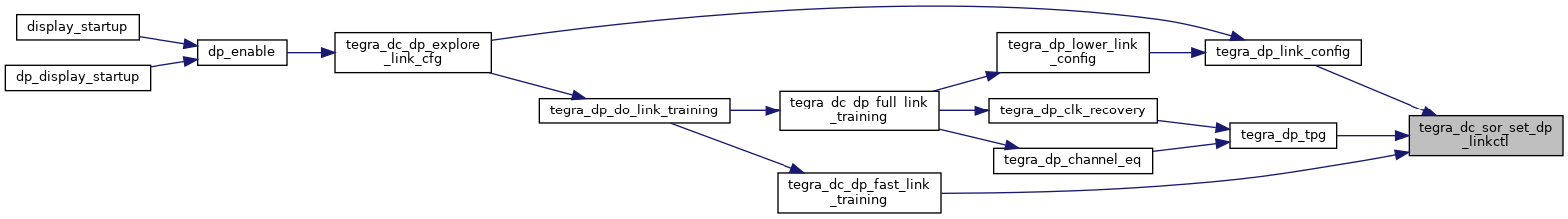

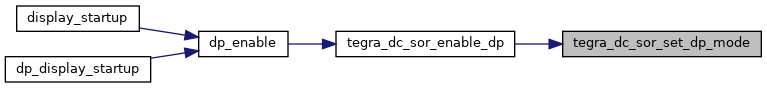

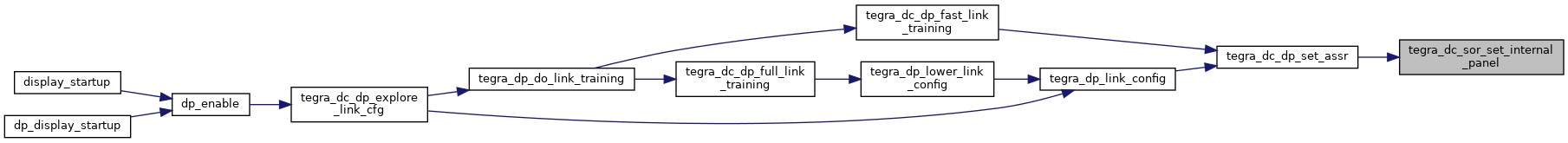

| void tegra_dc_sor_enable_dp | ( | struct tegra_dc_sor_data * | sor | ) |

Definition at line 666 of file sor.c.

References BIOS_ERR, tegra_dc_dp_link_config::lane_count, tegra_dc_sor_data::link_cfg, NV_SOR_CLK_CNTRL, NV_SOR_CLK_CNTRL_DP_CLK_SEL_MASK, NV_SOR_CLK_CNTRL_DP_CLK_SEL_SINGLE_DPCLK, NV_SOR_PLL0, NV_SOR_PLL0_ICHPMP_SHFIT, NV_SOR_PLL0_PLLREG_LEVEL_V45, NV_SOR_PLL0_PWR_ON, NV_SOR_PLL0_RESISTORSEL_EXT, NV_SOR_PLL0_VCOCAP_SHIFT, NV_SOR_PLL0_VCOPD_RESCIND, NV_SOR_PLL1, NV_SOR_PLL1_TERM_COMPOUT_HIGH, NV_SOR_PLL1_TMDS_TERM_ENABLE, NV_SOR_PLL2, NV_SOR_PLL2_AUX1_SEQ_MASK, NV_SOR_PLL2_AUX1_SEQ_PLLCAPPD_OVERRIDE, NV_SOR_PLL2_AUX2_MASK, NV_SOR_PLL2_AUX2_OVERRIDE_POWERDOWN, NV_SOR_PLL2_AUX6_BANDGAP_POWERDOWN_DISABLE, NV_SOR_PLL2_AUX6_BANDGAP_POWERDOWN_MASK, NV_SOR_PLL2_AUX7_PORT_POWERDOWN_DISABLE, NV_SOR_PLL2_AUX7_PORT_POWERDOWN_MASK, NV_SOR_PLL2_AUX8_SEQ_PLLCAPPD_ENFORCE_DISABLE, NV_SOR_PLL2_AUX8_SEQ_PLLCAPPD_ENFORCE_MASK, NV_SOR_PLL2_AUX9_LVDSEN_OVERRIDE, NV_SOR_PLL3, NV_SOR_PLL3_PLLVDD_MODE_MASK, NV_SOR_PLL3_PLLVDD_MODE_V3_3, printk, tegra_dc_sor_poll_register(), tegra_dc_sor_power_dplanes(), tegra_dc_sor_power_up(), tegra_dc_sor_set_dp_mode(), tegra_sor_enable_edp_clock(), TEGRA_SOR_TIMEOUT_MS, tegra_sor_write_field(), tegra_sor_writel(), and udelay().

Referenced by dp_enable().

|

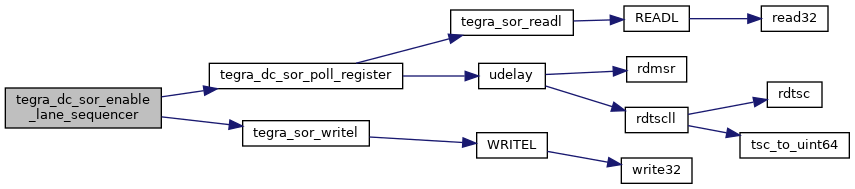

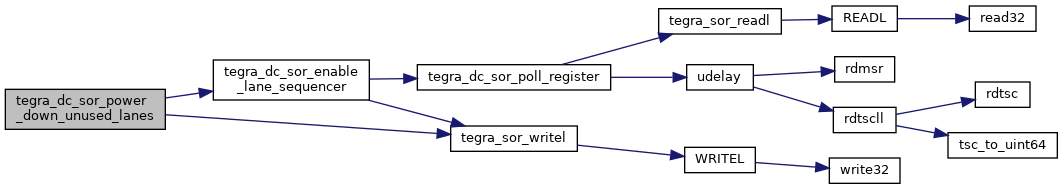

static |

Definition at line 179 of file sor.c.

References BIOS_ERR, NV_SOR_LANE_SEQ_CTL, NV_SOR_LANE_SEQ_CTL_DELAY_SHIFT, NV_SOR_LANE_SEQ_CTL_NEW_POWER_STATE_PD, NV_SOR_LANE_SEQ_CTL_NEW_POWER_STATE_PU, NV_SOR_LANE_SEQ_CTL_SEQUENCE_DOWN, NV_SOR_LANE_SEQ_CTL_SEQUENCE_UP, NV_SOR_LANE_SEQ_CTL_SETTING_MASK, NV_SOR_LANE_SEQ_CTL_SETTING_NEW_DONE, NV_SOR_LANE_SEQ_CTL_SETTING_NEW_TRIGGER, printk, tegra_dc_sor_poll_register(), TEGRA_SOR_TIMEOUT_MS, and tegra_sor_writel().

Referenced by tegra_dc_sor_power_down_unused_lanes(), and tegra_dc_sor_power_dplanes().

|

static |

Definition at line 1030 of file sor.c.

References tegra_dc::base, tegra_dc_sor_data::dc, display_controller::disp, dc_disp_reg::disp_win_opt, READL(), SOR_ENABLE, and WRITEL().

Referenced by tegra_dc_detach().

|

static |

Definition at line 935 of file sor.c.

Referenced by tegra_dc_detach().

|

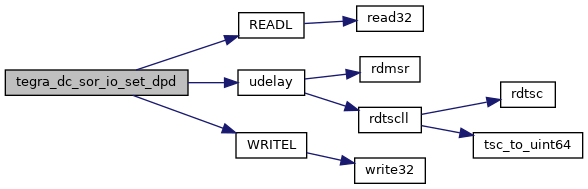

static |

Definition at line 324 of file sor.c.

References APBDEV_PMC_DPD_SAMPLE, APBDEV_PMC_DPD_SAMPLE_ON_DISABLE, APBDEV_PMC_DPD_SAMPLE_ON_ENABLE, APBDEV_PMC_IO_DPD2_REQ, APBDEV_PMC_IO_DPD2_REQ_CODE_DEFAULT_MASK, APBDEV_PMC_IO_DPD2_REQ_CODE_DPD_OFF, APBDEV_PMC_IO_DPD2_REQ_CODE_DPD_ON, APBDEV_PMC_IO_DPD2_REQ_LVDS_OFF, APBDEV_PMC_IO_DPD2_REQ_LVDS_ON, APBDEV_PMC_IO_DPD2_STATUS, APBDEV_PMC_IO_DPD2_STATUS_LVDS_ON, APBDEV_PMC_SEL_DPD_TIM, BIOS_ERR, tegra_dc_sor_data::pmc_base, printk, READL(), udelay(), and WRITEL().

Referenced by tegra_dc_sor_power_up().

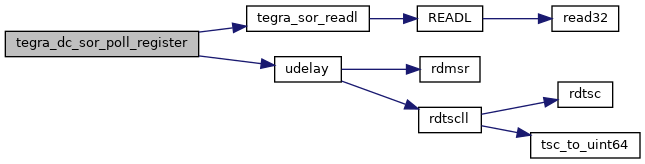

|

static |

Definition at line 90 of file sor.c.

References BIOS_ERR, mask, printk, tegra_sor_readl(), and udelay().

Referenced by tegra_dc_detach(), tegra_dc_sor_attach(), tegra_dc_sor_config_pwm(), tegra_dc_sor_enable_dp(), tegra_dc_sor_enable_lane_sequencer(), and tegra_dc_sor_set_power_state().

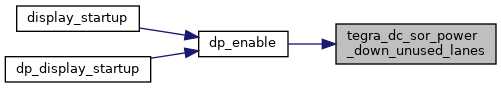

| void tegra_dc_sor_power_down_unused_lanes | ( | struct tegra_dc_sor_data * | sor | ) |

Definition at line 843 of file sor.c.

References BIOS_ERR, tegra_dc_dp_link_config::lane_count, tegra_dc_sor_data::link_cfg, NV_SOR_DP_PADCTL, NV_SOR_DP_PADCTL_PAD_CAL_PD_POWERDOWN, NV_SOR_DP_PADCTL_PD_TXD_0_NO, NV_SOR_DP_PADCTL_PD_TXD_1_NO, NV_SOR_DP_PADCTL_PD_TXD_1_YES, NV_SOR_DP_PADCTL_PD_TXD_2_NO, NV_SOR_DP_PADCTL_PD_TXD_2_YES, NV_SOR_DP_PADCTL_PD_TXD_3_NO, NV_SOR_DP_PADCTL_PD_TXD_3_YES, tegra_dc_sor_data::portnum, printk, tegra_dc_sor_enable_lane_sequencer(), and tegra_sor_writel().

Referenced by dp_enable().

|

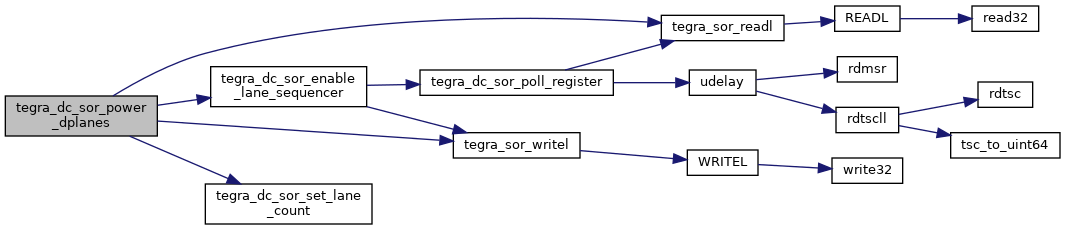

static |

Definition at line 213 of file sor.c.

References BIOS_ERR, NV_SOR_DP_PADCTL, NV_SOR_DP_PADCTL_PD_TXD_0_NO, NV_SOR_DP_PADCTL_PD_TXD_1_NO, NV_SOR_DP_PADCTL_PD_TXD_2_NO, NV_SOR_DP_PADCTL_PD_TXD_3_NO, tegra_dc_sor_data::portnum, printk, tegra_dc_sor_enable_lane_sequencer(), tegra_dc_sor_set_lane_count(), tegra_sor_readl(), and tegra_sor_writel().

Referenced by tegra_dc_sor_enable_dp().

|

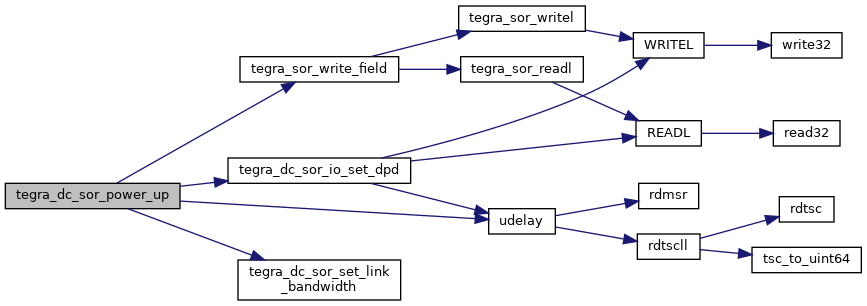

static |

Definition at line 458 of file sor.c.

References NV_SOR_CLK_CNTRL_DP_LINK_SPEED_G1_62, NV_SOR_CLK_CNTRL_DP_LINK_SPEED_LVDS, NV_SOR_DP_PADCTL, NV_SOR_DP_PADCTL_PAD_CAL_PD_POWERDOWN, NV_SOR_DP_PADCTL_PAD_CAL_PD_POWERUP, NV_SOR_PLL0, NV_SOR_PLL0_PWR_MASK, NV_SOR_PLL0_PWR_OFF, NV_SOR_PLL0_PWR_ON, NV_SOR_PLL0_VCOPD_ASSERT, NV_SOR_PLL0_VCOPD_MASK, NV_SOR_PLL0_VCOPD_RESCIND, NV_SOR_PLL2, NV_SOR_PLL2_AUX6_BANDGAP_POWERDOWN_DISABLE, NV_SOR_PLL2_AUX6_BANDGAP_POWERDOWN_ENABLE, NV_SOR_PLL2_AUX6_BANDGAP_POWERDOWN_MASK, NV_SOR_PLL2_AUX7_PORT_POWERDOWN_DISABLE, NV_SOR_PLL2_AUX7_PORT_POWERDOWN_ENABLE, NV_SOR_PLL2_AUX7_PORT_POWERDOWN_MASK, NV_SOR_PLL2_AUX8_SEQ_PLLCAPPD_ENFORCE_DISABLE, NV_SOR_PLL2_AUX8_SEQ_PLLCAPPD_ENFORCE_ENABLE, NV_SOR_PLL2_AUX8_SEQ_PLLCAPPD_ENFORCE_MASK, tegra_dc_sor_data::portnum, tegra_dc_sor_data::power_is_up, tegra_dc_sor_io_set_dpd(), tegra_dc_sor_set_link_bandwidth(), tegra_sor_write_field(), and udelay().

Referenced by tegra_dc_sor_enable_dp().

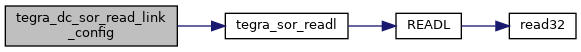

| void tegra_dc_sor_read_link_config | ( | struct tegra_dc_sor_data * | sor, |

| u8 * | link_bw, | ||

| u8 * | lane_count | ||

| ) |

Definition at line 381 of file sor.c.

References BIOS_ERR, NV_SOR_CLK_CNTRL, NV_SOR_CLK_CNTRL_DP_LINK_SPEED_MASK, NV_SOR_CLK_CNTRL_DP_LINK_SPEED_SHIFT, NV_SOR_DP_LINKCTL, NV_SOR_DP_LINKCTL_LANECOUNT_FOUR, NV_SOR_DP_LINKCTL_LANECOUNT_MASK, NV_SOR_DP_LINKCTL_LANECOUNT_ONE, NV_SOR_DP_LINKCTL_LANECOUNT_TWO, NV_SOR_DP_LINKCTL_LANECOUNT_ZERO, tegra_dc_sor_data::portnum, printk, and tegra_sor_readl().

Referenced by tegra_dc_dp_fast_link_training(), and tegra_dp_do_link_training().

|

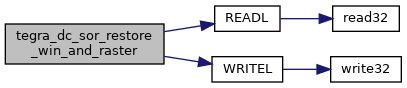

static |

Definition at line 1006 of file sor.c.

References dc_disp_reg::back_porch, display_controller::cmd, DC_N_WINDOWS, display_controller::disp, dc_disp_reg::disp_active, dc_cmd_reg::disp_win_header, dc_disp_reg::front_porch, GENERAL_UPDATE, READL(), dc_disp_reg::ref_to_sync, dc_cmd_reg::state_ctrl, dc_disp_reg::sync_width, display_controller::win, WIN_A_ACT_REQ, dc_win_reg::win_opt, WINDOW_A_SELECT, and WRITEL().

Referenced by tegra_dc_detach().

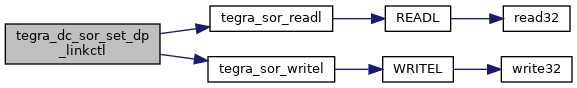

| void tegra_dc_sor_set_dp_linkctl | ( | struct tegra_dc_sor_data * | sor, |

| int | ena, | ||

| u8 | training_pattern, | ||

| const struct tegra_dc_dp_link_config * | link_cfg | ||

| ) |

Definition at line 143 of file sor.c.

References tegra_dc_dp_link_config::enhanced_framing, tegra_dc_dp_link_config::link_bw, NV_SOR_DP_LINKCTL, NV_SOR_DP_LINKCTL_ENABLE_NO, NV_SOR_DP_LINKCTL_ENABLE_YES, NV_SOR_DP_LINKCTL_ENHANCEDFRAME_ENABLE, NV_SOR_DP_LINKCTL_TUSIZE_MASK, NV_SOR_DP_LINKCTL_TUSIZE_SHIFT, NV_SOR_DP_TPG, tegra_dc_sor_data::portnum, SOR_LINK_SPEED_G5_4, tegra_sor_readl(), tegra_sor_writel(), training_pattern_1, training_pattern_2, training_pattern_3, and tegra_dc_dp_link_config::tu_size.

Referenced by tegra_dc_dp_fast_link_training(), tegra_dp_link_config(), and tegra_dp_tpg().

|

static |

Definition at line 276 of file sor.c.

References tegra_dc_dp_link_config::active_count, tegra_dc_dp_link_config::active_frac, tegra_dc_dp_link_config::activepolarity, tegra_dc_dp_link_config::hblank_sym, tegra_dc_dp_link_config::link_bw, NV_SOR_DP_AUDIO_HBLANK_SYMBOLS, NV_SOR_DP_AUDIO_HBLANK_SYMBOLS_MASK, NV_SOR_DP_AUDIO_VBLANK_SYMBOLS, NV_SOR_DP_AUDIO_VBLANK_SYMBOLS_MASK, NV_SOR_DP_CONFIG, NV_SOR_DP_CONFIG_ACTIVESYM_CNTL_ENABLE, NV_SOR_DP_CONFIG_ACTIVESYM_COUNT_MASK, NV_SOR_DP_CONFIG_ACTIVESYM_COUNT_SHIFT, NV_SOR_DP_CONFIG_ACTIVESYM_FRAC_MASK, NV_SOR_DP_CONFIG_ACTIVESYM_FRAC_SHIFT, NV_SOR_DP_CONFIG_ACTIVESYM_POLARITY_POSITIVE, NV_SOR_DP_CONFIG_RD_RESET_VAL_NEGATIVE, NV_SOR_DP_CONFIG_WATERMARK_MASK, tegra_dc_sor_data::portnum, tegra_dc_sor_set_dp_linkctl(), tegra_dc_sor_set_link_bandwidth(), tegra_sor_readl(), tegra_sor_write_field(), tegra_sor_writel(), training_pattern_none, tegra_dc_dp_link_config::vblank_sym, and tegra_dc_dp_link_config::watermark.

Referenced by tegra_dc_sor_enable_dp().

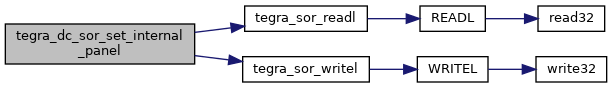

| void tegra_dc_sor_set_internal_panel | ( | struct tegra_dc_sor_data * | sor, |

| int | is_int | ||

| ) |

Definition at line 366 of file sor.c.

References NV_SOR_DP_SPARE, NV_SOR_DP_SPARE_PANEL_INTERNAL, NV_SOR_DP_SPARE_SEQ_ENABLE_YES, NV_SOR_DP_SPARE_SOR_CLK_SEL_MACRO_SORCLK, tegra_dc_sor_data::portnum, tegra_sor_readl(), and tegra_sor_writel().

Referenced by tegra_dc_dp_set_assr().

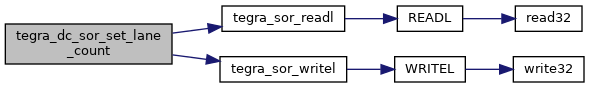

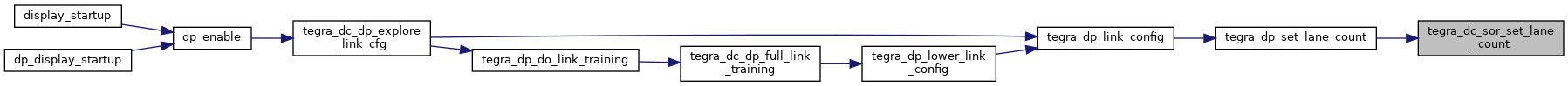

| void tegra_dc_sor_set_lane_count | ( | struct tegra_dc_sor_data * | sor, |

| u8 | lane_count | ||

| ) |

Definition at line 417 of file sor.c.

References BIOS_ERR, NV_SOR_DP_LINKCTL, NV_SOR_DP_LINKCTL_LANECOUNT_FOUR, NV_SOR_DP_LINKCTL_LANECOUNT_MASK, NV_SOR_DP_LINKCTL_LANECOUNT_ONE, NV_SOR_DP_LINKCTL_LANECOUNT_TWO, tegra_dc_sor_data::portnum, printk, tegra_sor_readl(), and tegra_sor_writel().

Referenced by tegra_dp_set_lane_count().

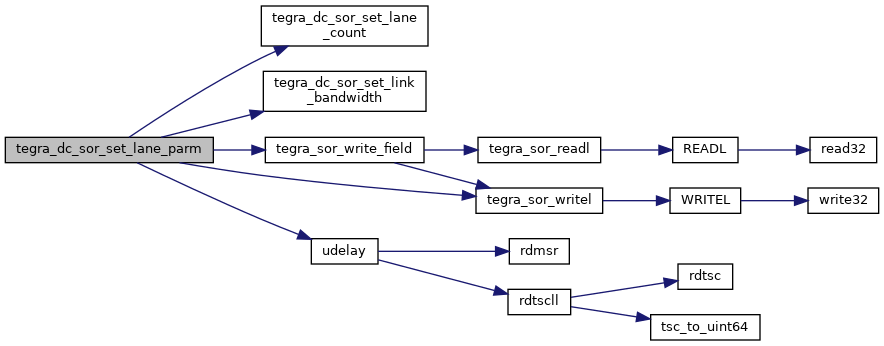

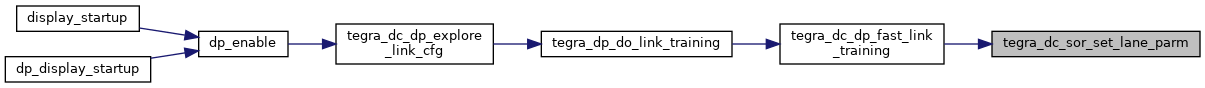

| void tegra_dc_sor_set_lane_parm | ( | struct tegra_dc_sor_data * | sor, |

| const struct tegra_dc_dp_link_config * | link_cfg | ||

| ) |

Definition at line 788 of file sor.c.

References tegra_dc_dp_link_config::drive_current, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_link_config::link_bw, NV_SOR_DP_PADCTL, NV_SOR_DP_PADCTL_TX_PU_ENABLE, NV_SOR_DP_PADCTL_TX_PU_VALUE_DEFAULT_MASK, NV_SOR_DP_PADCTL_TX_PU_VALUE_SHIFT, NV_SOR_LANE_DRIVE_CURRENT, NV_SOR_LVDS, NV_SOR_POSTCURSOR, NV_SOR_PR, tegra_dc_sor_data::portnum, tegra_dc_dp_link_config::postcursor, tegra_dc_dp_link_config::preemphasis, tegra_dc_sor_set_lane_count(), tegra_dc_sor_set_link_bandwidth(), tegra_sor_write_field(), tegra_sor_writel(), and udelay().

Referenced by tegra_dc_dp_fast_link_training().

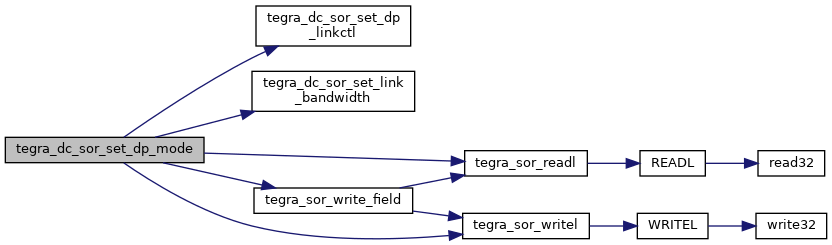

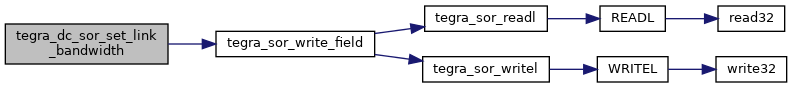

| void tegra_dc_sor_set_link_bandwidth | ( | struct tegra_dc_sor_data * | sor, |

| u8 | link_bw | ||

| ) |

Definition at line 410 of file sor.c.

References NV_SOR_CLK_CNTRL, NV_SOR_CLK_CNTRL_DP_LINK_SPEED_MASK, NV_SOR_CLK_CNTRL_DP_LINK_SPEED_SHIFT, and tegra_sor_write_field().

Referenced by tegra_dp_set_link_bandwidth().

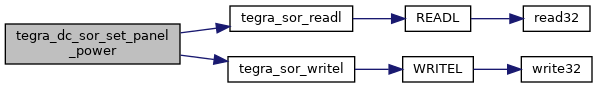

| void tegra_dc_sor_set_panel_power | ( | struct tegra_dc_sor_data * | sor, |

| int | power_up | ||

| ) |

Definition at line 244 of file sor.c.

References NV_SOR_DP_PADCTL, NV_SOR_DP_PADCTL_PAD_CAL_PD_POWERDOWN, NV_SOR_DP_PADCTL_PAD_CAL_PD_POWERUP, tegra_dc_sor_data::portnum, tegra_sor_readl(), and tegra_sor_writel().

Referenced by dp_enable().

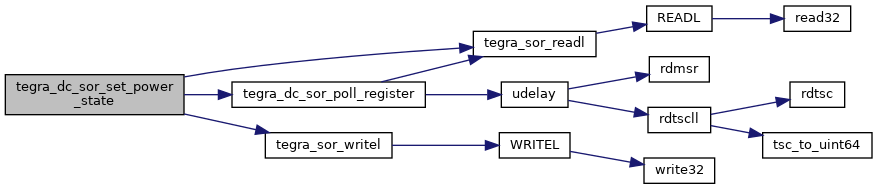

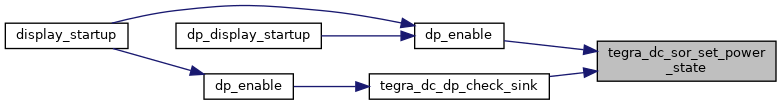

| int tegra_dc_sor_set_power_state | ( | struct tegra_dc_sor_data * | sor, |

| int | pu_pd | ||

| ) |

Definition at line 115 of file sor.c.

References BIOS_ERR, EFAULT, NV_SOR_PWR, NV_SOR_PWR_NORMAL_STATE_PD, NV_SOR_PWR_NORMAL_STATE_PU, NV_SOR_PWR_SETTING_NEW_DEFAULT_MASK, NV_SOR_PWR_SETTING_NEW_DONE, NV_SOR_PWR_SETTING_NEW_TRIGGER, printk, tegra_dc_sor_poll_register(), tegra_sor_readl(), TEGRA_SOR_TIMEOUT_MS, and tegra_sor_writel().

Referenced by dp_enable(), and tegra_dc_dp_check_sink().

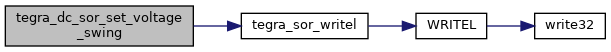

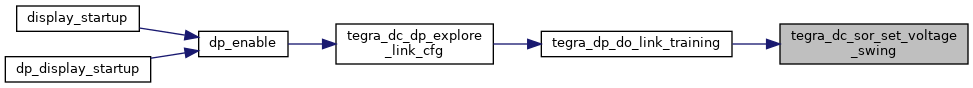

| void tegra_dc_sor_set_voltage_swing | ( | struct tegra_dc_sor_data * | sor | ) |

Definition at line 817 of file sor.c.

References BIOS_WARNING, tegra_dc_dp_link_config::link_bw, tegra_dc_sor_data::link_cfg, NV_SOR_LANE_DRIVE_CURRENT, NV_SOR_PR, tegra_dc_sor_data::portnum, printk, SOR_LINK_SPEED_G1_62, SOR_LINK_SPEED_G2_7, SOR_LINK_SPEED_G5_4, and tegra_sor_writel().

Referenced by tegra_dp_do_link_training().

|

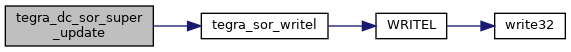

inlinestatic |

Definition at line 310 of file sor.c.

References NV_SOR_SUPER_STATE0, and tegra_sor_writel().

Referenced by tegra_dc_detach(), and tegra_dc_sor_attach().

|

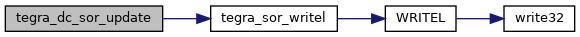

inlinestatic |

Definition at line 317 of file sor.c.

References NV_SOR_STATE0, and tegra_sor_writel().

Referenced by tegra_dc_sor_attach().

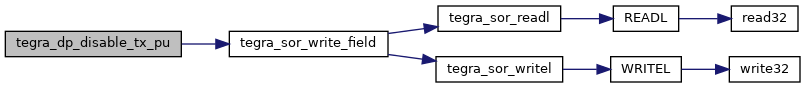

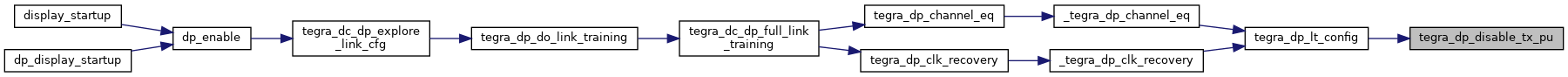

| void tegra_dp_disable_tx_pu | ( | struct tegra_dc_sor_data * | sor | ) |

Definition at line 68 of file sor.c.

References NV_SOR_DP_PADCTL, NV_SOR_DP_PADCTL_TX_PU_DISABLE, NV_SOR_DP_PADCTL_TX_PU_MASK, tegra_dc_sor_data::portnum, and tegra_sor_write_field().

Referenced by tegra_dp_lt_config().

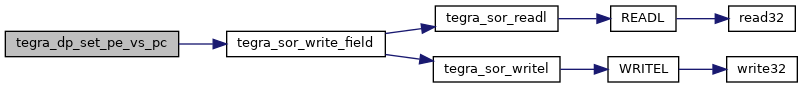

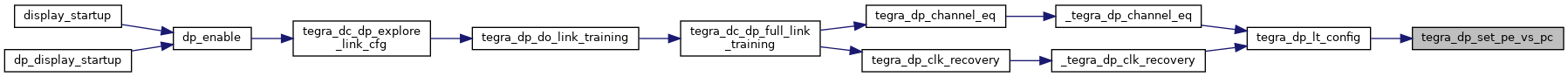

| void tegra_dp_set_pe_vs_pc | ( | struct tegra_dc_sor_data * | sor, |

| u32 | mask, | ||

| u32 | pe_reg, | ||

| u32 | vs_reg, | ||

| u32 | pc_reg, | ||

| u8 | pc_supported | ||

| ) |

Definition at line 76 of file sor.c.

References mask, NV_SOR_DC, NV_SOR_POSTCURSOR, NV_SOR_PR, tegra_dc_sor_data::portnum, and tegra_sor_write_field().

Referenced by tegra_dp_lt_config().

|

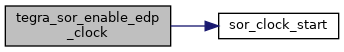

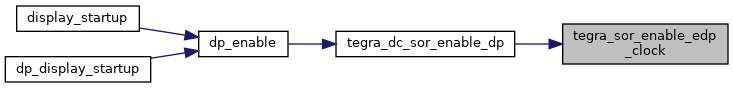

static |

Definition at line 444 of file sor.c.

References sor_clock_start().

Referenced by tegra_dc_sor_enable_dp().

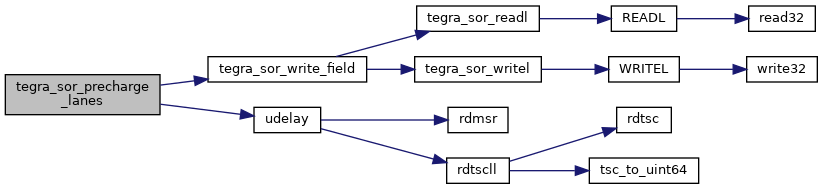

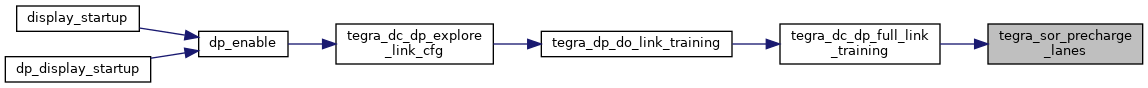

| void tegra_sor_precharge_lanes | ( | struct tegra_dc_sor_data * | sor | ) |

Definition at line 884 of file sor.c.

References __fallthrough, BIOS_ERR, tegra_dc_dp_link_config::lane_count, tegra_dc_sor_data::link_cfg, NV_SOR_DP_PADCTL, NV_SOR_DP_PADCTL_COMODE_TXD_0_DP_TXD_2_SHIFT, NV_SOR_DP_PADCTL_PD_TXD_0_NO, NV_SOR_DP_PADCTL_PD_TXD_1_NO, NV_SOR_DP_PADCTL_PD_TXD_2_NO, NV_SOR_DP_PADCTL_PD_TXD_3_NO, tegra_dc_sor_data::portnum, printk, tegra_sor_write_field(), udelay(), and val.

Referenced by tegra_dc_dp_full_link_training().

|

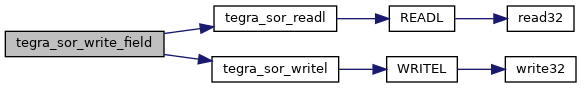

inlinestatic |

Definition at line 45 of file sor.c.

References addr, tegra_dc_sor_data::base, and READL().

Referenced by tegra_dc_sor_attach(), tegra_dc_sor_poll_register(), tegra_dc_sor_power_dplanes(), tegra_dc_sor_read_link_config(), tegra_dc_sor_set_dp_linkctl(), tegra_dc_sor_set_dp_mode(), tegra_dc_sor_set_internal_panel(), tegra_dc_sor_set_lane_count(), tegra_dc_sor_set_panel_power(), tegra_dc_sor_set_power_state(), and tegra_sor_write_field().

|

inlinestatic |

Definition at line 59 of file sor.c.

References mask, tegra_sor_readl(), tegra_sor_writel(), and val.

Referenced by tegra_dc_sor_config_panel(), tegra_dc_sor_enable_dp(), tegra_dc_sor_power_up(), tegra_dc_sor_set_dp_mode(), tegra_dc_sor_set_lane_parm(), tegra_dc_sor_set_link_bandwidth(), tegra_dp_disable_tx_pu(), tegra_dp_set_pe_vs_pc(), and tegra_sor_precharge_lanes().

|

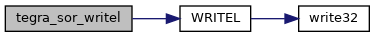

inlinestatic |

Definition at line 52 of file sor.c.

References addr, tegra_dc_sor_data::base, val, and WRITEL().

Referenced by tegra_dc_detach(), tegra_dc_sor_attach(), tegra_dc_sor_config_panel(), tegra_dc_sor_config_pwm(), tegra_dc_sor_enable_dp(), tegra_dc_sor_enable_lane_sequencer(), tegra_dc_sor_power_down_unused_lanes(), tegra_dc_sor_power_dplanes(), tegra_dc_sor_set_dp_linkctl(), tegra_dc_sor_set_dp_mode(), tegra_dc_sor_set_internal_panel(), tegra_dc_sor_set_lane_count(), tegra_dc_sor_set_lane_parm(), tegra_dc_sor_set_panel_power(), tegra_dc_sor_set_power_state(), tegra_dc_sor_set_voltage_swing(), tegra_dc_sor_super_update(), tegra_dc_sor_update(), and tegra_sor_write_field().

|

static |

Definition at line 935 of file sor.c.

Referenced by tegra_dc_sor_disable_win_short_raster().