|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

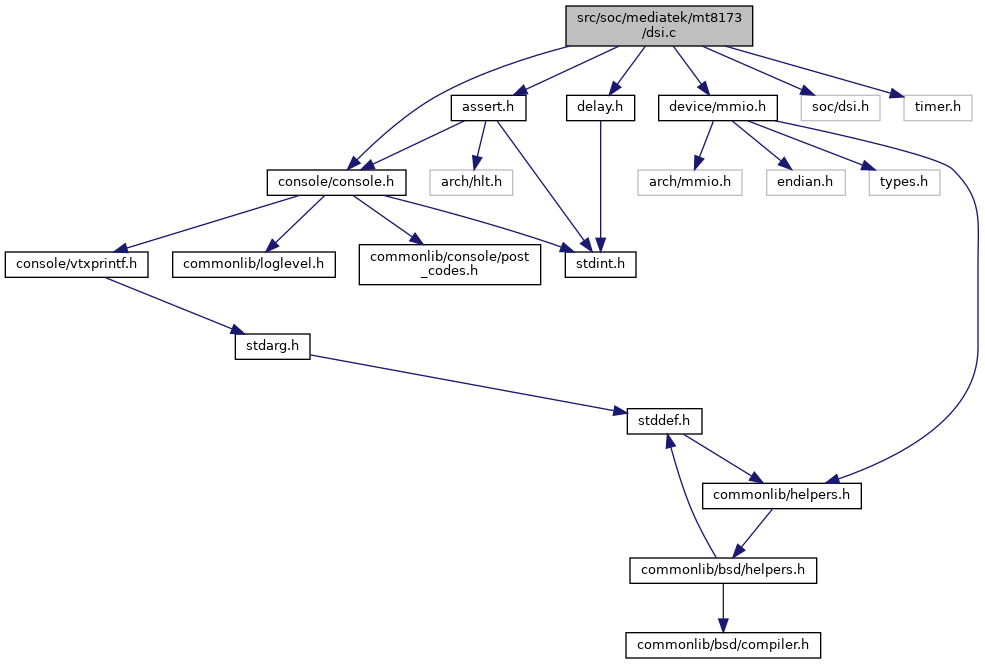

#include <assert.h>#include <device/mmio.h>#include <console/console.h>#include <delay.h>#include <soc/dsi.h>#include <timer.h>

Go to the source code of this file.

Functions | |

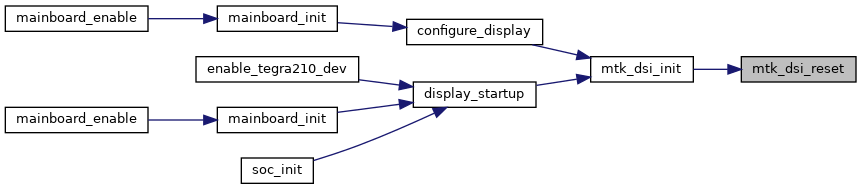

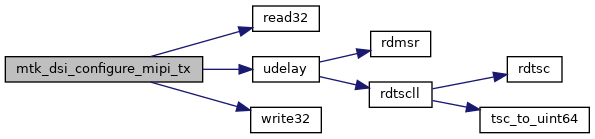

| void | mtk_dsi_configure_mipi_tx (u32 data_rate, u32 lanes) |

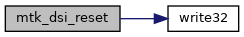

| void | mtk_dsi_reset (void) |

| void | mtk_dsi_override_phy_timing (struct mtk_phy_timing *timing) |

| void | mtk_dsi_pin_drv_ctrl (void) |

PLL PCW config PCW bit 24~30 = integer part of pcw PCW bit 0~23 = fractional part of pcw pcw = data_Rate*4*txdiv/(Ref_clk*2); Post DIV =4, so need data_Rate*4 Ref_clk is 26MHz

Definition at line 10 of file dsi.c.

References AD_DSI_PLL_SDM_ISO_EN, AD_DSI_PLL_SDM_PWR_ON, assert, BIT, mipi_tx_regs::ck_ckmode_en, mipi_tx_regs::ck_sw_ctl_en, CLK26M_HZ, clrbits32, clrsetbits32, mipi_tx_regs::d0_sw_ctl_en, mipi_tx_regs::d1_sw_ctl_en, mipi_tx_regs::d2_sw_ctl_en, mipi_tx_regs::d3_sw_ctl_en, mipi_tx_regs::dsi_bg_con, DSI_CK_CKMODE_EN, mipi_tx_regs::dsi_clock_lane, mipi_tx_regs::dsi_con, mipi_tx_regs::dsi_data_lane, mipi_tx_regs::dsi_pll_con0, mipi_tx_regs::dsi_pll_con1, mipi_tx_regs::dsi_pll_con2, mipi_tx_regs::dsi_pll_pwr, DSI_SW_CTL_EN, mipi_tx_regs::dsi_top_con, mipi_tx_regs::lane_con, LDOOUT_EN, MHz, mipi_tx, mipi_tx0, MTK_DSI_DATA_RATE_MIN_MHZ, mipi_tx_regs::pll_con0, mipi_tx_regs::pll_con1, mipi_tx_regs::pll_con4, mipi_tx_regs::pll_pwr, read32(), RG_DSI0_CKG_LDOOUT_EN, RG_DSI0_LDOCORE_EN, RG_DSI0_MPPLL_PLL_EN, RG_DSI0_MPPLL_PREDIV, RG_DSI0_MPPLL_SDM_FRA_EN, RG_DSI0_MPPLL_SDM_SSC_EN, RG_DSI0_MPPLL_TXDIV0, RG_DSI0_MPPLL_TXDIV1, RG_DSI_BG_CKEN, RG_DSI_BG_CORE_EN, RG_DSI_LNT_HS_BIAS_EN, RG_DSI_LNT_IMP_CAL_CODE, RG_DSI_MPPLL_SDM_ISO_EN, RG_DSI_MPPLL_SDM_PWR_ON, RG_DSI_PAD_TIE_LOW_EN, RG_DSI_PLL_EN, RG_DSI_PLL_POSDIV, RG_DSI_V02_SEL, RG_DSI_V032_SEL, RG_DSI_V04_SEL, RG_DSI_V072_SEL, RG_DSI_V10_SEL, RG_DSI_V12_SEL, setbits32, udelay(), and write32().

Referenced by mtk_dsi_init().

| void mtk_dsi_override_phy_timing | ( | struct mtk_phy_timing * | timing | ) |

Definition at line 97 of file dsi.c.

References mtk_phy_timing::clk_hs_exit, mtk_phy_timing::d_phy, mtk_phy_timing::da_hs_exit, mtk_phy_timing::da_hs_prepare, mtk_phy_timing::da_hs_sync, mtk_phy_timing::da_hs_trail, mtk_phy_timing::da_hs_zero, mtk_phy_timing::lpx, mtk_phy_timing::ta_get, mtk_phy_timing::ta_go, and mtk_phy_timing::ta_sure.

Definition at line 116 of file dsi.c.

References BIOS_ERR, clrbits32, lvds_tx1, printk, read32(), RG_AD_LVDSTX_PWR_ACK, RG_DA_LVDS_ISO_EN, RG_DA_LVDSTX_PWR_ON, setbits32, stopwatch_expired(), stopwatch_init_usecs_expire(), and lvds_tx1_regs::vopll_ctl3.

Referenced by mainboard_init().

Definition at line 91 of file dsi.c.

References clrbits32, dsi0, dsi_regs::dsi_con_ctrl, dsi_regs::dsi_force_commit, DSI_FORCE_COMMIT_ALWAYS, DSI_FORCE_COMMIT_USE_MMSYS, setbits32, and write32().

Referenced by mtk_dsi_init().