|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

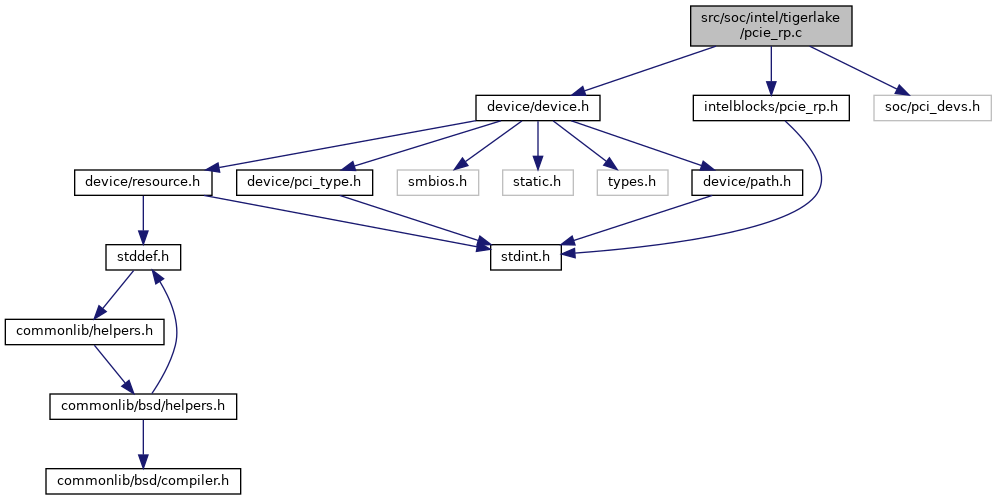

Go to the source code of this file.

Macros | |

| #define | CPU_CPIE_VW_IDX_BASE 24 |

Functions | |

| static bool | is_part_of_group (const struct device *dev, const struct pcie_rp_group *groups) |

| const struct pcie_rp_group * | soc_get_pch_rp_groups (void) |

| enum pcie_rp_type | soc_get_pcie_rp_type (const struct device *dev) |

| int | soc_get_cpu_rp_vw_idx (const struct device *dev) |

Variables | |

| static const struct pcie_rp_group | pch_lp_rp_groups [] |

| static const struct pcie_rp_group | pch_h_rp_groups [] |

| static const struct pcie_rp_group | cpu_rp_groups [] |

|

static |

Definition at line 28 of file pcie_rp.c.

References pcie_rp_group::count, pci_path::devfn, DEVICE_PATH_PCI, device::path, device_path::pci, PCI_FUNC, PCI_SLOT, rp_start_fn(), pcie_rp_group::slot, and device_path::type.

| int soc_get_cpu_rp_vw_idx | ( | const struct device * | dev | ) |

Definition at line 71 of file pcie_rp.c.

References CPU_CPIE_VW_IDX_BASE, pci_path::devfn, DEVICE_PATH_PCI, device::path, device_path::pci, SA_DEVFN_CPU_PCIE, SA_DEVFN_PEG1, SA_DEVFN_PEG2, SA_DEVFN_PEG3, and device_path::type.

| const struct pcie_rp_group* soc_get_pch_rp_groups | ( | void | ) |

Definition at line 50 of file pcie_rp.c.

References CONFIG, pch_h_rp_groups, and pch_lp_rp_groups.

Referenced by soc_init_pre_device().

| enum pcie_rp_type soc_get_pcie_rp_type | ( | const struct device * | dev | ) |

|

static |

|

static |

Definition at line 1 of file pcie_rp.c.

Referenced by soc_get_pch_rp_groups().

|

static |

Definition at line 1 of file pcie_rp.c.

Referenced by soc_get_pch_rp_groups().