|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

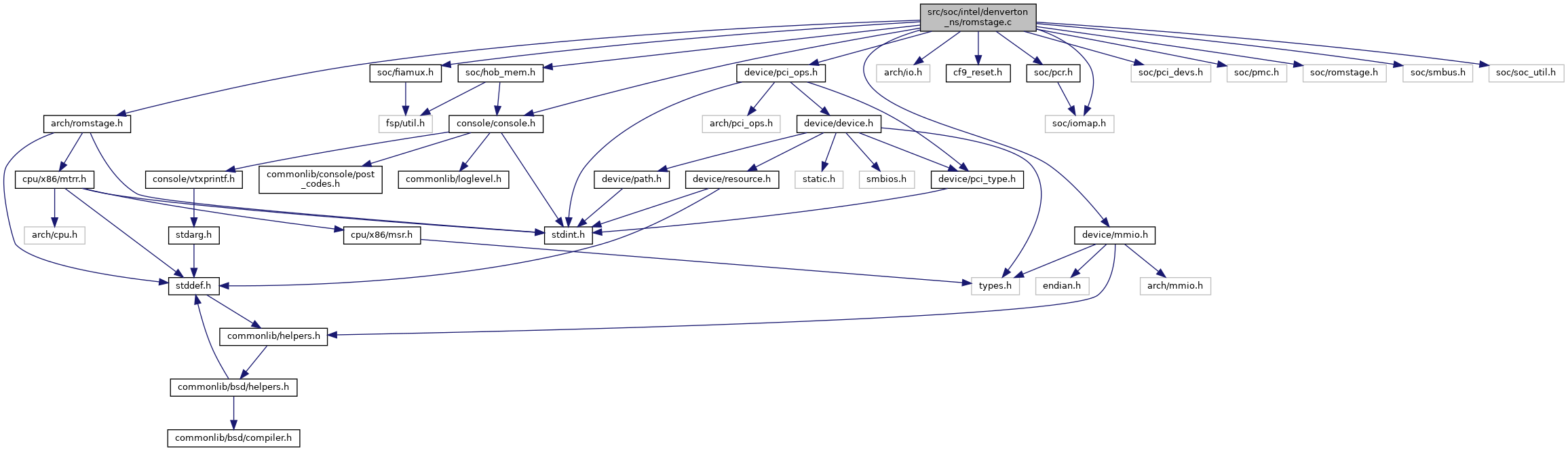

#include <arch/romstage.h>#include <arch/io.h>#include <cf9_reset.h>#include <console/console.h>#include <device/pci_ops.h>#include <soc/fiamux.h>#include <device/mmio.h>#include <soc/iomap.h>#include <soc/pci_devs.h>#include <soc/pcr.h>#include <soc/pmc.h>#include <soc/romstage.h>#include <soc/smbus.h>#include <soc/soc_util.h>#include <soc/hob_mem.h>

Go to the source code of this file.

Functions | |

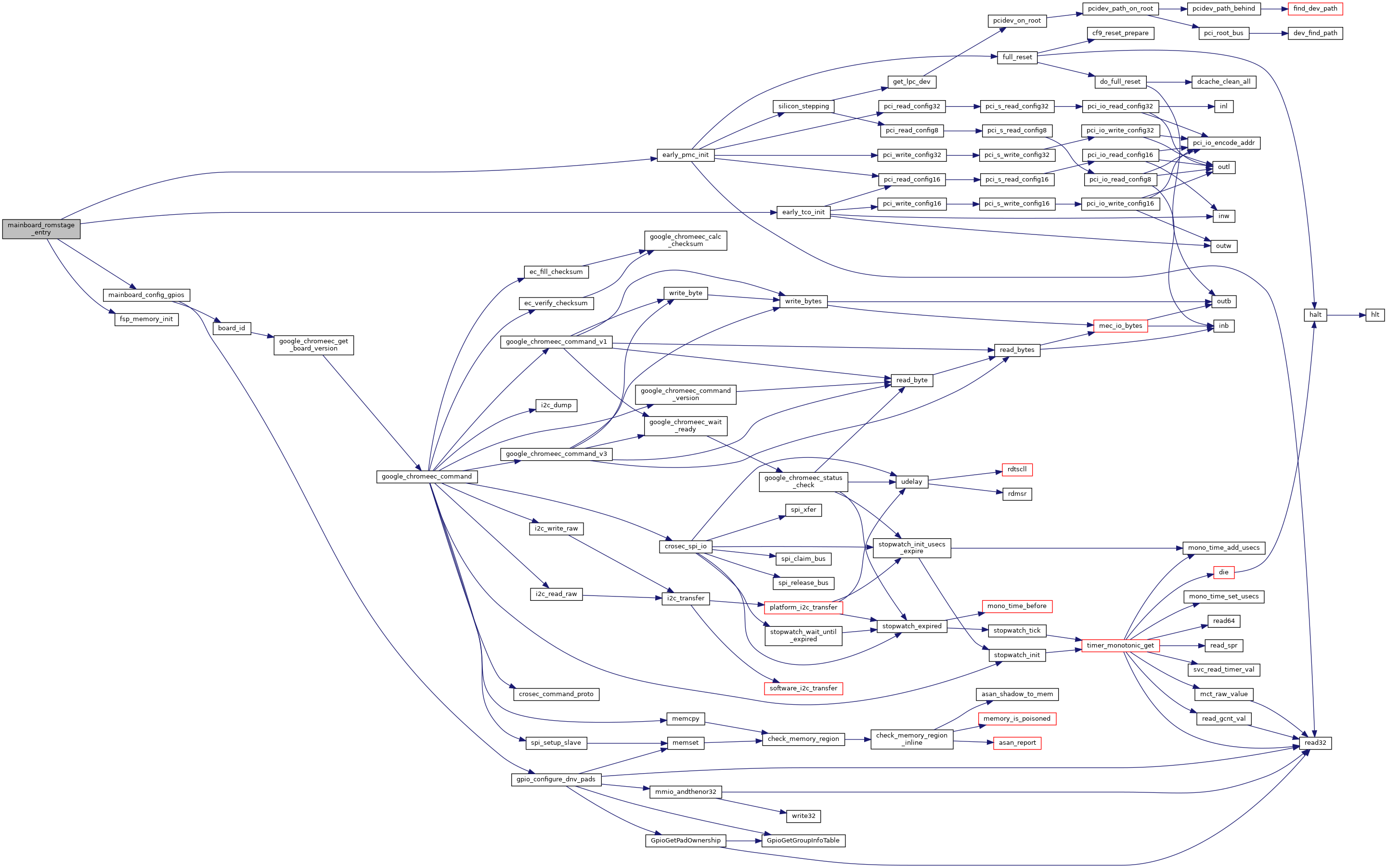

| void __weak | mainboard_config_gpios (void) |

| static void | early_pmc_init (void) |

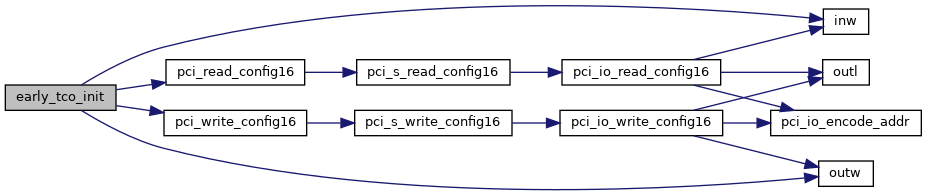

| static void | early_tco_init (void) |

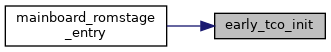

| void | mainboard_romstage_entry (void) |

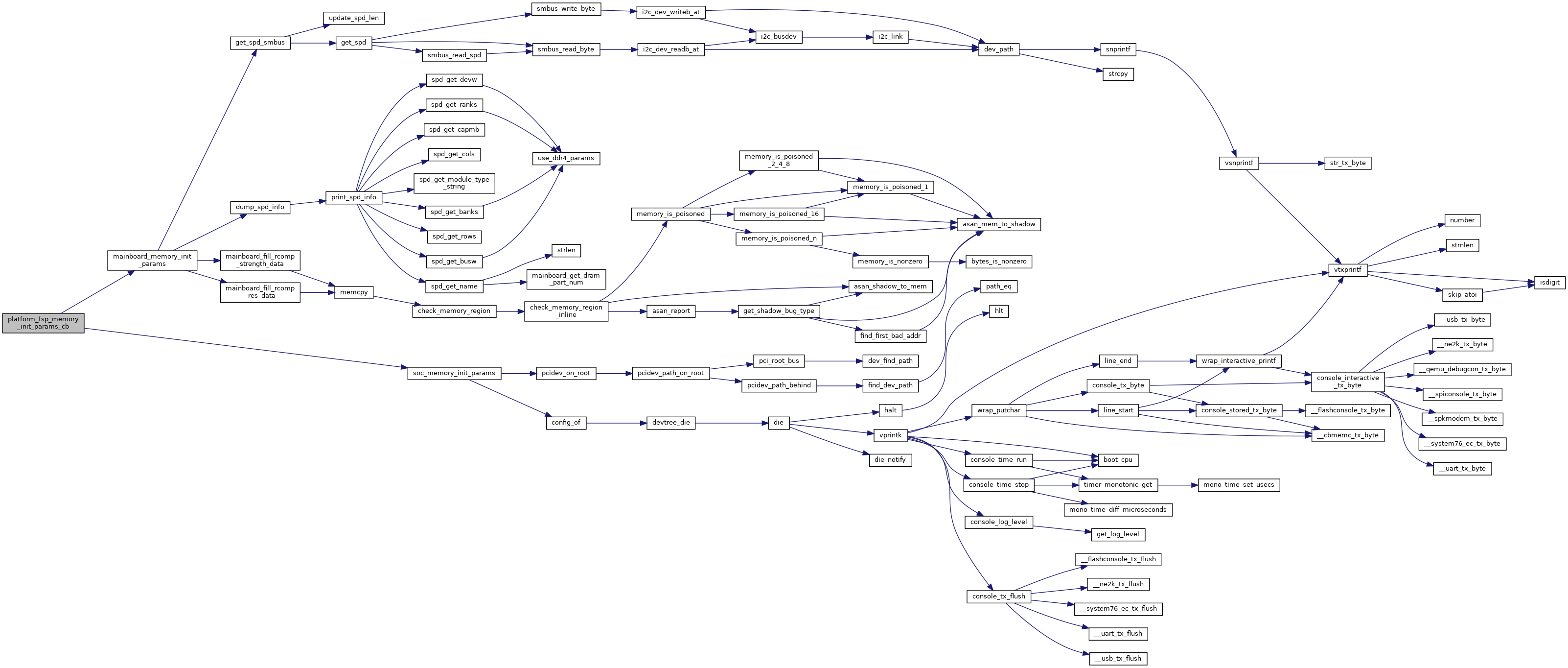

| static void | soc_memory_init_params (FSP_M_CONFIG *m_cfg) |

| __weak void | mainboard_memory_init_params (FSPM_UPD *mupd) |

| void | platform_fsp_memory_init_params_cb (FSPM_UPD *mupd, uint32_t version) |

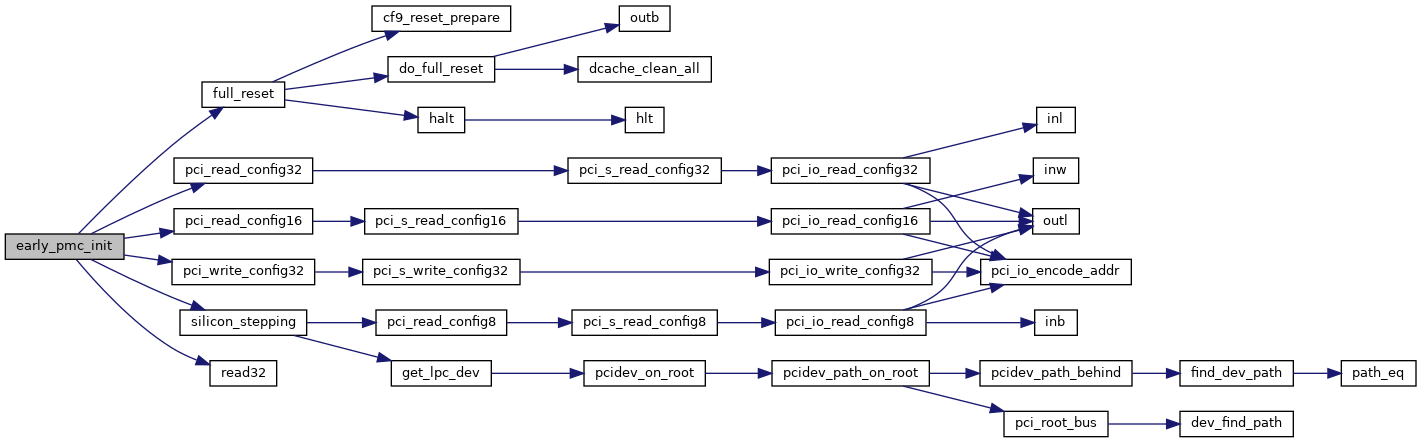

Definition at line 36 of file romstage.c.

References BIOS_DEBUG, BIOS_ERR, ETR3, ETR3_CF9GR, full_reset(), GEN_PMCON_B, GEN_PMCON_B_RTC_PWR_STS, MASK_PMC_PWRM_BASE, PCH_DEV_PMC, pci_read_config16(), pci_read_config32(), pci_write_config32(), PMC_PWRM_BASE, printk, read32(), SILICON_REV_DENVERTON_B0, and silicon_stepping().

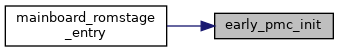

Referenced by mainboard_romstage_entry().

Definition at line 85 of file romstage.c.

References BIOS_DEBUG, BIOS_ERR, DEFAULT_TCO_BASE, inw(), MASK_TCOBASE, MMIO32_OR, outw(), PCH_PCR_ADDRESS, PCI_DEV, pci_read_config16(), pci_write_config16(), PCR_SMBUS_GC, PCR_SMBUS_GC_NR, PID_SMB, printk, SMBUS_DEV, SMBUS_FUNC, TCO1_CNT, TCO2_STS, TCO2_STS_SECOND_TO, TCO_TMR_HLT, TCOBASE, TCOBASE_EN, TCOBASE_LOCK, and TCOCTL.

Referenced by mainboard_romstage_entry().

Definition at line 19 of file romstage.c.

Definition at line 174 of file romstage.c.

Definition at line 122 of file romstage.c.

References BIOS_DEBUG, early_pmc_init(), early_tco_init(), fsp_memory_init(), mainboard_config_gpios(), and printk.

Definition at line 179 of file romstage.c.

References FSP_M_CONFIG, mainboard_memory_init_params(), and soc_memory_init_params().

|

static |

Definition at line 137 of file romstage.c.

References CONFIG, container_of, die(), get_fiamux_hsio_info(), and mainboard_get_hsio_config().