|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

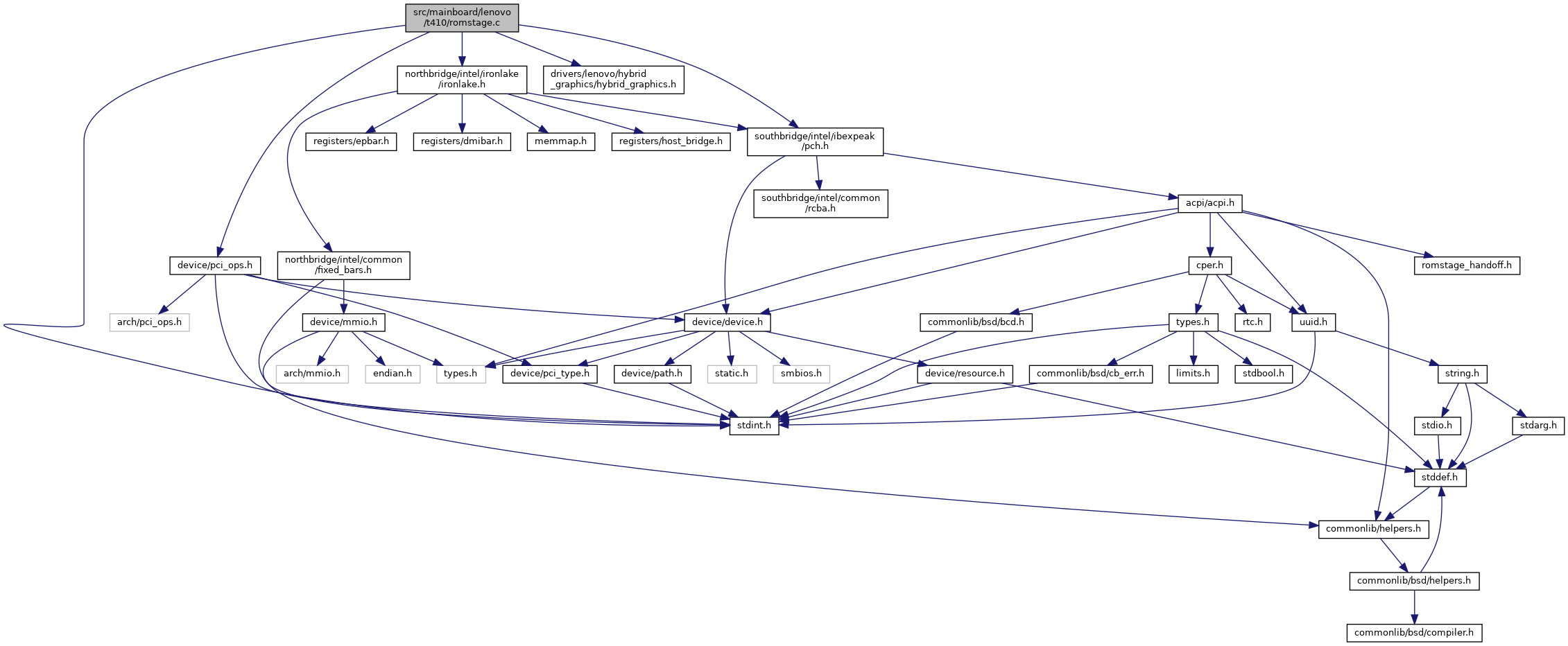

#include <stdint.h>#include <device/pci_ops.h>#include <southbridge/intel/ibexpeak/pch.h>#include <drivers/lenovo/hybrid_graphics/hybrid_graphics.h>#include <northbridge/intel/ironlake/ironlake.h>

Go to the source code of this file.

Functions | |

| static void | hybrid_graphics_init (void) |

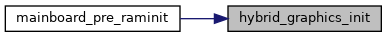

| void | mainboard_pre_raminit (void) |

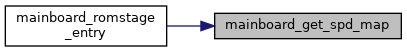

| void | mainboard_get_spd_map (u8 *spd_addrmap) |

Variables | |

| const struct southbridge_usb_port | mainboard_usb_ports [] |

Definition at line 27 of file romstage.c.

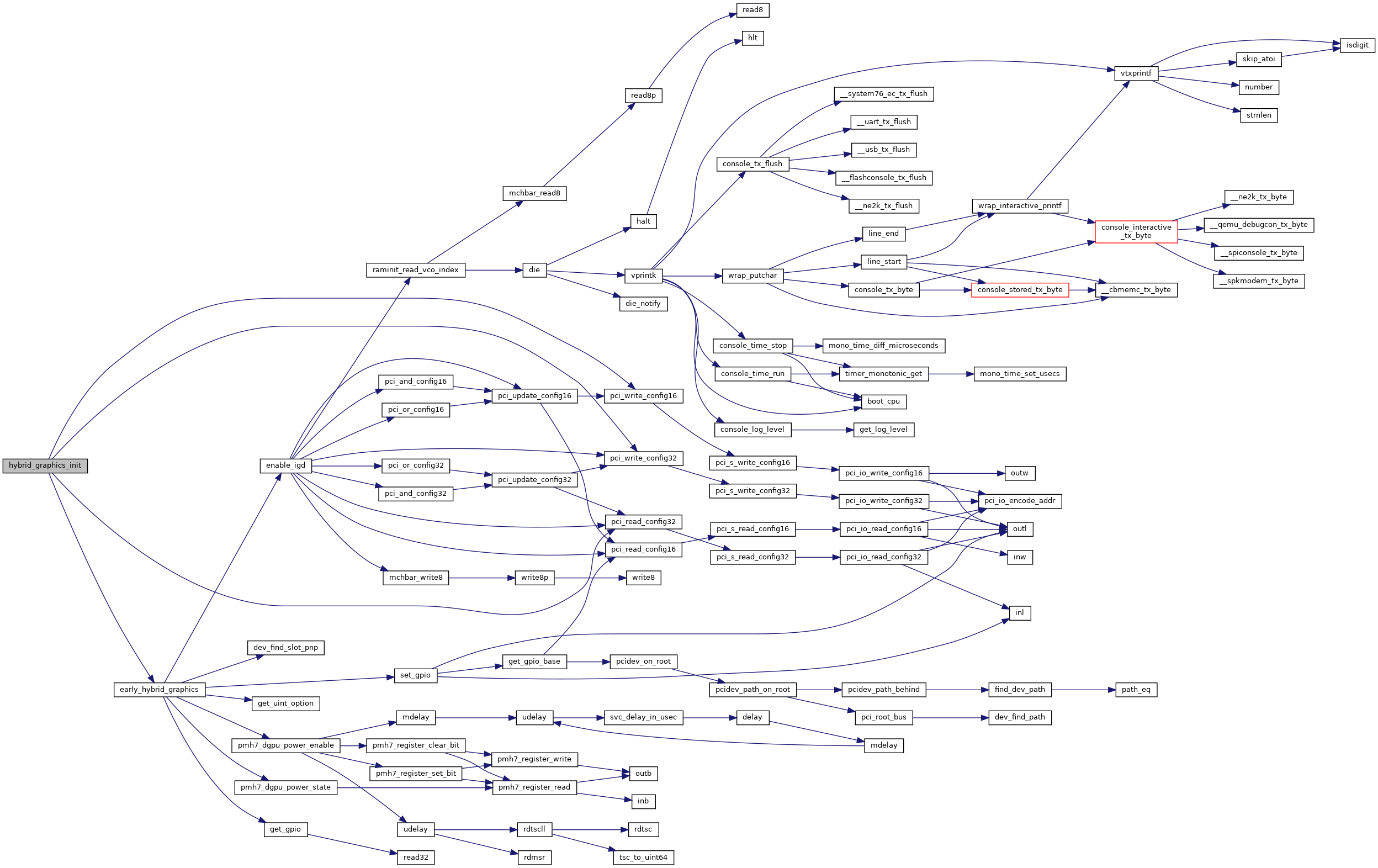

References DEVEN, DEVEN_IGD, DEVEN_PEG10, early_hybrid_graphics(), GGC, PCI_DEV, pci_read_config32(), pci_write_config16(), and pci_write_config32().

Referenced by mainboard_pre_raminit().

Definition at line 55 of file romstage.c.

Referenced by mainboard_romstage_entry().

Definition at line 50 of file romstage.c.

References hybrid_graphics_init().

| const struct southbridge_usb_port mainboard_usb_ports[] |

Definition at line 1 of file romstage.c.

Referenced by mainboard_romstage_entry().