|

| enum | { MDSS_BASE = 0xAE00000

} |

| |

| enum | {

MDP_0_CTL_BASE = MDSS_BASE + 0x2000

, MDP_VP_0_SSPP_BASE = MDSS_BASE + 0x5000

, MDP_VP_0_LAYER_MIXER_BASE = MDSS_BASE + 0x45000

, MDP_1_INTF_BASE = MDSS_BASE + 0x6b800

,

MDP_VBIF_RT_BASE = MDSS_BASE + 0xB0000

, DSI0_CTL_BASE = MDSS_BASE + 0x94000

, DSI0_PHY_BASE = MDSS_BASE + 0x94400

, DSI0_PHY_DLN0_BASE = MDSS_BASE + 0x94600

,

DSI0_PHY_DLN1_BASE = MDSS_BASE + 0x94680

, DSI0_PHY_DLN2_BASE = MDSS_BASE + 0x94700

, DSI0_PHY_DLN3_BASE = MDSS_BASE + 0x94780

, DSI0_PHY_CLKLN_BASE = MDSS_BASE + 0x94800

,

DSI0_PHY_PLL_QLINK_COM = MDSS_BASE + 0x94a00

} |

| |

| enum | {

INTF = BIT(31)

, PERIPH = BIT(30)

, CWB = BIT(28)

, ROT = BIT(27)

,

CDM_0 = BIT(26)

, DMA_3 = BIT(25)

, DMA_2 = BIT(24)

, MERGE_3D = BIT(23)

,

DSC = BIT(22)

, DSPP_3 = BIT(21)

, LAYER_MIXER_5 = BIT(20)

, DSPP_PA_LUTV_3 = BIT(19)

,

VIG_3 = BIT(18)

, CTL = BIT(17)

, WB = BIT(16)

, DSPP_2 = BIT(15)

,

DSPP_1 = BIT(14)

, DSPP_0 = BIT(13)

, DMA_1 = BIT(12)

, DMA_0 = BIT(11)

,

LAYER_MIXER_4 = BIT(10)

, LAYER_MIXER_3 = BIT(9)

, LAYER_MIXER_2 = BIT(8)

, LAYER_MIXER_1 = BIT(7)

,

LAYER_MIXER_0 = BIT(6)

, DSPP_PA_LUTV_2 = BIT(5)

, DSPP_PA_LUTV_1 = BIT(4)

, DSPP_PA_LUTV_0 = BIT(3)

,

VIG_2 = BIT(2)

, VIG_1 = BIT(1)

, VIG_0 = BIT(0)

} |

| |

| enum | {

DSI_AHBS_HCLK_ON = BIT(0)

, DSI_AHBM_SCLK_ON = BIT(1)

, DSI_PCLK_ON = BIT(2)

, DSI_DSICLK_ON = BIT(3)

,

DSI_BYTECLK_ON = BIT(4)

, DSI_ESCCLK_ON = BIT(5)

, DSI_FORCE_ON_DYN_AHBS_HCLK = BIT(8)

, DSI_FORCE_ON_DYN_AHBM_HCLK = BIT(9)

,

DSI_FORCE_ON_DYN_DSICLK = BIT(10)

, DSI_FORCE_ON_DYN_BYTECLK = BIT(11)

, DSI_AHBS_HCLK_HYSTERISIS1_CTRL = (3 << 11)

, DSI_AHBM_HCLK_HYSTERISIS1_CTRL = (3 << 13)

,

DSI_DSICLK_HYSTERISIS1_CTRL = (3 << 15)

, DSI_FORCE_ON_DYN_PCLK = BIT(20)

, DSI_FORCE_ON_LANE_LAYER_TG_BYTECLK = BIT(21)

, DSI_DMA_CLK_STOP = BIT(22)

} |

| |

| enum | {

DSI_CMD_MODE_DMA_DONE_AK = BIT(0)

, DSI_CMD_MODE_DMA_DONE_STAT = BIT(0)

, DSI_CMD_MODE_DMA_DONE_MASK = BIT(1)

, DSI_CMD_MODE_MDP_DONE_AK = BIT(8)

,

DSI_CMD_MODE_MDP_DONE_STAT = BIT(8)

, DSI_CMD_MODE_MDP_DONE_MASK = BIT(9)

, DSI_CMD_MDP_STREAM0_DONE_AK = BIT(10)

, DSI_CMD_MDP_STREAM0_DONE_STAT = BIT(10)

,

DSI_CMD_MDP_STREAM0_DONE_MASK = BIT(11)

, DSI_VIDEO_MODE_DONE_AK = BIT(16)

, DSI_VIDEO_MODE_DONE_STAT = BIT(16)

, DSI_VIDEO_MODE_DONE_MASK = BIT(17)

,

DSI_BTA_DONE_AK = BIT(20)

, DSI_BTA_DONE_STAT = BIT(20)

, DSI_BTA_DONE_MASK = BIT(21)

, DSI_ERROR_AK = BIT(24)

,

DSI_ERROR_STAT = BIT(24)

, DSI_ERROR_MASK = BIT(25)

, DSI_DYNAMIC_BLANKING_DMA_DONE_AK = BIT(26)

, DSI_DYNAMIC_BLANKING_DMA_DONE_STAT = BIT(26)

,

DSI_DYNAMIC_BLANKING_DMA_DONE_MASK = BIT(27)

, DSI_DYNAMIC_REFRESH_DONE_AK = BIT(28)

, DSI_DYNAMIC_REFRESH_DONE_STAT = BIT(28)

, DSI_DYNAMIC_REFRESH_DONE_MASK = BIT(29)

,

DSI_DESKEW_DONE_AK = BIT(30)

, DSI_DESKEW_DONE_STAT = BIT(30)

, DSI_DESKEW_DONE_MASK = BIT(31)

} |

| |

| enum | { WR_MEM_START = 255

, WR_MEM_CONTINUE = 255 << 8

, INSERT_DCS_COMMAND = BIT(16)

} |

| |

| enum | {

PACKET_TYPE = BIT(24)

, POWER_MODE = BIT(26)

, EMBEDDED_MODE = BIT(28)

, WC_SEL = BIT(29)

,

BROADCAST_MASTER = BIT(30)

, BROADCAST_EN = BIT(31)

} |

| |

|

| | check_member (dsi_regs, video_mode_active_h, 0x24) |

| |

| | check_member (dsi_regs, cmd_mode_mdp_stream0_ctrl, 0x58) |

| |

| | check_member (dsi_regs, trig_ctrl, 0x84) |

| |

| | check_member (dsi_regs, cmd_mode_dma_sw_trigger, 0x90) |

| |

| | check_member (dsi_regs, misr_cmd_ctrl, 0xA0) |

| |

| | check_member (dsi_regs, hs_timer_ctrl, 0xBC) |

| |

| | check_member (dsi_regs, err_int_mask0, 0x10C) |

| |

| | check_member (dsi_regs, test_pattern_gen_ctrl, 0x15c) |

| |

| | check_member (dsi_regs, test_pattern_gen_cmd_dma_init_val, 0x17c) |

| |

| | check_member (dsi_regs, cmd_mode_mdp_ctrl2, 0x1B8) |

| |

| | check_member (dsi_regs, tpg_dma_fifo_reset, 0x1EC) |

| |

| | check_member (dsi_regs, video_compression_mode_ctrl, 0x2A0) |

| |

| | check_member (dsi_phy_regs, phy_cmn_clk_cfg0, 0x10) |

| |

| | check_member (dsi_phy_regs, phy_cmn_dsi_lane_ctrl0, 0x98) |

| |

| | check_member (dsi_phy_regs, phy_cmn_timing_ctrl[0], 0xAC) |

| |

| | check_member (dsi_phy_regs, phy_cmn_phy_status, 0xEC) |

| |

| | check_member (dsi_phy_regs, phy_ln_regs[0], 0x200) |

| |

| | check_member (dsi_phy_regs, phy_ln_regs[1], 0x280) |

| |

| | check_member (dsi_phy_regs, phy_ln_regs[2], 0x300) |

| |

| | check_member (dsi_phy_regs, phy_ln_regs[3], 0x380) |

| |

| | check_member (dsi_phy_regs, phy_ln_regs[4], 0x400) |

| |

| | check_member (dsi_phy_pll_qlink_regs, pll_mash_ctrl, 0xEC) |

| |

| | check_member (dsi_phy_pll_qlink_regs, pll_ssc_mux_ctrl, 0x108) |

| |

| | check_member (dsi_phy_pll_qlink_regs, pll_ssc_ctrl, 0x13C) |

| |

| | check_member (dsi_phy_pll_qlink_regs, pll_freq_tune_accum_init_mux, 0x17C) |

| |

| | check_member (mdp_intf_regs, intf_panel_format, 0x90) |

| |

| | check_member (mdp_intf_regs, intf_prof_fetch_start, 0x170) |

| |

| | check_member (mdp_intf_regs, intf_mux, 0x25C) |

| |

| | check_member (mdp_ctl_regs, ctl_top, 0x14) |

| |

| | check_member (mdp_ctl_regs, ctl_intf_active, 0xF4) |

| |

| | check_member (mdp_ctl_regs, ctl_intf_flush, 0x110) |

| |

| | check_member (mdp_sspp_regs, sspp_sw_pic_ext_c0_req_pixels, 0x108) |

| |

| | check_member (mdp_sspp_regs, sspp_sw_pic_ext_c1c2_req_pixels, 0x118) |

| |

| | check_member (mdp_sspp_regs, sspp_sw_pic_ext_c3_req_pixels, 0x128) |

| |

| | check_member (vbif_rt_regs, vbif_out_axi_amemtype_conf0, 0x160) |

| |

| | check_member (vbif_rt_regs, qos_rp_remap[0], 0x550) |

| |

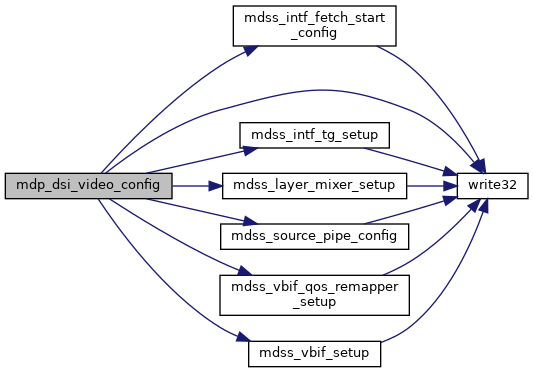

| void | mdp_dsi_video_config (struct edid *edid) |

| |

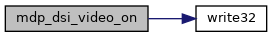

| void | mdp_dsi_video_on (void) |

| |