|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

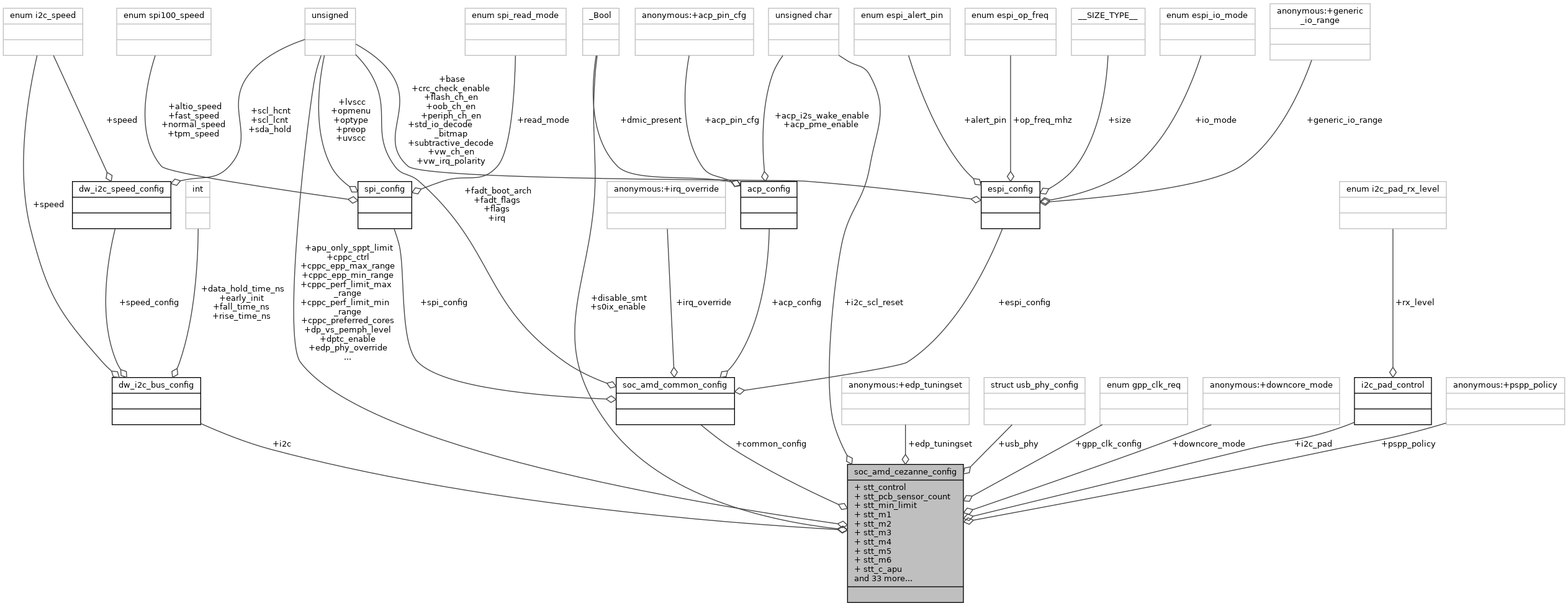

#include <chip.h>

Public Types | |

| enum | { DOWNCORE_AUTO = 0 , DOWNCORE_1 = 1 , DOWNCORE_2 = 3 , DOWNCORE_3 = 4 , DOWNCORE_4 = 6 , DOWNCORE_5 = 8 , DOWNCORE_6 = 9 , DOWNCORE_7 = 10 } |

| enum | { DXIO_PSPP_DISABLED = 0 , DXIO_PSPP_PERFORMANCE , DXIO_PSPP_BALANCED , DXIO_PSPP_POWERSAVE } |

| anonymous enum |

| anonymous enum |

| struct soc_amd_common_config soc_amd_cezanne_config::common_config |

Definition at line 1 of file chip.h.

Referenced by acpi_fill_fadt(), and soc_get_common_config().

| enum { ... } soc_amd_cezanne_config::downcore_mode |

| struct { ... } soc_amd_cezanne_config::edp_tuningset |

| uint32_t soc_amd_cezanne_config::fast_ppt_limit_tablet_mode_mW |

| enum gpp_clk_req soc_amd_cezanne_config::gpp_clk_config[GPP_CLK_OUTPUT_COUNT] |

Definition at line 96 of file chip.h.

Referenced by gpp_clk_setup().

| struct dw_i2c_bus_config soc_amd_cezanne_config::i2c[I2C_CTRLR_COUNT] |

| struct i2c_pad_control soc_amd_cezanne_config::i2c_pad[I2C_CTRLR_COUNT] |

| u8 soc_amd_cezanne_config::i2c_scl_reset |

Definition at line 23 of file chip.h.

Referenced by reset_i2c_peripherals().

| enum { ... } soc_amd_cezanne_config::pspp_policy |

| bool soc_amd_cezanne_config::s0ix_enable |

Definition at line 28 of file chip.h.

Referenced by acpi_fill_fadt().

| uint32_t soc_amd_cezanne_config::slow_ppt_limit_tablet_mode_mW |

| uint32_t soc_amd_cezanne_config::sustained_power_limit_tablet_mode_mW |

| uint32_t soc_amd_cezanne_config::telemetry_vddcrsocfull_scale_current_mA |

| uint32_t soc_amd_cezanne_config::telemetry_vddcrvddfull_scale_current_mA |

| uint32_t soc_amd_cezanne_config::thermctl_limit_tablet_mode_degreeC |