|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

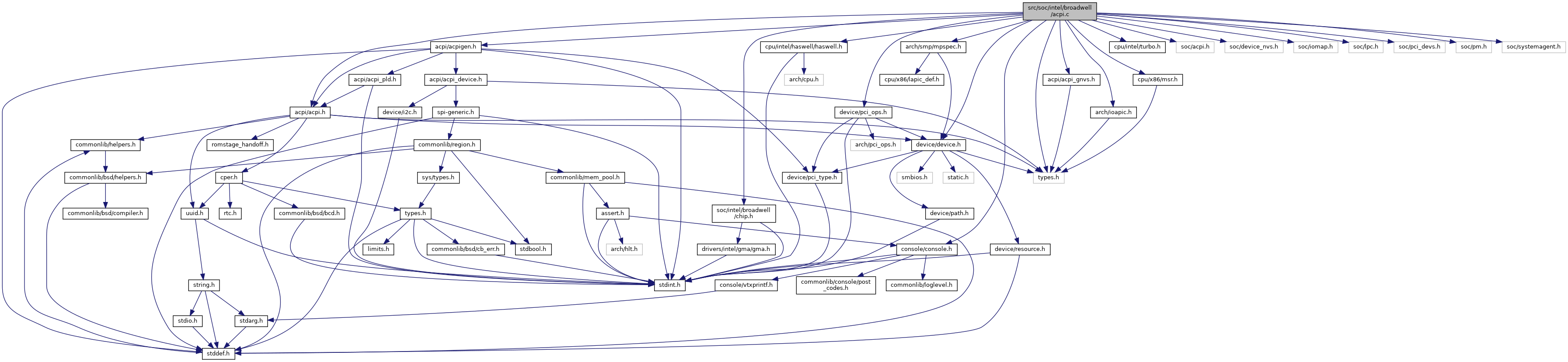

#include <acpi/acpi.h>#include <acpi/acpi_gnvs.h>#include <acpi/acpigen.h>#include <arch/ioapic.h>#include <arch/smp/mpspec.h>#include <cpu/intel/haswell/haswell.h>#include <device/pci_ops.h>#include <console/console.h>#include <device/device.h>#include <types.h>#include <cpu/x86/msr.h>#include <cpu/intel/turbo.h>#include <soc/acpi.h>#include <soc/device_nvs.h>#include <soc/iomap.h>#include <soc/lpc.h>#include <soc/pci_devs.h>#include <soc/pm.h>#include <soc/systemagent.h>#include <soc/intel/broadwell/chip.h>

Go to the source code of this file.

Functions | |

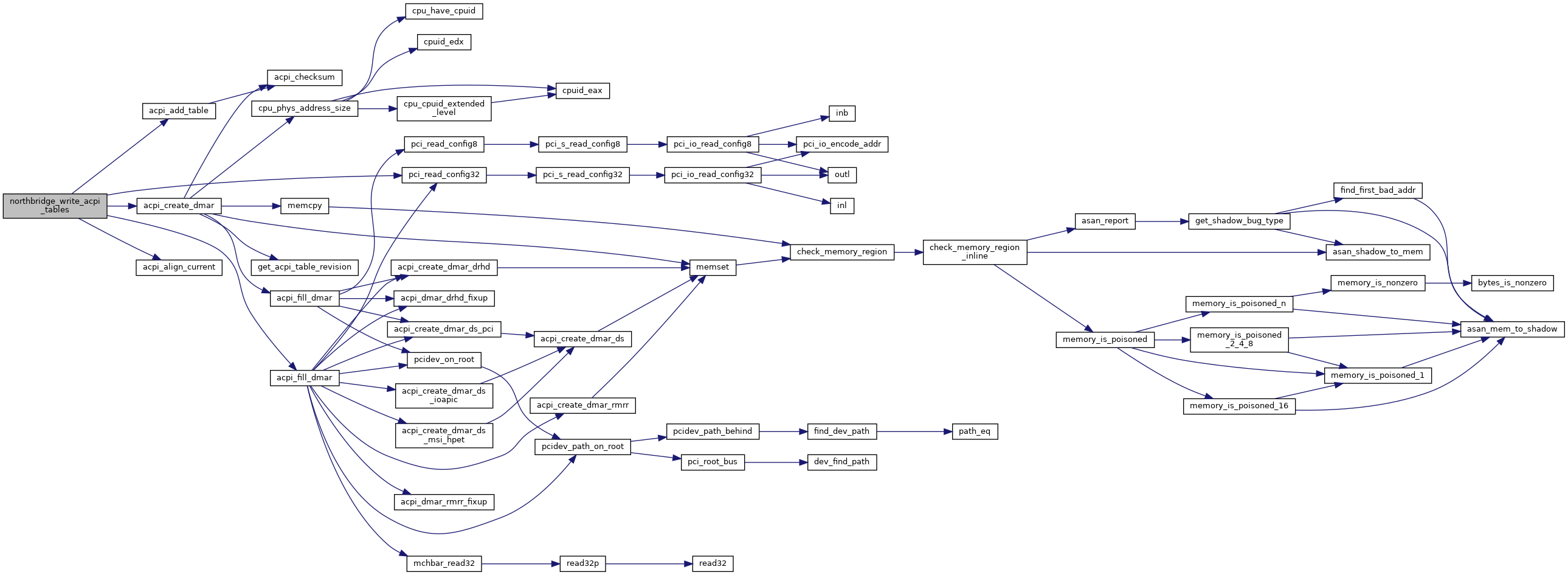

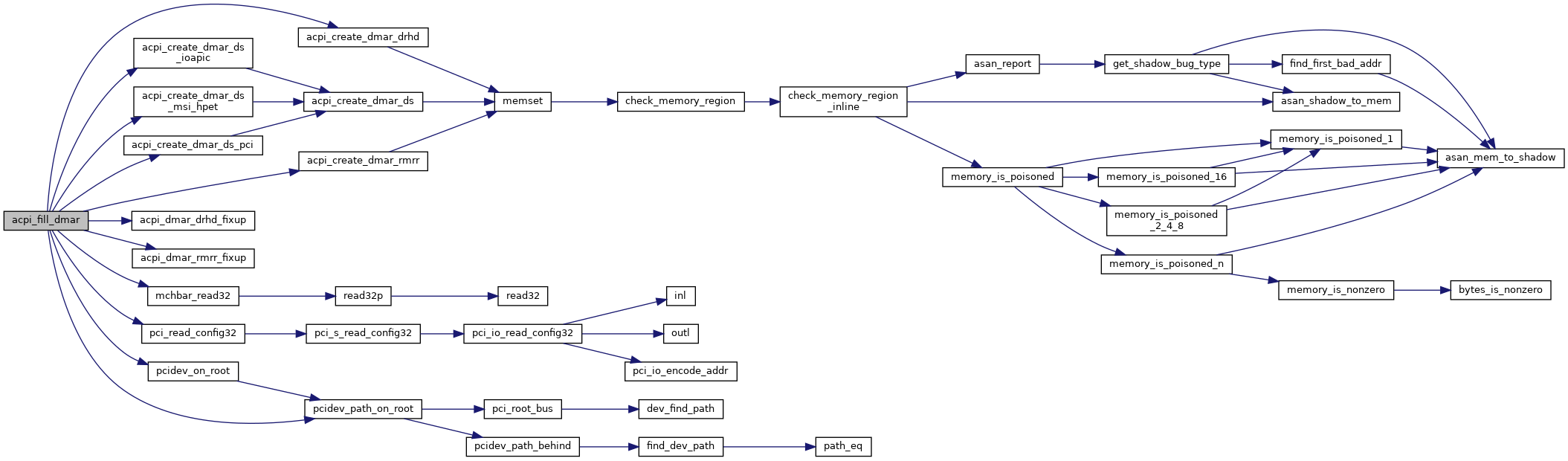

| static unsigned long | acpi_fill_dmar (unsigned long current) |

| unsigned long | northbridge_write_acpi_tables (const struct device *const dev, unsigned long current, struct acpi_rsdp *const rsdp) |

| size_t | size_of_dnvs (void) |

Definition at line 24 of file acpi.c.

References acpi_create_dmar_drhd(), acpi_create_dmar_ds_ioapic(), acpi_create_dmar_ds_msi_hpet(), acpi_create_dmar_ds_pci(), acpi_create_dmar_rmrr(), acpi_dmar_drhd_fixup(), acpi_dmar_rmrr_fixup(), BGSM, DRHD_INCLUDE_PCI_ALL, device::enabled, GFXVTBAR, mchbar_read32(), PCH_HPET_PCI_BUS, PCH_HPET_PCI_SLOT, PCH_IOAPIC_PCI_BUS, PCH_IOAPIC_PCI_SLOT, pci_read_config32(), pcidev_on_root(), pcidev_path_on_root(), SA_DEVFN_IGD, TOLUD, and VTVC0BAR.

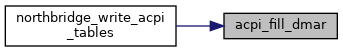

Referenced by northbridge_write_acpi_tables().

| unsigned long northbridge_write_acpi_tables | ( | const struct device *const | dev, |

| unsigned long | current, | ||

| struct acpi_rsdp *const | rsdp | ||

| ) |

Definition at line 81 of file acpi.c.

References acpi_add_table(), acpi_align_current(), acpi_create_dmar(), acpi_fill_dmar(), BIOS_DEBUG, CAPID0_A, DMAR_INTR_REMAP, acpi_dmar::header, acpi_table_header::length, pci_read_config32(), printk, and VTD_DISABLE.