|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <commonlib/stdlib.h>#include <console/console.h>#include <device/mmio.h>#include <device/resource.h>#include <delay.h>#include <soc/addressmap.h>#include <soc/early_init.h>#include <soc/gpio.h>#include <soc/pcie.h>#include <soc/pcie_common.h>#include <stdlib.h>#include <string.h>

Go to the source code of this file.

Data Structures | |

| struct | pad_func |

Macros | |

| #define | PCIE_REG_BASE_PORT0 0x112f0000 |

| #define | PCIE_RST_CTRL_REG (PCIE_REG_BASE_PORT0 + 0x148) |

| #define | PCIE_MAC_RSTB BIT(0) |

| #define | PCIE_PHY_RSTB BIT(1) |

| #define | PCIE_BRG_RSTB BIT(2) |

| #define | PCIE_PE_RSTB BIT(3) |

| #define | PAD_FUNC(name, func) {GPIO(name), PAD_##name##_FUNC_##func} |

Functions | |

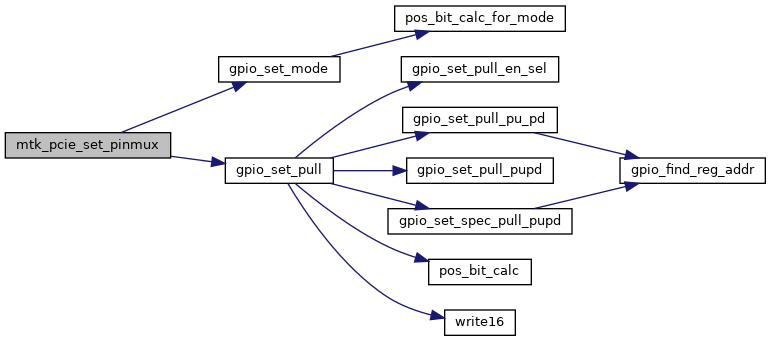

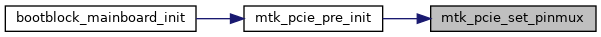

| static void | mtk_pcie_set_pinmux (uint8_t port) |

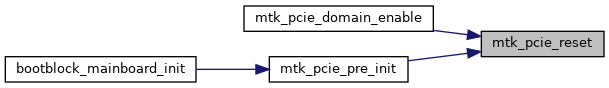

| void | mtk_pcie_reset (uintptr_t reg, bool enable) |

| void | mtk_pcie_pre_init (void) |

Variables | |

| static const struct pad_func | pcie_pins [2][3] |

| #define PCIE_RST_CTRL_REG (PCIE_REG_BASE_PORT0 + 0x148) |

Definition at line 70 of file pcie.c.

References EARLY_INIT_PCIE, early_init_save_time(), mtk_pcie_reset(), mtk_pcie_set_pinmux(), and PCIE_RST_CTRL_REG.

Referenced by bootblock_mainboard_init().

Definition at line 54 of file pcie.c.

References PCIE_BRG_RSTB, PCIE_MAC_RSTB, PCIE_PE_RSTB, PCIE_PHY_RSTB, read32p(), val, and write32p().

Referenced by mtk_pcie_domain_enable(), and mtk_pcie_pre_init().

Definition at line 43 of file pcie.c.

References ARRAY_SIZE, pad_func::func, GPIO_PULL_ENABLE, GPIO_PULL_UP, gpio_set_mode(), gpio_set_pull(), pcie_pins, and pins.

Referenced by mtk_pcie_pre_init().

|

static |