|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

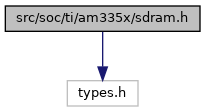

#include <types.h>

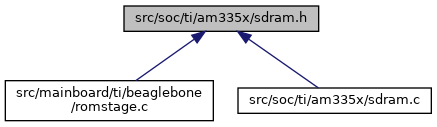

Go to the source code of this file.

Data Structures | |

| struct | ctrl_ioregs |

| struct | ddr_data |

| Encapsulates DDR DATA registers. More... | |

| struct | cmd_control |

| Encapsulates DDR CMD control registers. More... | |

| struct | emif_regs |

| struct | vtp_reg |

| struct | emif_reg_struct |

| struct | ddr_cmd_regs |

| struct | ddr_data_regs |

| struct | ctrl_stat |

| struct | ddr_cmdtctrl |

| This structure represents the DDR io control on AM33XX devices. More... | |

| struct | ddr_ctrl |

Macros | |

| #define | VTP_CTRL_READY (0x1 << 5) |

| #define | VTP_CTRL_ENABLE (0x1 << 6) |

| #define | VTP_CTRL_START_EN (0x1) |

| #define | DDR_CKE_CTRL_NORMAL 0x1 |

| #define | PHY_EN_DYN_PWRDN (0x1 << 20) |

| #define | VTP0_CTRL_ADDR 0x44E10E0C |

| #define | VTP1_CTRL_ADDR 0x48140E10 |

| #define | EMIF4_0_CFG_BASE 0x4C000000 |

| #define | EMIF4_1_CFG_BASE 0x4D000000 |

| #define | DDR_PHY_CMD_ADDR 0x44E12000 |

| #define | DDR_PHY_DATA_ADDR 0x44E120C8 |

| #define | DDR_PHY_CMD_ADDR2 0x47C0C800 |

| #define | DDR_PHY_DATA_ADDR2 0x47C0C8C8 |

| #define | DDR_DATA_REGS_NR 2 |

| #define | DDR_CTRL_ADDR 0x44E10E04 |

| #define | DDR_CONTROL_BASE_ADDR 0x44E11404 |

| #define | CTRL_BASE 0x44E10000 |

| #define | EMIF_REG_MAJOR_REVISION_SHIFT 8 |

| #define | EMIF_REG_MAJOR_REVISION_MASK (0x7 << 8) |

| #define | EMIF_REG_SDRAM_TYPE_SHIFT 29 |

| #define | EMIF_REG_SDRAM_TYPE_MASK (0x7 << 29) |

| #define | EMIF_EXT_PHY_CTRL_TIMING_REG 0x5 |

| #define | EMIF_REG_INITREF_DIS_MASK (1 << 31) |

| #define | EMIF_4D5 0x5 |

| #define | EMIF_SDRAM_TYPE_DDR2 0x2 |

| #define | EMIF_SDRAM_TYPE_DDR3 0x3 |

| #define | EMIF_SDRAM_TYPE_LPDDR2 0x4 |

| #define | PLL_BYPASS_MODE 0x4 |

| #define | ST_MN_BYPASS 0x00000100 |

| #define | ST_DPLL_CLK 0x00000001 |

| #define | CLK_SEL_MASK 0x7ffff |

| #define | CLK_DIV_MASK 0x1f |

| #define | CLK_DIV2_MASK 0x7f |

| #define | CLK_SEL_SHIFT 0x8 |

| #define | CLK_MODE_SEL 0x7 |

| #define | CLK_MODE_MASK 0xfffffff8 |

| #define | CLK_DIV_SEL 0xFFFFFFE0 |

| #define | CPGMAC0_IDLE 0x30000 |

| #define | DPLL_CLKDCOLDO_GATE_CTRL 0x300 |

| #define | V_OSCK 24000000 /* Clock output from T2 */ |

| #define | OSC (V_OSCK / 1000000) |

| #define | DDRPLL_M 266 |

| #define | DDRPLL_N (OSC - 1) |

| #define | DDRPLL_M2 1 |

Functions | |

| void | config_ddr (uint32_t pll, const struct ctrl_ioregs *ioregs, const struct ddr_data *data, const struct cmd_control *ctrl, const struct emif_regs *regs, int nr) |

| void config_ddr | ( | uint32_t | pll, |

| const struct ctrl_ioregs * | ioregs, | ||

| const struct ddr_data * | data, | ||

| const struct cmd_control * | ctrl, | ||

| const struct emif_regs * | regs, | ||

| int | nr | ||

| ) |

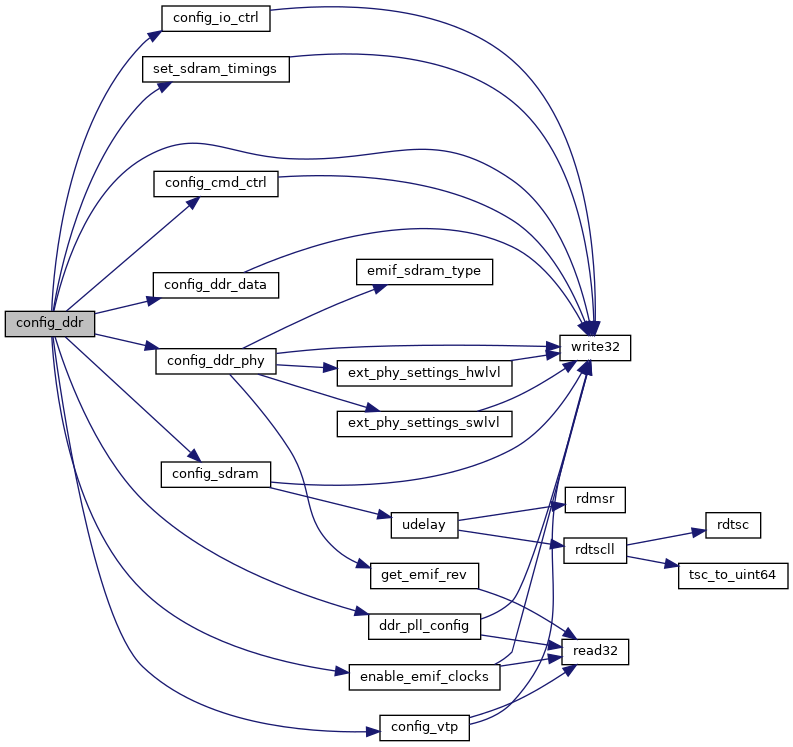

Definition at line 311 of file sdram.c.

References config_cmd_ctrl(), config_ddr_data(), config_ddr_phy(), config_io_ctrl(), config_sdram(), config_vtp(), DDR_CKE_CTRL_NORMAL, ddr_pll_config(), ddr_ctrl::ddrckectrl, ddrctrl, enable_emif_clocks(), set_sdram_timings(), and write32().

Referenced by main().