|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

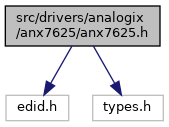

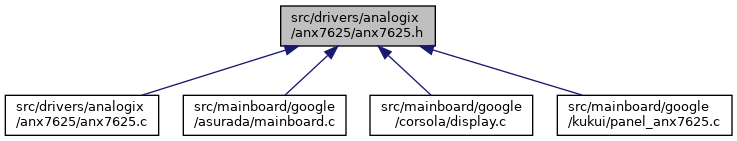

#include <edid.h>#include <types.h>

Go to the source code of this file.

Data Structures | |

| struct | display_timing |

Enumerations | |

| enum | AudioFs { AUDIO_FS_441K = 0x00 , AUDIO_FS_48K = 0x02 , AUDIO_FS_32K = 0x03 , AUDIO_FS_882K = 0x08 , AUDIO_FS_96K = 0x0a , AUDIO_FS_1764K = 0x0c , AUDIO_FS_192K = 0x0e } |

| enum | AudioWdLen { AUDIO_W_LEN_16_20MAX = 0x02 , AUDIO_W_LEN_18_20MAX = 0x04 , AUDIO_W_LEN_17_20MAX = 0x0c , AUDIO_W_LEN_19_20MAX = 0x08 , AUDIO_W_LEN_20_20MAX = 0x0a , AUDIO_W_LEN_20_24MAX = 0x03 , AUDIO_W_LEN_22_24MAX = 0x05 , AUDIO_W_LEN_21_24MAX = 0x0d , AUDIO_W_LEN_23_24MAX = 0x09 , AUDIO_W_LEN_24_24MAX = 0x0b } |

Functions | |

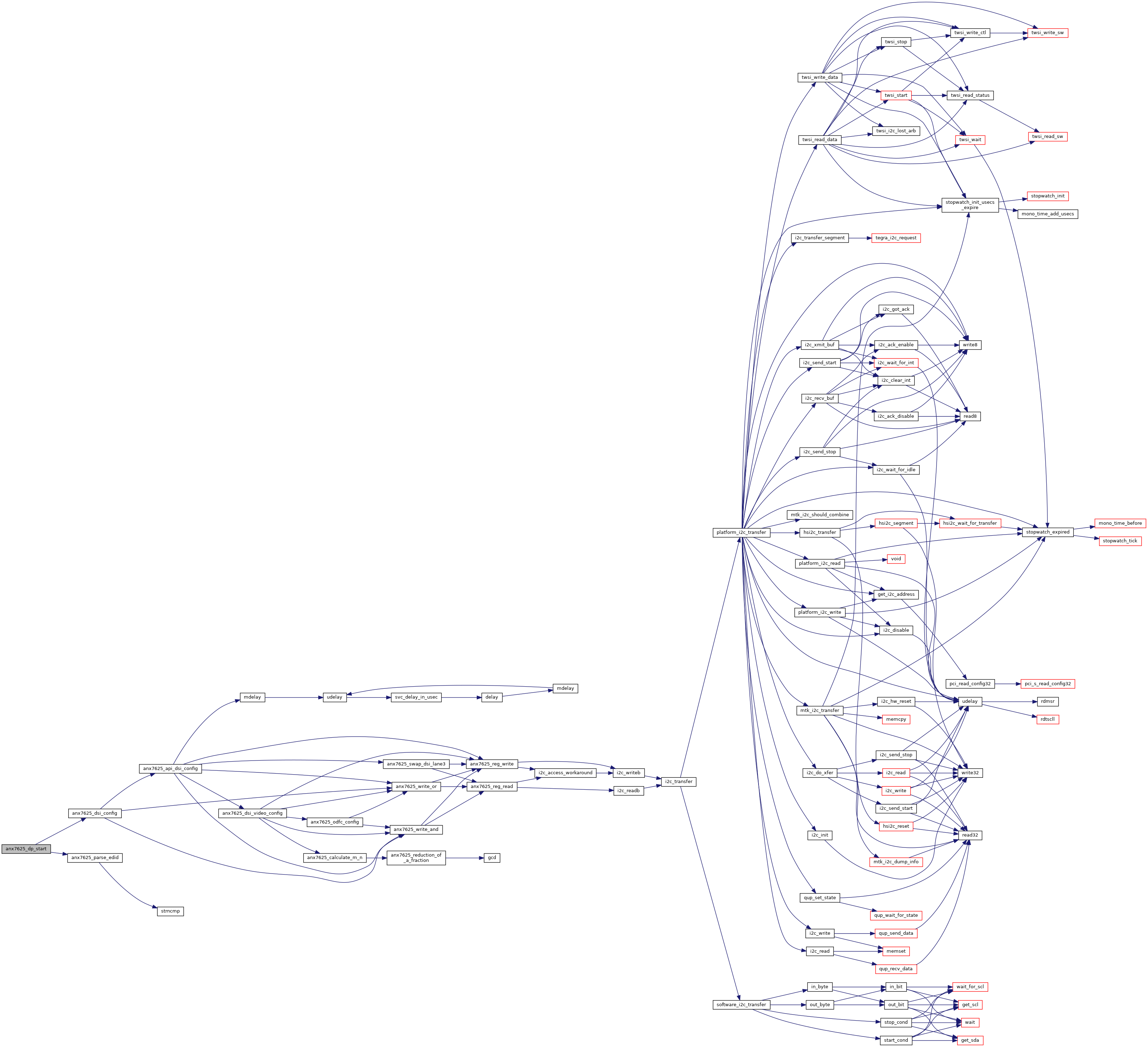

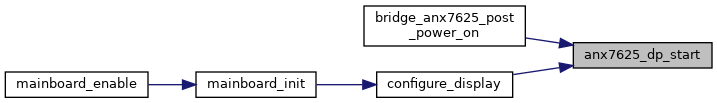

| int | anx7625_dp_start (uint8_t bus, const struct edid *edid) |

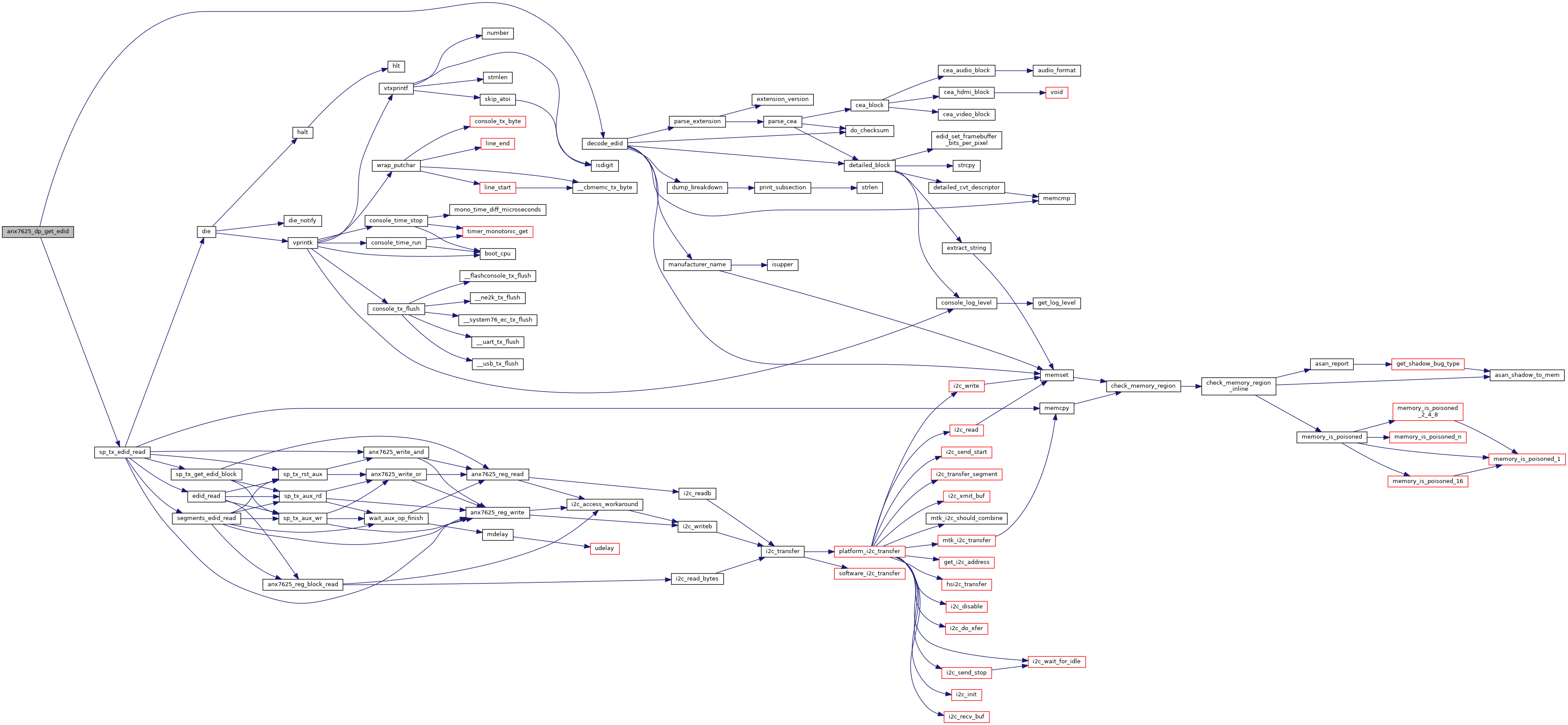

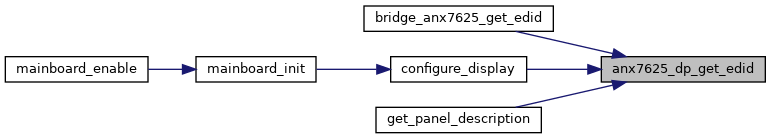

| int | anx7625_dp_get_edid (uint8_t bus, struct edid *out) |

| int | anx7625_init (uint8_t bus) |

| #define ACTIVE_LINES_H 0x15 /* note: bit[7:6] are reserved */ |

| #define AP_MIPI_MUTE (1<<4) /* 1:MIPI input mute, 0: ummute */ |

| #define HORIZONTAL_ACTIVE_PIXELS_H 0x1C /* note: bit[7:6] are reserved */ |

| #define HORIZONTAL_BACK_PORCH_H 0x22 /* note: bit[7:4] are reserved */ |

| #define HORIZONTAL_FRONT_PORCH_H 0x1E /* note: bit[7:4] are reserved */ |

| #define HORIZONTAL_SYNC_WIDTH_H 0x20 /* note: bit[7:4] are reserved */ |

| #define HORIZONTAL_TOTAL_PIXELS_H 0x1A /* note: bit[7:6] are reserved */ |

| #define XTAL_FRQ_19M2 (0 << XTAL_FRQ_SEL_POS) |

| #define XTAL_FRQ_27M (4 << XTAL_FRQ_SEL_POS) |

| enum AudioFs |

| enum AudioWdLen |

Definition at line 845 of file anx7625.c.

References ANXERROR, decode_edid(), EDID_CONFORMANT, FOUR_BLOCK_SIZE, ONE_BLOCK_SIZE, and sp_tx_edid_read().

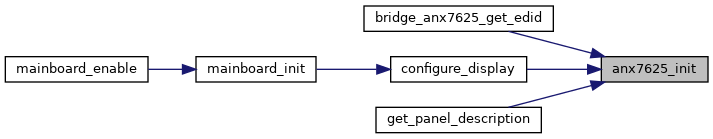

Referenced by bridge_anx7625_get_edid(), configure_display(), and get_panel_description().

Definition at line 828 of file anx7625.c.

References anx7625_dsi_config(), anx7625_parse_edid(), ANXERROR, and ANXINFO.

Referenced by bridge_anx7625_post_power_on(), and configure_display().

| int anx7625_init | ( | uint8_t | bus | ) |

Definition at line 866 of file anx7625.c.

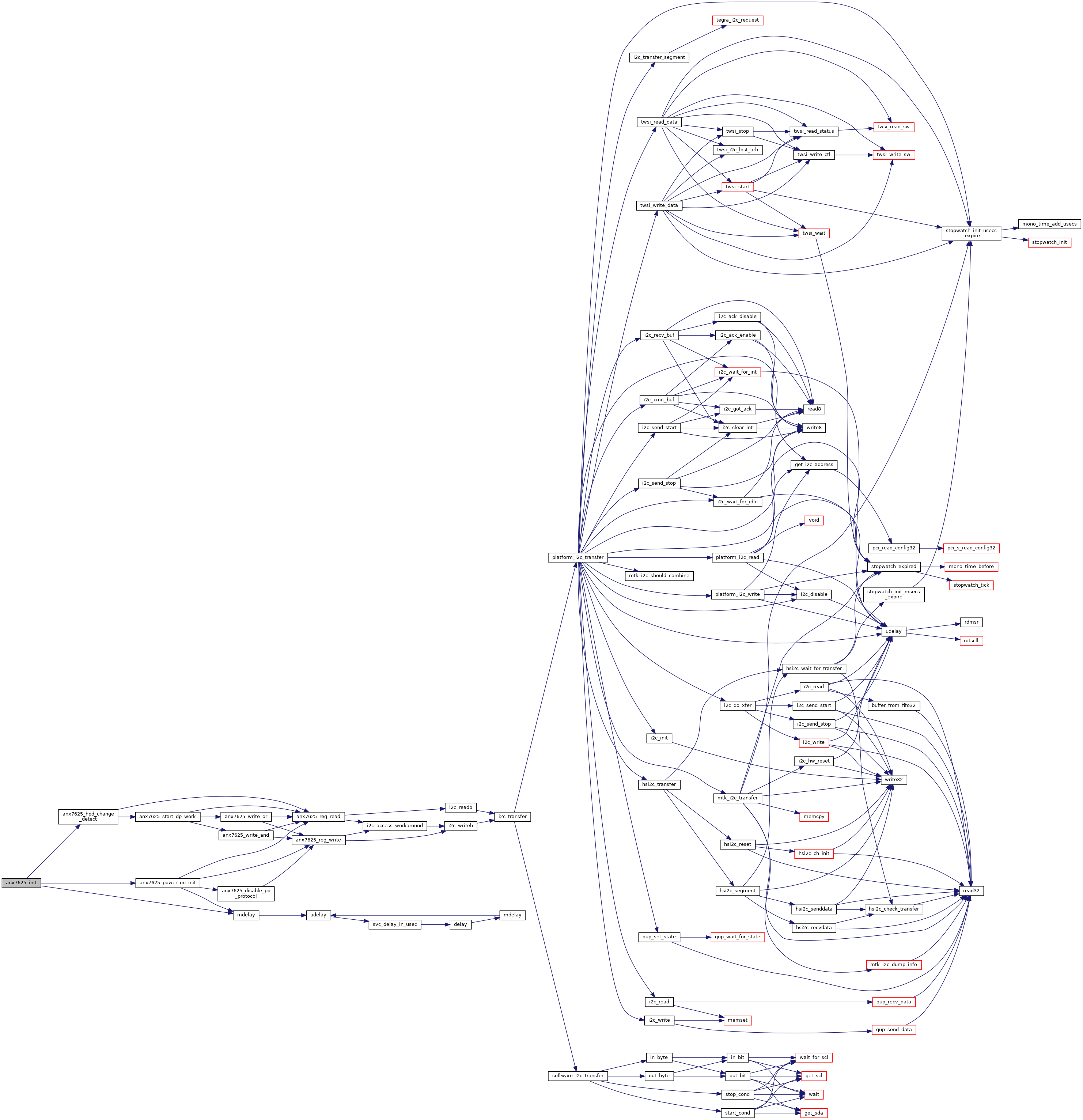

References anx7625_hpd_change_detect(), anx7625_power_on_init(), ANXERROR, mdelay(), and retry.

Referenced by bridge_anx7625_get_edid(), configure_display(), and get_panel_description().