|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Data Structures | |

| struct | lp0_header |

Macros | |

| #define | MBIST_CLK_ENB_L_0 0x80000130 |

| #define | MBIST_CLK_ENB_H_0 0x020000C1 |

| #define | MBIST_CLK_ENB_U_0 0x01F00200 |

| #define | MBIST_CLK_ENB_V_0 0x80400008 |

| #define | MBIST_CLK_ENB_W_0 0x002000FC |

| #define | MBIST_CLK_ENB_X_0 0x23004780 |

| #define | MBIST_CLK_ENB_Y_0 0x00000300 |

| #define | MAX77620_I2C_ADDR (0x3c << 1) |

| #define | MAX77620_GPIO5_DATA (0x3b | (0x9 << 8)) |

| #define | MAX77621_I2C_ADDR (0x1b << 1) |

| #define | MAX77621_VOUT_REG 0x0 |

| #define | MAX77621_VOUT_VAL (0x80 | 0x27) |

| #define | MAX77621_VOUT_DATA (MAX77621_VOUT_REG | (MAX77621_VOUT_VAL << 8)) |

Enumerations | |

| enum | { UP_TAG_BASE = 0x60000000 , TIMER_BASE = 0x60005000 , CLK_RST_BASE = 0x60006000 , FLOW_CTLR_BASE = 0x60007000 , SECURE_BOOT_BASE = 0x6000C200 , TEGRA_EVP_BASE = 0x6000f000 , APB_MISC_BASE = 0x70000000 , PINMUX_BASE = 0x70003000 , PMC_CTLR_BASE = 0x7000e400 , MC_CTLR_BASE = 0x70019000 , FUSE_BASE = 0x7000F800 , TEGRA_SDMMC1_BASE = 0x700b0000 , TEGRA_SDMMC3_BASE = 0x700b0400 , EMC_BASE = 0x7001B000 , I2C5_BASE = 0x7000D000 , I2S_BASE = 0x702d1000 } |

| enum | { UP_TAG_AVP = 0xaaaaaaaa } |

| enum | { PP_CONFIG_CTL_TBE = 0x1 << 7 , PP_CONFIG_CTL_JTAG = 0x1 << 6 } |

| enum | { CFG2TMC_RAM_SVOP_PDP_MASK = 0x3 << 24 , CFG2TMC_RAM_SVOP_PDP_VAL_2 = 0x2 << 24 } |

| enum | { E_INPUT = 1 << 6 , TRISTATE = 1 << 4 , PM_CLDVFS = 1 , PM_I2CPMU = 0 } |

| enum | { SWR_TRIG_SYS_RST = 0x1 << 2 } |

| enum | { CCLKG_PLLP_BURST_POLICY = 0x20004444 } |

| enum | { CCLKLP_PLLP_BURST_POLICY = 0x20004444 } |

| enum | { SUPER_CDIV_ENB = 0x1 << 31 } |

| enum | { OSC_XOE = 0x1 << 0 , OSC_XOFS_SHIFT = 4 , OSC_XOFS_MASK = 0x3f << OSC_XOFS_SHIFT , OSC_FREQ_SHIFT = 28 , OSC_FREQ_MASK = 0xf << OSC_FREQ_SHIFT } |

| enum | { PLLX_ENABLE = 0x1 << 30 } |

| enum | { I2C5_CLK_DIVISOR = 4 } |

| enum | { I2C5_RST = 0x1 << 15 } |

| enum | { SWR_CSITE_RST = 0x1 << 9 } |

| enum | { MSELECT_RST = 0x1 << 3 } |

| enum | { CLK_ENB_CPU = 0x1 << 0 } |

| enum | { CLK_ENB_I2C5 = 0x1 << 15 } |

| enum | { CLK_ENB_CSITE = 0x1 << 9 } |

| enum | { CAR2PMC_CPU_ACK_WIDTH_SHIFT = 0 , CAR2PMC_CPU_ACK_WIDTH_MASK = 0xfff << CAR2PMC_CPU_ACK_WIDTH_SHIFT } |

| enum | { CLK_ENB_CPUG = 0x1 << 0 } |

| enum | { CLK_ENB_PLLP_OUT_CPU = 0x1 << 31 } |

| enum | { CLR_CPURESET0 = 0x1 << 0 , CLR_CPURESET1 = 0x1 << 1 , CLR_CPURESET2 = 0x1 << 2 , CLR_CPURESET3 = 0x1 << 3 , CLR_DBGRESET0 = 0x1 << 12 , CLR_DBGRESET1 = 0x1 << 13 , CLR_DBGRESET2 = 0x1 << 14 , CLR_DBGRESET3 = 0x1 << 15 , CLR_CORERESET0 = 0x1 << 16 , CLR_CORERESET1 = 0x1 << 17 , CLR_CORERESET2 = 0x1 << 18 , CLR_CORERESET3 = 0x1 << 19 , CLR_CXRESET0 = 0x1 << 20 , CLR_CXRESET1 = 0x1 << 21 , CLR_CXRESET2 = 0x1 << 22 , CLR_CXRESET3 = 0x1 << 23 , CLR_L2RESET = 0x1 << 24 , CLR_NONCPURESET = 0x1 << 29 , CLR_PRESETDBG = 0x1 << 30 } |

| enum | { CLK_M_DIVISOR_MASK = 0x3 << 2 , CLK_M_DIVISOR_BY_2 = 0x1 << 2 } |

| enum | { CLK_ENB_MSELECT = 0x1 << 3 } |

| enum | { CLK_ENB_MC1 = 0x1 << 30 , CLK_ENB_DVFS = 0x1 << 27 } |

| enum | { CLK_SRC_PLLP_OUT0 = (0x0 << 29) , MSELECT_CLK_DIVISOR_4 = 6 } |

| enum | { DVFS_REF_CLK_DIVISOR = 0xe } |

| enum | { DVFS_SOC_CLK_DIVISOR = 0xe } |

| enum | { EVENT_MSEC = 0x1 << 24 , EVENT_JTAG = 0x1 << 28 , FLOW_MODE_SHIFT = 29 , FLOW_MODE_STOP = 2 << FLOW_MODE_SHIFT } |

| enum | { RAM_REPAIR_REQ = 0x1 << 0 , RAM_REPAIR_STS = 0x1 << 1 } |

| enum | { ACTIVE_SLOW = 0x1 << 0 } |

| enum | { PARTID_CRAIL = 0 , PARTID_CE1 = 9 , PARTID_CE2 = 10 , PARTID_CE3 = 11 , PARTID_CE0 = 14 , PARTID_C0NC = 15 } |

| enum | { PWRGATE_TOGGLE_START = 0x1 << 8 } |

| enum | { PMC_WAKEUP_CLUSTER_LPCPU = 1 << 31 } |

| enum | { PMIC_77621 = 0x1 << 1 } |

| enum | { PMC_XOFS_SHIFT = 1 , PMC_XOFS_MASK = 0x3f << PMC_XOFS_SHIFT } |

| enum | { HDA_LPBK_DIS = 1 << 0 } |

| enum | { VPR_WR_ACCESS_DISABLE = 0x1 << 0 , VPR_ALLOW_TZ_WR_ACCESS = 0x1 << 1 } |

| enum | { SECURITY_MODE = 0x1 << 0 } |

| enum | { SECURE_BOOT_DEBUG_CONFIG = 0x1 << 3 } |

| enum | { DISABLE_CFG_BYTE0 = 0x1 << 16 , DISABLE_CFG_BYTE1 = 0x1 << 17 , DISABLE_CFG_BYTE2 = 0x1 << 18 , DISABLE_CFG_BYTE3 = 0x1 << 19 , DISABLE_CFG_BYTE4 = 0x1 << 20 , DISABLE_CFG_BYTE5 = 0x1 << 21 , DISABLE_CFG_BYTE6 = 0x1 << 22 , DISABLE_CFG_BYTE7 = 0x1 << 23 , DISABLE_CFG_BYTES = 0xff << 16 , ENABLE_CFG_BYTES = 0 << 16 , DISABLE_CFG_CMD0 = 0x1 << 24 , DISABLE_CFG_CMD1 = 0x1 << 25 , DISABLE_CFG_CMD2 = 0x1 << 26 , DISABLE_CFG_CMD3 = 0x1 << 27 } |

| enum | { TRAINING_E_WRPTR = 0x1 << 3 } |

| enum | { CH1_ENABLE = 0x1 << 2 } |

| enum | { I2C_DEBOUNCE_CNT_4 = 2 << 12 , I2C_NEW_MASTER_FSM = 1 << 11 , I2C_SEND = 1 << 9 , I2C_LENGTH_2_BYTES = 1 << 1 } |

| enum | { I2C_STATUS_BUSY = 1 << 8 , I2C_STATUS_CMD1_STAT_MASK = 0xf << 0 , I2C_STATUS_CMD1_XFER_SUCCESS = 0 << 0 } |

| enum | { MSTR_CONFIG_LOAD = 1 << 0 } |

| enum | { UART_THR_DLAB = 0x0 , UART_IER_DLAB = 0x1 , UART_IIR_FCR = 0x2 , UART_LCR = 0x3 } |

| enum | { UART_RATE_115200 = (408000000/115200/16) , FCR_TX_CLR = 0x4 , FCR_RX_CLR = 0x2 , FCR_EN_FIFO = 0x1 , LCR_DLAB = 0x80 , LCR_WD_SIZE_8 = 0x3 } |

| enum | { SDMMC1_DEV_L = 0x1 << 14 , SDMMC3_DEV_U = 0x1 << 5 , PAD_E_INPUT_COMPPADCTRL = 0x1 << 31 , SEL_VREG_VENDOR_IO_TRIM = 0x1 << 2 } |

Functions | |

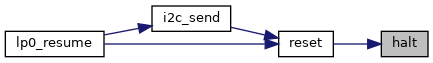

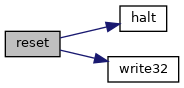

| static __always_inline void __noreturn | halt (void) |

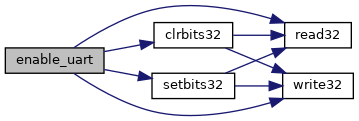

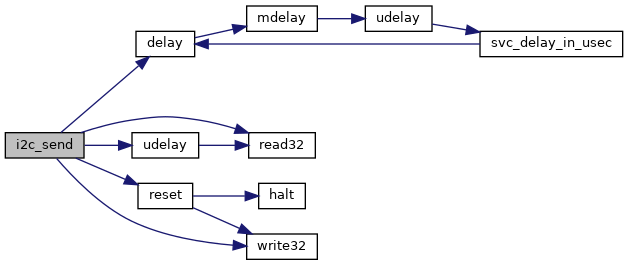

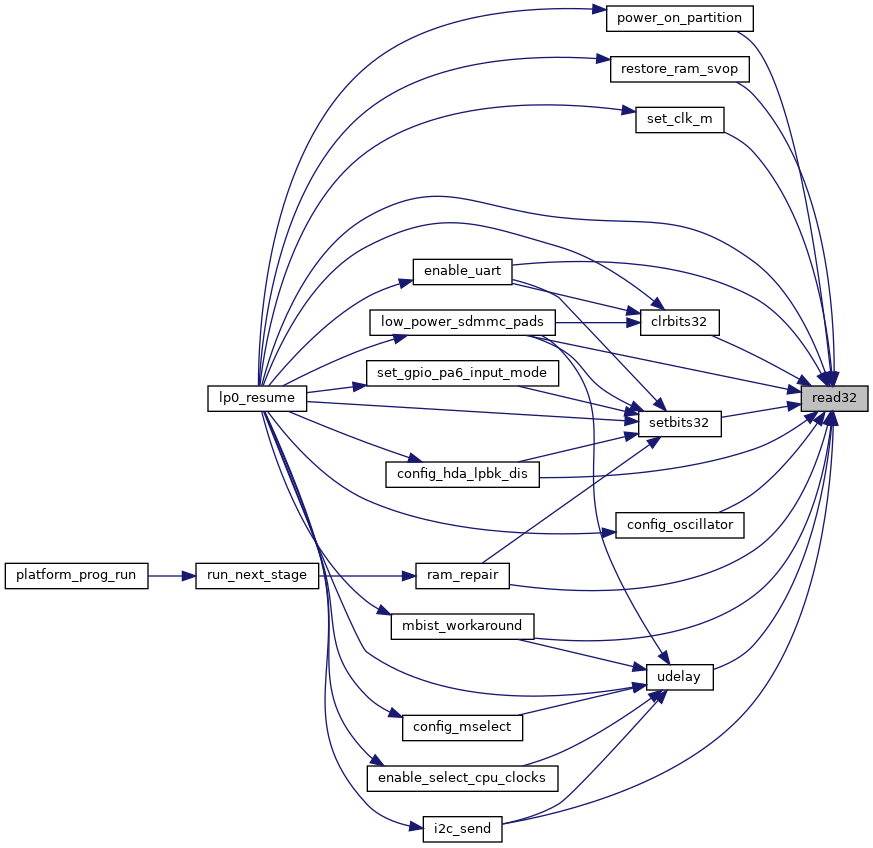

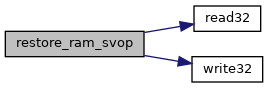

| static uint32_t | read32 (const void *addr) |

| static void | write32 (void *addr, uint32_t val) |

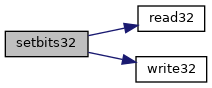

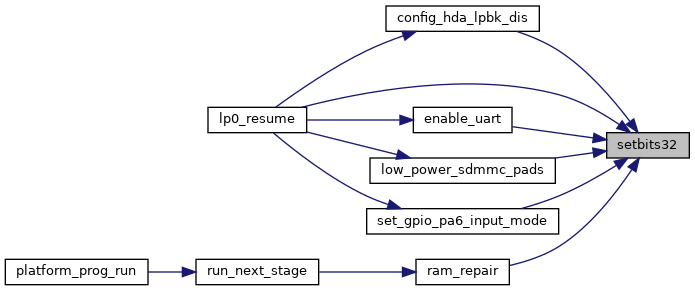

| static void | setbits32 (uint32_t bits, void *addr) |

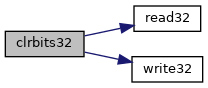

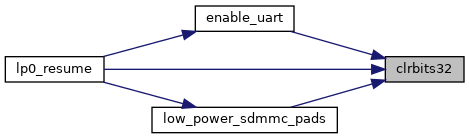

| static void | clrbits32 (uint32_t bits, void *addr) |

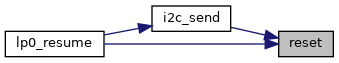

| static void __noreturn | reset (void) |

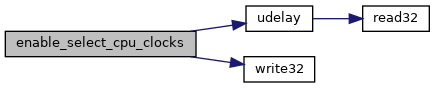

| static void | udelay (unsigned int usecs) |

| static void | enable_uart (void) |

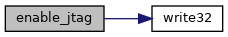

| static void | enable_jtag (void) |

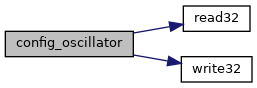

| static void | config_oscillator (void) |

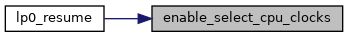

| static void | enable_select_cpu_clocks (void) |

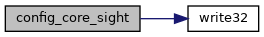

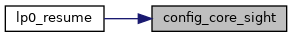

| static void | config_core_sight (void) |

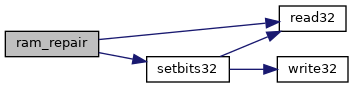

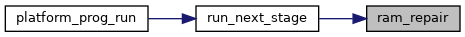

| void | ram_repair (void) |

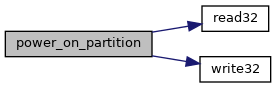

| static void | power_on_partition (unsigned int id) |

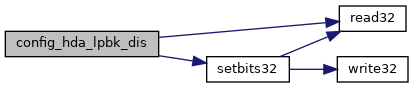

| static void | config_hda_lpbk_dis (void) |

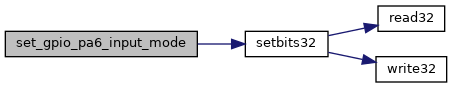

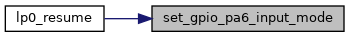

| static void | set_gpio_pa6_input_mode (void) |

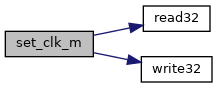

| static void | set_clk_m (void) |

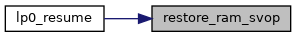

| static void | restore_ram_svop (void) |

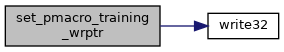

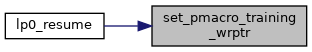

| static void | set_pmacro_training_wrptr (void) |

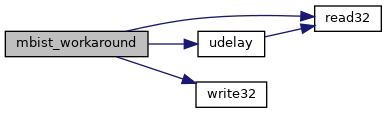

| static void | mbist_workaround (void) |

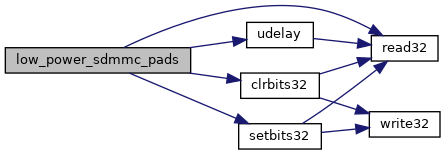

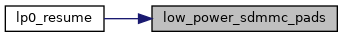

| static void | low_power_sdmmc_pads (void) |

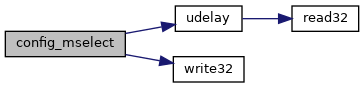

| static void | config_mselect (void) |

| static void | i2c_send (uint32_t addr, uint32_t data) |

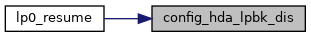

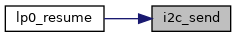

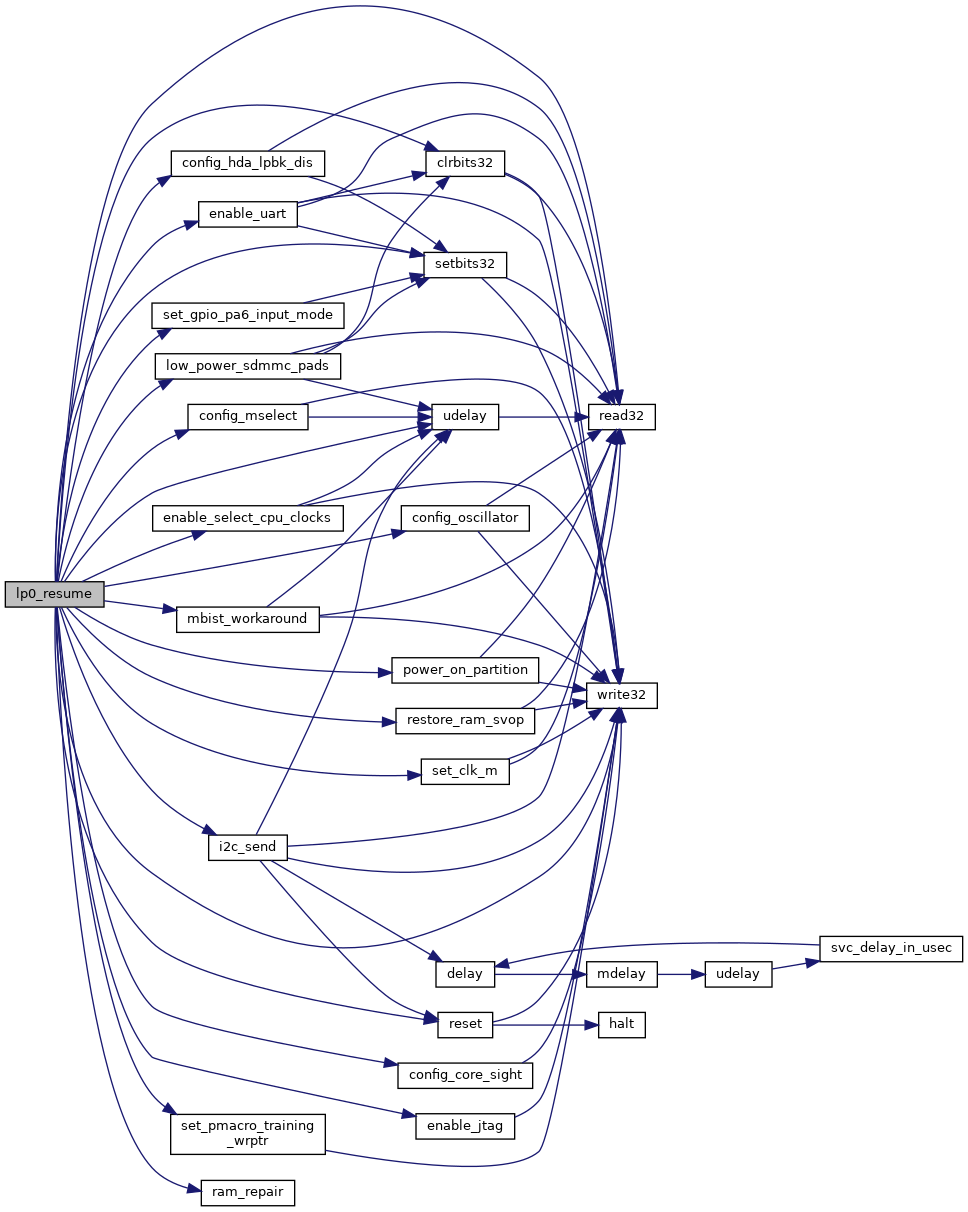

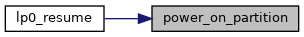

| void | lp0_resume (void) |

| #define MAX77620_GPIO5_DATA (0x3b | (0x9 << 8)) |

Definition at line 399 of file tegra_lp0_resume.c.

| #define MAX77620_I2C_ADDR (0x3c << 1) |

Definition at line 398 of file tegra_lp0_resume.c.

| #define MAX77621_I2C_ADDR (0x1b << 1) |

Definition at line 401 of file tegra_lp0_resume.c.

| #define MAX77621_VOUT_DATA (MAX77621_VOUT_REG | (MAX77621_VOUT_VAL << 8)) |

Definition at line 404 of file tegra_lp0_resume.c.

| #define MAX77621_VOUT_REG 0x0 |

Definition at line 402 of file tegra_lp0_resume.c.

| #define MAX77621_VOUT_VAL (0x80 | 0x27) |

Definition at line 403 of file tegra_lp0_resume.c.

| #define MBIST_CLK_ENB_H_0 0x020000C1 |

Definition at line 205 of file tegra_lp0_resume.c.

| #define MBIST_CLK_ENB_L_0 0x80000130 |

Definition at line 204 of file tegra_lp0_resume.c.

| #define MBIST_CLK_ENB_U_0 0x01F00200 |

Definition at line 206 of file tegra_lp0_resume.c.

| #define MBIST_CLK_ENB_V_0 0x80400008 |

Definition at line 207 of file tegra_lp0_resume.c.

| #define MBIST_CLK_ENB_W_0 0x002000FC |

Definition at line 208 of file tegra_lp0_resume.c.

| #define MBIST_CLK_ENB_X_0 0x23004780 |

Definition at line 209 of file tegra_lp0_resume.c.

| #define MBIST_CLK_ENB_Y_0 0x00000300 |

Definition at line 210 of file tegra_lp0_resume.c.

| anonymous enum |

Definition at line 4 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| UP_TAG_AVP | |

Definition at line 25 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| PP_CONFIG_CTL_TBE | |

| PP_CONFIG_CTL_JTAG | |

Definition at line 31 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CFG2TMC_RAM_SVOP_PDP_MASK | |

| CFG2TMC_RAM_SVOP_PDP_VAL_2 | |

Definition at line 37 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| E_INPUT | |

| TRISTATE | |

| PM_CLDVFS | |

| PM_I2CPMU | |

Definition at line 47 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| SWR_TRIG_SYS_RST | |

Definition at line 60 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CCLKG_PLLP_BURST_POLICY | |

Definition at line 67 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CCLKLP_PLLP_BURST_POLICY | |

Definition at line 72 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| SUPER_CDIV_ENB | |

Definition at line 78 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| OSC_XOE | |

| OSC_XOFS_SHIFT | |

| OSC_XOFS_MASK | |

| OSC_FREQ_SHIFT | |

| OSC_FREQ_MASK | |

Definition at line 83 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| PLLX_ENABLE | |

Definition at line 92 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| I2C5_CLK_DIVISOR | |

Definition at line 97 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| I2C5_RST | |

Definition at line 102 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| SWR_CSITE_RST | |

Definition at line 109 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| MSELECT_RST | |

Definition at line 114 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CLK_ENB_CPU | |

Definition at line 119 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CLK_ENB_I2C5 | |

Definition at line 124 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CLK_ENB_CSITE | |

Definition at line 130 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CAR2PMC_CPU_ACK_WIDTH_SHIFT | |

| CAR2PMC_CPU_ACK_WIDTH_MASK | |

Definition at line 136 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CLK_ENB_CPUG | |

Definition at line 142 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CLK_ENB_PLLP_OUT_CPU | |

Definition at line 147 of file tegra_lp0_resume.c.

| anonymous enum |

Definition at line 153 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CLK_M_DIVISOR_MASK | |

| CLK_M_DIVISOR_BY_2 | |

Definition at line 177 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CLK_ENB_MSELECT | |

Definition at line 213 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CLK_ENB_MC1 | |

| CLK_ENB_DVFS | |

Definition at line 218 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CLK_SRC_PLLP_OUT0 | |

| MSELECT_CLK_DIVISOR_4 | |

Definition at line 224 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| DVFS_REF_CLK_DIVISOR | |

Definition at line 230 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| DVFS_SOC_CLK_DIVISOR | |

Definition at line 235 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| EVENT_MSEC | |

| EVENT_JTAG | |

| FLOW_MODE_SHIFT | |

| FLOW_MODE_STOP | |

Definition at line 242 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| RAM_REPAIR_REQ | |

| RAM_REPAIR_STS | |

Definition at line 253 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| ACTIVE_SLOW | |

Definition at line 260 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| PARTID_CRAIL | |

| PARTID_CE1 | |

| PARTID_CE2 | |

| PARTID_CE3 | |

| PARTID_CE0 | |

| PARTID_C0NC | |

Definition at line 265 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| PWRGATE_TOGGLE_START | |

Definition at line 278 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| PMC_WAKEUP_CLUSTER_LPCPU | |

Definition at line 291 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| PMIC_77621 | |

Definition at line 299 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| PMC_XOFS_SHIFT | |

| PMC_XOFS_MASK | |

Definition at line 307 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| HDA_LPBK_DIS | |

Definition at line 313 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| VPR_WR_ACCESS_DISABLE | |

| VPR_ALLOW_TZ_WR_ACCESS | |

Definition at line 326 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| SECURITY_MODE | |

Definition at line 332 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| SECURE_BOOT_DEBUG_CONFIG | |

Definition at line 338 of file tegra_lp0_resume.c.

| anonymous enum |

Definition at line 347 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| TRAINING_E_WRPTR | |

Definition at line 366 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| CH1_ENABLE | |

Definition at line 371 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| I2C_DEBOUNCE_CNT_4 | |

| I2C_NEW_MASTER_FSM | |

| I2C_SEND | |

| I2C_LENGTH_2_BYTES | |

Definition at line 377 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| I2C_STATUS_BUSY | |

| I2C_STATUS_CMD1_STAT_MASK | |

| I2C_STATUS_CMD1_XFER_SUCCESS | |

Definition at line 387 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| MSTR_CONFIG_LOAD | |

Definition at line 394 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| UART_THR_DLAB | |

| UART_IER_DLAB | |

| UART_IIR_FCR | |

| UART_LCR | |

Definition at line 482 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| UART_RATE_115200 | |

| FCR_TX_CLR | |

| FCR_RX_CLR | |

| FCR_EN_FIFO | |

| LCR_DLAB | |

| LCR_WD_SIZE_8 | |

Definition at line 488 of file tegra_lp0_resume.c.

| anonymous enum |

| Enumerator | |

|---|---|

| SDMMC1_DEV_L | |

| SDMMC3_DEV_U | |

| PAD_E_INPUT_COMPPADCTRL | |

| SEL_VREG_VENDOR_IO_TRIM | |

Definition at line 796 of file tegra_lp0_resume.c.

Definition at line 428 of file tegra_lp0_resume.c.

References addr, read32(), and write32().

Referenced by enable_uart(), low_power_sdmmc_pads(), and lp0_resume().

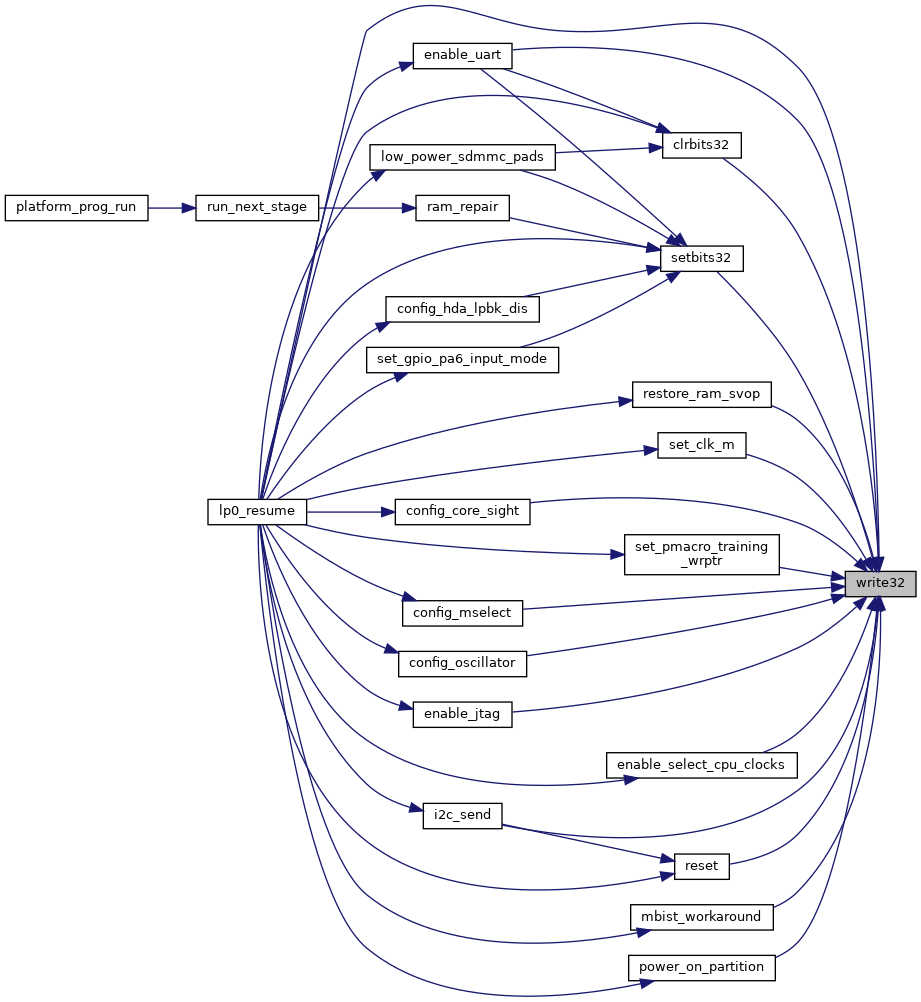

Definition at line 591 of file tegra_lp0_resume.c.

References CLK_ENB_CSITE, clk_rst_clk_out_enb_u_set_ptr, clk_rst_rst_dev_u_clr_ptr, SWR_CSITE_RST, and write32().

Referenced by lp0_resume().

Definition at line 635 of file tegra_lp0_resume.c.

References fuse_security_mode_ptr, HDA_LPBK_DIS, pmc_sticky_bits_ptr, read32(), SECURITY_MODE, and setbits32().

Referenced by lp0_resume().

Definition at line 834 of file tegra_lp0_resume.c.

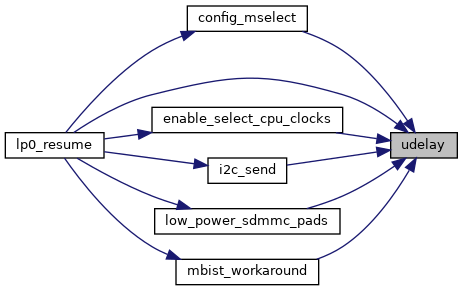

References CLK_ENB_MSELECT, clk_rst_clk_enb_v_ptr, clk_rst_clk_source_mselect_ptr, clk_rst_rst_dev_v_clr_ptr, CLK_SRC_PLLP_OUT0, MSELECT_CLK_DIVISOR_4, MSELECT_RST, udelay(), and write32().

Referenced by lp0_resume().

Definition at line 560 of file tegra_lp0_resume.c.

References clk_rst_osc_ctrl_ptr, OSC_XOE, OSC_XOFS_MASK, OSC_XOFS_SHIFT, pmc_osc_edpd_over_ptr, PMC_XOFS_MASK, PMC_XOFS_SHIFT, read32(), and write32().

Referenced by lp0_resume().

Definition at line 553 of file tegra_lp0_resume.c.

References misc_pp_config_ctl_ptr, PP_CONFIG_CTL_JTAG, and write32().

Referenced by lp0_resume().

Definition at line 576 of file tegra_lp0_resume.c.

References CCLKG_PLLP_BURST_POLICY, CCLKLP_PLLP_BURST_POLICY, CLK_ENB_CPU, CLK_ENB_CPUG, clk_rst_cclkg_burst_policy_ptr, clk_rst_cclklp_burst_policy_ptr, clk_rst_clk_enb_l_set_ptr, clk_rst_clk_enb_v_set_ptr, udelay(), and write32().

Referenced by lp0_resume().

Definition at line 497 of file tegra_lp0_resume.c.

References clrbits32(), FCR_EN_FIFO, FCR_RX_CLR, FCR_TX_CLR, LCR_DLAB, LCR_WD_SIZE_8, pmc_odmdata_ptr, read32(), setbits32(), uart_base_regs, uart_clk_out_enb_regs, uart_clk_source_regs, uart_enable_mask, UART_IER_DLAB, UART_IIR_FCR, UART_LCR, UART_RATE_115200, uart_rst_devices_regs, UART_THR_DLAB, and write32().

Referenced by lp0_resume().

|

static |

Definition at line 408 of file tegra_lp0_resume.c.

Referenced by reset().

Definition at line 847 of file tegra_lp0_resume.c.

References addr, delay(), i2c5_cmd_addr0_ptr, i2c5_cmd_data1_ptr, i2c5_cnfg_ptr, i2c5_config_load_ptr, i2c5_status_ptr, I2C_DEBOUNCE_CNT_4, I2C_LENGTH_2_BYTES, I2C_NEW_MASTER_FSM, I2C_SEND, I2C_STATUS_BUSY, I2C_STATUS_CMD1_STAT_MASK, MSTR_CONFIG_LOAD, read32(), reset(), udelay(), and write32().

Referenced by lp0_resume().

Definition at line 803 of file tegra_lp0_resume.c.

References clk_rst_clk_out_enb_l_ptr, clk_rst_clk_out_enb_u_ptr, clk_rst_rst_devices_l_ptr, clk_rst_rst_devices_u_ptr, clrbits32(), PAD_E_INPUT_COMPPADCTRL, read32(), sdmmc1_comppadctrl, SDMMC1_DEV_L, sdmmc1_vendor_io_trim, sdmmc3_comppadctrl, SDMMC3_DEV_U, sdmmc3_vendor_io_trim, SEL_VREG_VENDOR_IO_TRIM, setbits32(), and udelay().

Referenced by lp0_resume().

Definition at line 883 of file tegra_lp0_resume.c.

References ACTIVE_SLOW, CAR2PMC_CPU_ACK_WIDTH_MASK, CLK_ENB_DVFS, CLK_ENB_I2C5, CLK_ENB_PLLP_OUT_CPU, clk_rst_clk_dvfs_ref_ptr, clk_rst_clk_dvfs_soc_ptr, clk_rst_clk_enb_h_clr_ptr, clk_rst_clk_enb_h_set_ptr, clk_rst_clk_enb_w_clr_ptr, clk_rst_clk_enb_w_set_ptr, clk_rst_clk_enb_y_set_ptr, clk_rst_clk_source_i2c5_ptr, clk_rst_cpu_softrst_ctrl2_ptr, clk_rst_cpug_cmplx_clr_ptr, clk_rst_pllx_base_ptr, clk_rst_rst_dev_h_clr_ptr, clk_rst_rst_dev_h_set_ptr, clk_rst_super_cclkg_div_ptr, clk_rst_super_cclklp_div_ptr, CLK_SRC_PLLP_OUT0, CLR_CORERESET0, CLR_CPURESET0, CLR_NONCPURESET, clrbits32(), config_core_sight(), config_hda_lpbk_dis(), config_mselect(), config_oscillator(), DVFS_REF_CLK_DIVISOR, DVFS_SOC_CLK_DIVISOR, E_INPUT, enable_jtag(), enable_select_cpu_clocks(), enable_uart(), EVENT_JTAG, flow_ctlr_bpmp_cluster_control_ptr, flow_ctlr_halt_cop_events_ptr, FLOW_MODE_STOP, I2C5_CLK_DIVISOR, I2C5_RST, i2c_send(), low_power_sdmmc_pads(), MAX77620_GPIO5_DATA, MAX77620_I2C_ADDR, MAX77621_I2C_ADDR, MAX77621_VOUT_DATA, mbist_workaround(), mc_intmask_ptr, mc_intstatus_ptr, mc_video_protect_reg_ctrl_ptr, mc_video_protect_size_mb_ptr, PARTID_C0NC, PARTID_CE0, PARTID_CRAIL, pinmux_dvfs_pwm_ptr, pinmux_pwr_i2c_scl_ptr, pinmux_pwr_i2c_sda_ptr, PLLX_ENABLE, PM_CLDVFS, PM_I2CPMU, pmc_clamp_status_ptr, pmc_cpupwrgood_timer_ptr, pmc_dpd_sample_ptr, pmc_remove_clamping_cmd_ptr, pmc_scratch190_ptr, pmc_scratch201_ptr, pmc_scratch4_ptr, pmc_secure_scratch34_ptr, pmc_secure_scratch35_ptr, pmc_set_sw_clamp_ptr, PMC_WAKEUP_CLUSTER_LPCPU, PMIC_77621, power_on_partition(), ram_repair(), read32(), reset(), restore_ram_svop(), sb_aa64_reset_high, sb_aa64_reset_low, set_clk_m(), set_gpio_pa6_input_mode(), set_pmacro_training_wrptr(), setbits32(), SUPER_CDIV_ENB, TRISTATE, udelay(), UP_TAG_AVP, up_tag_ptr, VPR_ALLOW_TZ_WR_ACCESS, VPR_WR_ACCESS_DISABLE, and write32().

Definition at line 702 of file tegra_lp0_resume.c.

References CH1_ENABLE, CLK_ENB_MC1, clk_rst_ape_clear, clk_rst_clk_enb_h_clr_ptr, clk_rst_clk_enb_l_clr_ptr, clk_rst_clk_enb_u_clr_ptr, clk_rst_clk_enb_v_clr_ptr, clk_rst_clk_enb_w_clr_ptr, clk_rst_clk_enb_w_set_ptr, clk_rst_clk_enb_x_clr_ptr, clk_rst_clk_enb_y_clr_ptr, clk_rst_clk_out_enb_h_ptr, clk_rst_clk_out_enb_l_ptr, clk_rst_clk_out_enb_u_ptr, clk_rst_clk_out_enb_v_ptr, clk_rst_clk_out_enb_w_ptr, clk_rst_clk_out_enb_x_ptr, clk_rst_clk_out_enb_y_ptr, clk_rst_lvl2_clk_gate_ovra_ptr, clk_rst_lvl2_clk_gate_ovrb_ptr, clk_rst_lvl2_clk_gate_ovrc_ptr, clk_rst_lvl2_clk_gate_ovrd_ptr, clk_rst_lvl2_clk_gate_ovre_ptr, fbio_cfg7_ptr, i2s_0_master, i2s_0_slcg, i2s_1_master, i2s_1_slcg, i2s_2_master, i2s_2_slcg, i2s_3_master, i2s_3_slcg, i2s_4_master, i2s_4_slcg, MBIST_CLK_ENB_H_0, MBIST_CLK_ENB_L_0, MBIST_CLK_ENB_U_0, MBIST_CLK_ENB_V_0, MBIST_CLK_ENB_W_0, MBIST_CLK_ENB_X_0, MBIST_CLK_ENB_Y_0, read32(), udelay(), and write32().

Referenced by lp0_resume().

Definition at line 618 of file tegra_lp0_resume.c.

References pmc_clamp_status_ptr, pmc_pwrgate_status_ptr, pmc_pwrgate_toggle_ptr, PWRGATE_TOGGLE_START, read32(), and write32().

Referenced by lp0_resume().

Definition at line 607 of file tegra_lp0_resume.c.

References flow_ctlr_ram_repair_cluster1_ptr, flow_ctlr_ram_repair_ptr, RAM_REPAIR_REQ, RAM_REPAIR_STS, read32(), and setbits32().

Referenced by run_next_stage().

Definition at line 413 of file tegra_lp0_resume.c.

References addr.

Referenced by clrbits32(), config_hda_lpbk_dis(), config_oscillator(), enable_uart(), i2c_send(), low_power_sdmmc_pads(), lp0_resume(), mbist_workaround(), power_on_partition(), ram_repair(), restore_ram_svop(), set_clk_m(), setbits32(), and udelay().

|

static |

Definition at line 433 of file tegra_lp0_resume.c.

References clk_rst_rst_devices_l_ptr, halt(), SWR_TRIG_SYS_RST, and write32().

Referenced by i2c_send(), and lp0_resume().

Definition at line 664 of file tegra_lp0_resume.c.

References CFG2TMC_RAM_SVOP_PDP_MASK, CFG2TMC_RAM_SVOP_PDP_VAL_2, misc_gp_asdbgreg_ptr, read32(), and write32().

Referenced by lp0_resume().

Definition at line 647 of file tegra_lp0_resume.c.

References CLK_M_DIVISOR_BY_2, CLK_M_DIVISOR_MASK, clk_rst_spare_reg0_ptr, read32(), timer_us_cfg_ptr, and write32().

Referenced by lp0_resume().

Definition at line 642 of file tegra_lp0_resume.c.

References E_INPUT, pinmux_gpio_pa6_ptr, and setbits32().

Referenced by lp0_resume().

Definition at line 674 of file tegra_lp0_resume.c.

References DISABLE_CFG_BYTES, ENABLE_CFG_BYTES, pmacro_cfg_pm_global, pmacro_training_ctrl_0_ptr, pmacro_training_ctrl_1_ptr, TRAINING_E_WRPTR, and write32().

Referenced by lp0_resume().

Definition at line 423 of file tegra_lp0_resume.c.

References addr, read32(), and write32().

Referenced by config_hda_lpbk_dis(), enable_uart(), low_power_sdmmc_pads(), lp0_resume(), ram_repair(), and set_gpio_pa6_input_mode().

Definition at line 439 of file tegra_lp0_resume.c.

References read32(), and timer_us_ptr.

Referenced by config_mselect(), enable_select_cpu_clocks(), i2c_send(), low_power_sdmmc_pads(), lp0_resume(), and mbist_workaround().

Definition at line 418 of file tegra_lp0_resume.c.

Referenced by clrbits32(), config_core_sight(), config_mselect(), config_oscillator(), enable_jtag(), enable_select_cpu_clocks(), enable_uart(), i2c_send(), lp0_resume(), mbist_workaround(), power_on_partition(), reset(), restore_ram_svop(), set_clk_m(), set_pmacro_training_wrptr(), and setbits32().

| struct lp0_header __packed |

|

extern |

|

extern |

|

extern |

|

static |

Definition at line 699 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 700 of file tegra_lp0_resume.c.

|

static |

Definition at line 66 of file tegra_lp0_resume.c.

Referenced by enable_select_cpu_clocks().

|

static |

Definition at line 71 of file tegra_lp0_resume.c.

Referenced by enable_select_cpu_clocks().

|

static |

Definition at line 229 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 234 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 197 of file tegra_lp0_resume.c.

Referenced by lp0_resume(), and mbist_workaround().

|

static |

Definition at line 123 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 196 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 118 of file tegra_lp0_resume.c.

Referenced by enable_select_cpu_clocks().

|

static |

Definition at line 198 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 199 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 212 of file tegra_lp0_resume.c.

Referenced by config_mselect().

|

static |

Definition at line 141 of file tegra_lp0_resume.c.

Referenced by enable_select_cpu_clocks().

|

static |

Definition at line 200 of file tegra_lp0_resume.c.

Referenced by lp0_resume(), and mbist_workaround().

|

static |

Definition at line 217 of file tegra_lp0_resume.c.

Referenced by lp0_resume(), and mbist_workaround().

|

static |

Definition at line 201 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 202 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 146 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 189 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 188 of file tegra_lp0_resume.c.

Referenced by low_power_sdmmc_pads(), and mbist_workaround().

|

static |

Definition at line 190 of file tegra_lp0_resume.c.

Referenced by low_power_sdmmc_pads(), and mbist_workaround().

|

static |

Definition at line 128 of file tegra_lp0_resume.c.

Referenced by config_core_sight().

|

static |

Definition at line 191 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 192 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 193 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 194 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 96 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 223 of file tegra_lp0_resume.c.

Referenced by config_mselect().

|

static |

Definition at line 134 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 151 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 182 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 183 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 184 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 185 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 186 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 82 of file tegra_lp0_resume.c.

Referenced by config_oscillator().

|

static |

Definition at line 91 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 106 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 101 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 108 of file tegra_lp0_resume.c.

Referenced by config_core_sight().

|

static |

Definition at line 113 of file tegra_lp0_resume.c.

Referenced by config_mselect().

|

static |

Definition at line 59 of file tegra_lp0_resume.c.

Referenced by low_power_sdmmc_pads(), and reset().

|

static |

Definition at line 64 of file tegra_lp0_resume.c.

Referenced by low_power_sdmmc_pads().

|

static |

Definition at line 175 of file tegra_lp0_resume.c.

Referenced by set_clk_m().

|

static |

Definition at line 76 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 77 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

Definition at line 370 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 258 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 240 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 251 of file tegra_lp0_resume.c.

|

static |

Definition at line 249 of file tegra_lp0_resume.c.

Referenced by ram_repair().

Definition at line 331 of file tegra_lp0_resume.c.

Referenced by config_hda_lpbk_dis().

| struct lp0_header header |

Definition at line 1082 of file tegra_lp0_resume.c.

Definition at line 384 of file tegra_lp0_resume.c.

Referenced by i2c_send().

Definition at line 385 of file tegra_lp0_resume.c.

Referenced by i2c_send().

Definition at line 376 of file tegra_lp0_resume.c.

Referenced by i2c_send().

Definition at line 393 of file tegra_lp0_resume.c.

Referenced by i2c_send().

Definition at line 386 of file tegra_lp0_resume.c.

Referenced by i2c_send().

Definition at line 687 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

Definition at line 693 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

Definition at line 688 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

Definition at line 694 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

Definition at line 689 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

Definition at line 695 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

Definition at line 690 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

Definition at line 696 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

Definition at line 691 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

Definition at line 697 of file tegra_lp0_resume.c.

Referenced by mbist_workaround().

|

static |

Definition at line 321 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 320 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 324 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 322 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 36 of file tegra_lp0_resume.c.

Referenced by restore_ram_svop().

|

static |

Definition at line 30 of file tegra_lp0_resume.c.

Referenced by enable_jtag().

|

static |

Definition at line 45 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 46 of file tegra_lp0_resume.c.

Referenced by set_gpio_pa6_input_mode().

|

static |

Definition at line 43 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 44 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

Definition at line 346 of file tegra_lp0_resume.c.

Referenced by set_pmacro_training_wrptr().

Definition at line 364 of file tegra_lp0_resume.c.

Referenced by set_pmacro_training_wrptr().

Definition at line 365 of file tegra_lp0_resume.c.

Referenced by set_pmacro_training_wrptr().

|

static |

Definition at line 275 of file tegra_lp0_resume.c.

Referenced by lp0_resume(), and power_on_partition().

|

static |

Definition at line 286 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 274 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 288 of file tegra_lp0_resume.c.

Referenced by enable_uart().

|

static |

Definition at line 306 of file tegra_lp0_resume.c.

Referenced by config_oscillator().

|

static |

Definition at line 284 of file tegra_lp0_resume.c.

Referenced by power_on_partition().

|

static |

Definition at line 277 of file tegra_lp0_resume.c.

Referenced by power_on_partition().

|

static |

Definition at line 282 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 295 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 298 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 290 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 303 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 304 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 317 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 312 of file tegra_lp0_resume.c.

Referenced by config_hda_lpbk_dis().

|

static |

Definition at line 343 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 342 of file tegra_lp0_resume.c.

Referenced by lp0_resume().

|

static |

Definition at line 337 of file tegra_lp0_resume.c.

|

static |

Definition at line 793 of file tegra_lp0_resume.c.

Referenced by low_power_sdmmc_pads().

|

static |

Definition at line 791 of file tegra_lp0_resume.c.

Referenced by low_power_sdmmc_pads().

|

static |

Definition at line 794 of file tegra_lp0_resume.c.

Referenced by low_power_sdmmc_pads().

|

static |

Definition at line 792 of file tegra_lp0_resume.c.

Referenced by low_power_sdmmc_pads().

|

static |

Definition at line 56 of file tegra_lp0_resume.c.

Referenced by set_clk_m().

|

static |

Definition at line 55 of file tegra_lp0_resume.c.

Referenced by udelay().

|

static |

Definition at line 475 of file tegra_lp0_resume.c.

Referenced by enable_uart().

|

static |

Definition at line 447 of file tegra_lp0_resume.c.

Referenced by enable_uart().

|

static |

Definition at line 468 of file tegra_lp0_resume.c.

Referenced by enable_uart().

|

static |

Definition at line 461 of file tegra_lp0_resume.c.

Referenced by enable_uart().

|

static |

Definition at line 454 of file tegra_lp0_resume.c.

Referenced by enable_uart().

|

static |

Definition at line 24 of file tegra_lp0_resume.c.

Referenced by lp0_resume().