|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

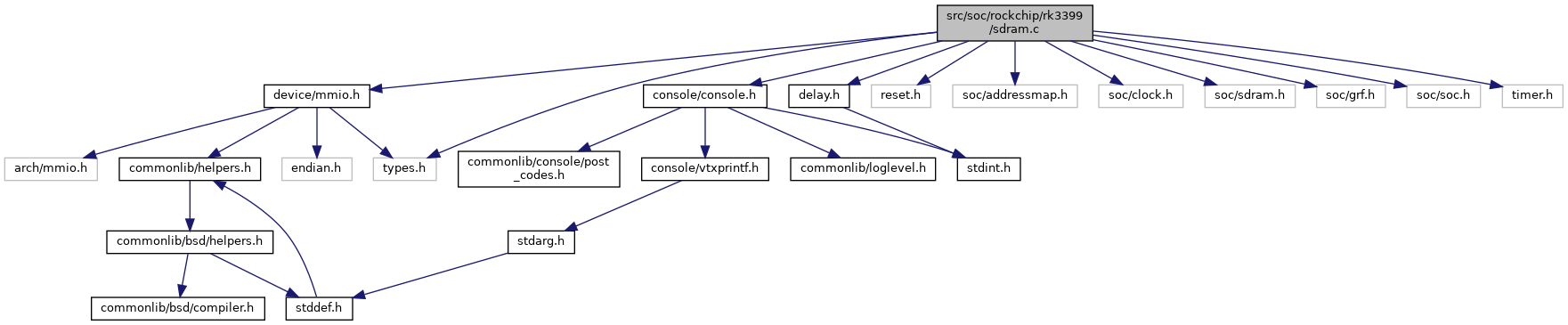

#include <device/mmio.h>#include <console/console.h>#include <delay.h>#include <reset.h>#include <soc/addressmap.h>#include <soc/clock.h>#include <soc/sdram.h>#include <soc/grf.h>#include <soc/soc.h>#include <timer.h>#include <types.h>

Go to the source code of this file.

Macros | |

| #define | DDR_PI_OFFSET 0x800 |

| #define | DDR_PHY_OFFSET 0x2000 |

| #define | DDRC0_PI_BASE_ADDR (DDRC0_BASE_ADDR + DDR_PI_OFFSET) |

| #define | DDRC0_PHY_BASE_ADDR (DDRC0_BASE_ADDR + DDR_PHY_OFFSET) |

| #define | DDRC1_PI_BASE_ADDR (DDRC1_BASE_ADDR + DDR_PI_OFFSET) |

| #define | DDRC1_PHY_BASE_ADDR (DDRC1_BASE_ADDR + DDR_PHY_OFFSET) |

| #define | SYS_REG_ENC_ROW_3_4(n, ch) ((n) << (30 + (ch))) |

| #define | SYS_REG_DEC_ROW_3_4(n, ch) ((n >> (30 + ch)) & 0x1) |

| #define | SYS_REG_ENC_CHINFO(ch) (1 << (28 + (ch))) |

| #define | SYS_REG_ENC_DDRTYPE(n) ((n) << 13) |

| #define | SYS_REG_ENC_NUM_CH(n) (((n) - 1) << 12) |

| #define | SYS_REG_DEC_NUM_CH(n) (1 + ((n >> 12) & 0x1)) |

| #define | SYS_REG_ENC_RANK(n, ch) (((n) - 1) << (11 + ((ch) * 16))) |

| #define | SYS_REG_DEC_RANK(n, ch) (1 + ((n >> (11 + 16 * ch)) & 0x1)) |

| #define | SYS_REG_ENC_COL(n, ch) (((n) - 9) << (9 + ((ch) * 16))) |

| #define | SYS_REG_DEC_COL(n, ch) (9 + ((n >> (9 + 16 * ch)) & 0x3)) |

| #define | SYS_REG_ENC_BK(n, ch) |

| #define | SYS_REG_DEC_BK(n, ch) (3 - ((n >> (8 + 16 * ch)) & 0x1)) |

| #define | SYS_REG_ENC_CS0_ROW(n, ch) (((n) - 13) << (6 + ((ch) * 16))) |

| #define | SYS_REG_DEC_CS0_ROW(n, ch) (13 + ((n >> (6 + 16 * ch)) & 0x3)) |

| #define | SYS_REG_ENC_CS1_ROW(n, ch) (((n) - 13) << (4 + ((ch) * 16))) |

| #define | SYS_REG_DEC_CS1_ROW(n, ch) (13 + ((n >> (4 + 16 * ch)) & 0x3)) |

| #define | SYS_REG_ENC_BW(n, ch) ((2 >> (n)) << (2 + ((ch) * 16))) |

| #define | SYS_REG_DEC_BW(n, ch) (2 >> ((n >> (2 + 16 * ch)) & 0x3)) |

| #define | SYS_REG_ENC_DBW(n, ch) ((2 >> (n)) << (0 + ((ch) * 16))) |

| #define | SYS_REG_DEC_DBW(n, ch) (2 >> ((n >> (0 + 16 * ch)) & 0x3)) |

| #define | DDR_STRIDE(n) |

| #define | PRESET_SGRF_HOLD(n) ((0x1 << (6+16)) | ((n) << 6)) |

| #define | PRESET_GPIO0_HOLD(n) ((0x1 << (7+16)) | ((n) << 7)) |

| #define | PRESET_GPIO1_HOLD(n) ((0x1 << (8+16)) | ((n) << 8)) |

| #define | PHY_DRV_ODT_Hi_Z (0x0) |

| #define | PHY_DRV_ODT_240 (0x1) |

| #define | PHY_DRV_ODT_120 (0x8) |

| #define | PHY_DRV_ODT_80 (0x9) |

| #define | PHY_DRV_ODT_60 (0xc) |

| #define | PHY_DRV_ODT_48 (0xd) |

| #define | PHY_DRV_ODT_40 (0xe) |

| #define | PHY_DRV_ODT_34_3 (0xf) |

| #define | MAX_RANKS_PER_CHANNEL 4 |

Variables | |

| static struct rk3399_ddr_pctl_regs *const | rk3399_ddr_pctl [2] |

| static struct rk3399_ddr_pi_regs *const | rk3399_ddr_pi [2] |

| static struct rk3399_ddr_publ_regs *const | rk3399_ddr_publ [2] |

| static struct rk3399_msch_regs *const | rk3399_msch [2] |

| static struct rk3399_ddr_cic_regs *const | rk3399_ddr_cic = (void *)CIC_BASE_ADDR |

| #define DDR_STRIDE | ( | n | ) |

| #define DDRC0_PHY_BASE_ADDR (DDRC0_BASE_ADDR + DDR_PHY_OFFSET) |

| #define DDRC0_PI_BASE_ADDR (DDRC0_BASE_ADDR + DDR_PI_OFFSET) |

| #define DDRC1_PHY_BASE_ADDR (DDRC1_BASE_ADDR + DDR_PHY_OFFSET) |

| #define DDRC1_PI_BASE_ADDR (DDRC1_BASE_ADDR + DDR_PI_OFFSET) |

| #define PRESET_GPIO0_HOLD | ( | n | ) | ((0x1 << (7+16)) | ((n) << 7)) |

| #define PRESET_GPIO1_HOLD | ( | n | ) | ((0x1 << (8+16)) | ((n) << 8)) |

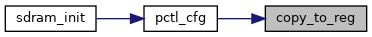

Definition at line 94 of file sdram.c.

References write32().

Referenced by pctl_cfg().

|

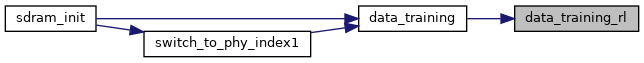

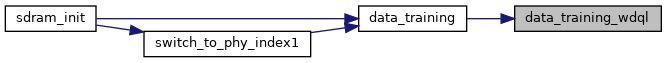

static |

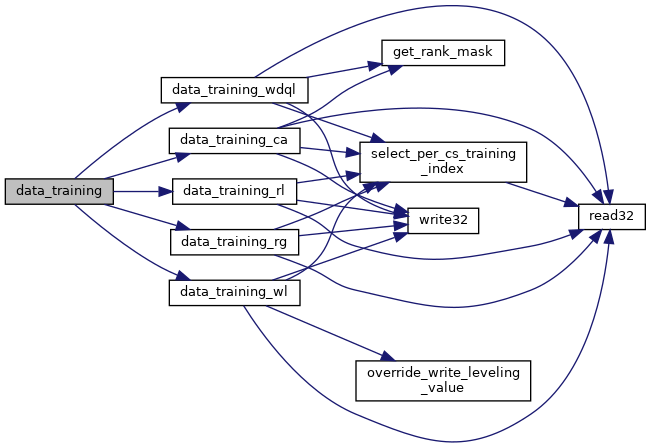

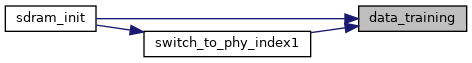

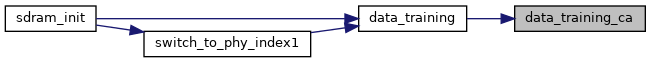

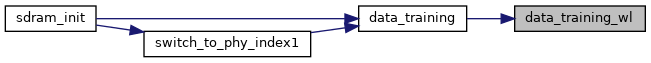

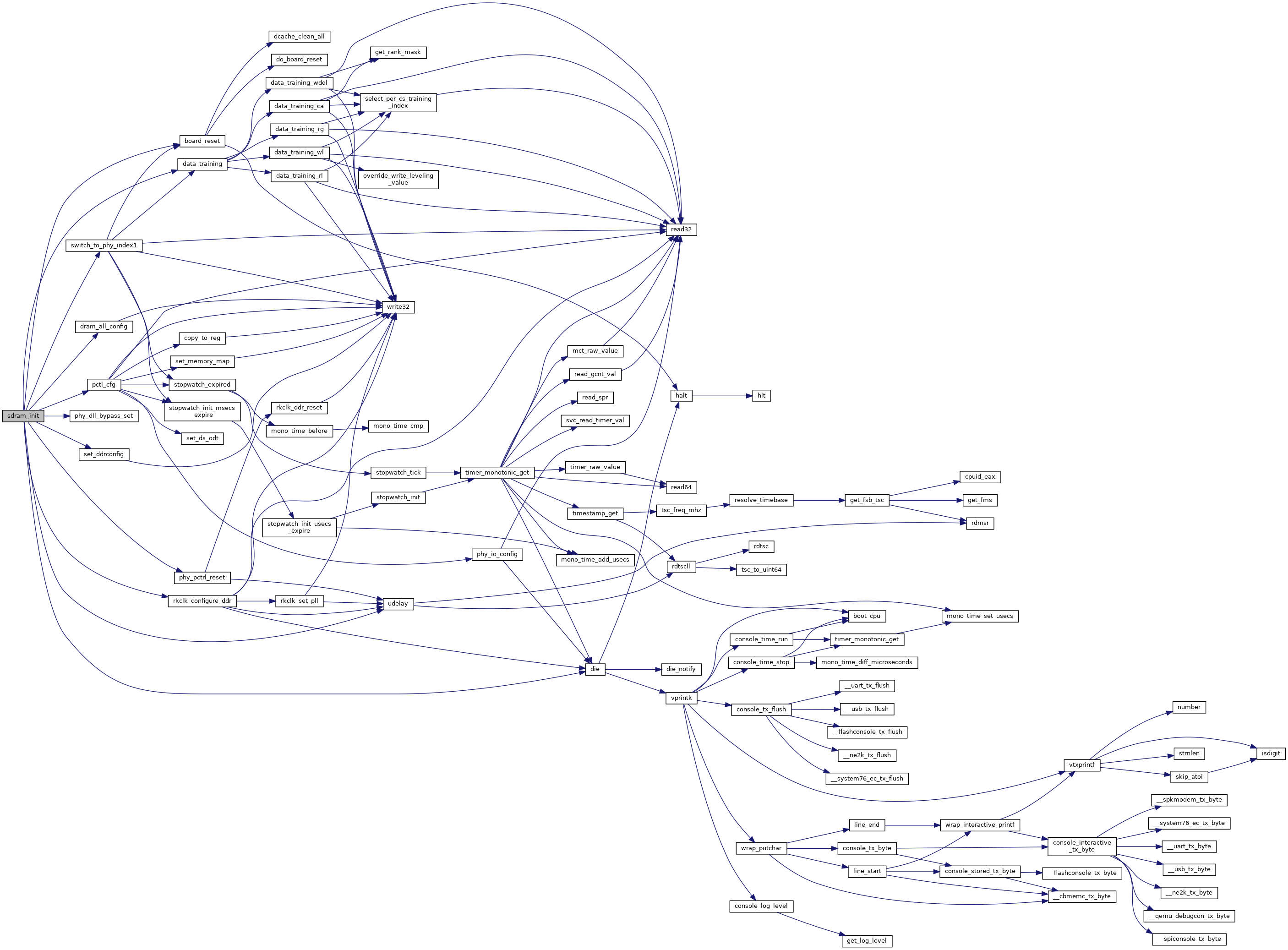

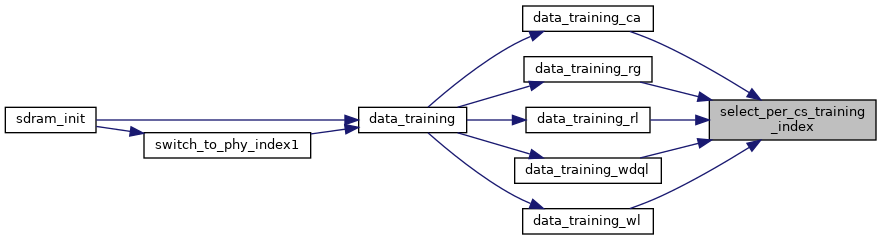

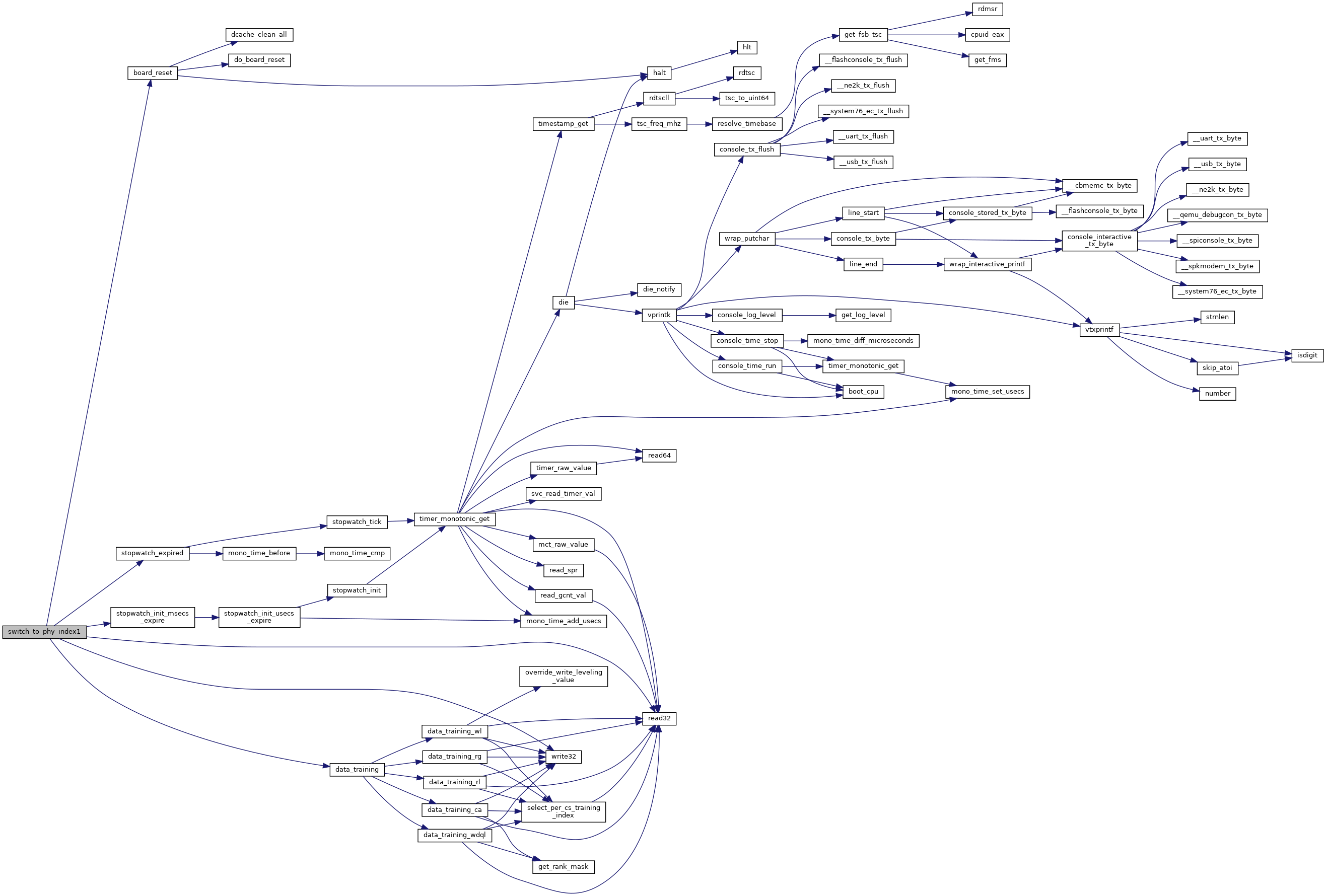

Definition at line 914 of file sdram.c.

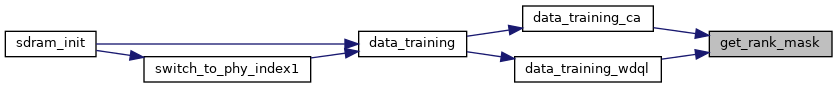

References BIOS_ERR, clrbits32, data_training_ca(), data_training_rg(), data_training_rl(), data_training_wdql(), data_training_wl(), DDR3, rk3399_ddr_publ_regs::denali_phy, LPDDR3, LPDDR4, params, PI_CA_TRAINING, PI_FULL_TRAINING, PI_READ_GATE_TRAINING, PI_READ_LEVELING, PI_WDQ_LEVELING, PI_WRITE_LEVELING, printk, rk3399_ddr_publ, and setbits32.

Referenced by sdram_init(), and switch_to_phy_index1().

|

static |

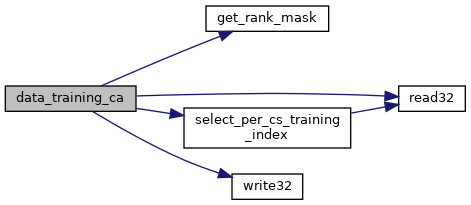

Definition at line 638 of file sdram.c.

References clrbits32, clrsetbits32, rk3399_ddr_publ_regs::denali_phy, rk3399_ddr_pi_regs::denali_pi, get_rank_mask(), MAX_RANKS_PER_CHANNEL, params, read32(), rk3399_ddr_pi, rk3399_ddr_publ, select_per_cs_training_index(), and write32().

Referenced by data_training().

|

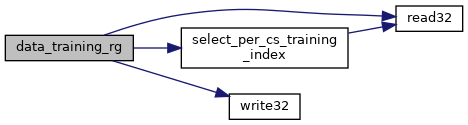

static |

Definition at line 743 of file sdram.c.

References clrbits32, clrsetbits32, rk3399_ddr_publ_regs::denali_phy, rk3399_ddr_pi_regs::denali_pi, LPDDR4, params, read32(), rk3399_ddr_pi, rk3399_ddr_publ, select_per_cs_training_index(), and write32().

Referenced by data_training().

|

static |

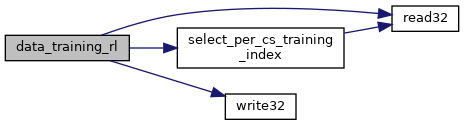

Definition at line 832 of file sdram.c.

References clrbits32, clrsetbits32, rk3399_ddr_pi_regs::denali_pi, params, read32(), rk3399_ddr_pi, select_per_cs_training_index(), and write32().

Referenced by data_training().

|

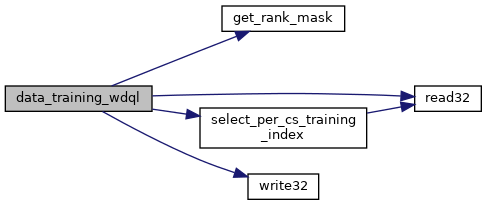

static |

Definition at line 872 of file sdram.c.

References clrbits32, clrsetbits32, rk3399_ddr_pi_regs::denali_pi, get_rank_mask(), MAX_RANKS_PER_CHANNEL, params, read32(), rk3399_ddr_pi, select_per_cs_training_index(), and write32().

Referenced by data_training().

|

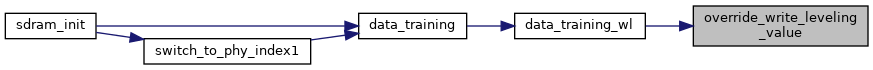

static |

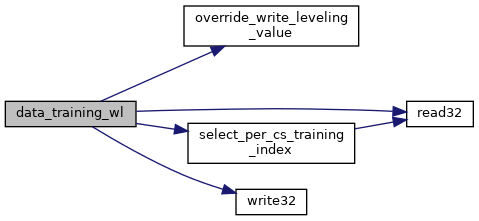

Definition at line 690 of file sdram.c.

References clrbits32, clrsetbits32, rk3399_ddr_publ_regs::denali_phy, rk3399_ddr_pi_regs::denali_pi, override_write_leveling_value(), params, read32(), rk3399_ddr_pi, rk3399_ddr_publ, select_per_cs_training_index(), and write32().

Referenced by data_training().

|

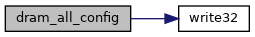

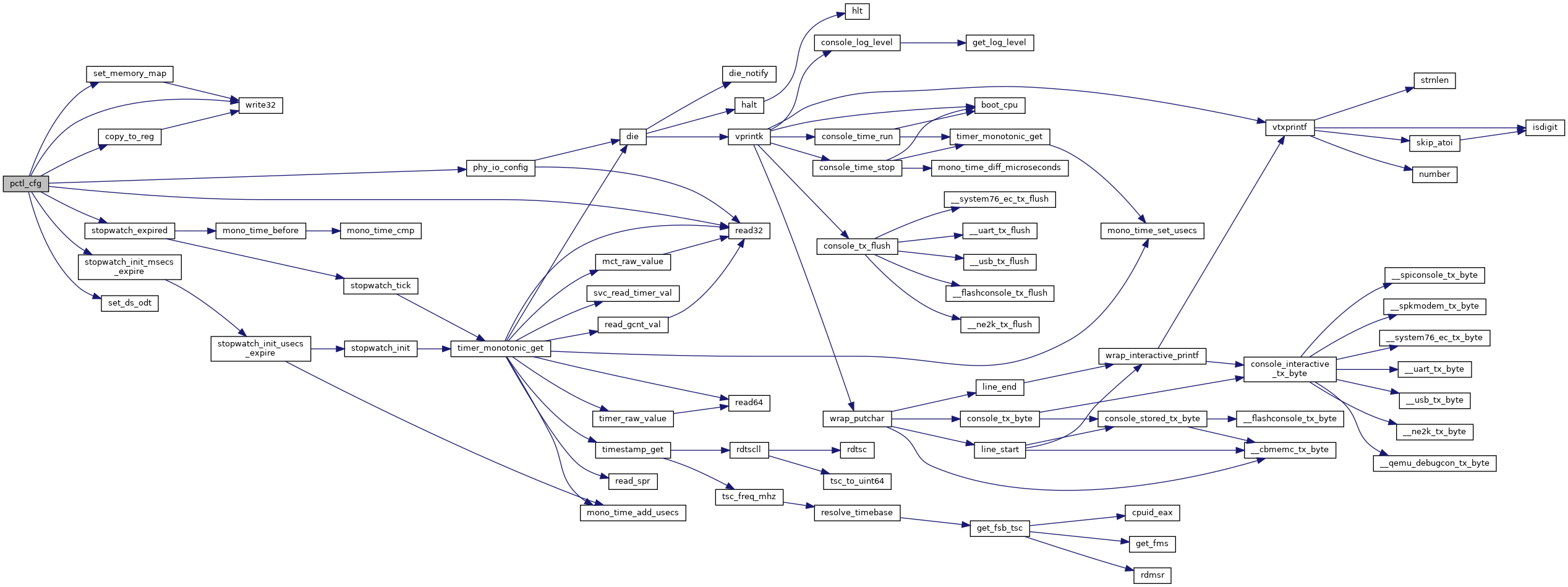

static |

Definition at line 1014 of file sdram.c.

References clrsetbits32, cru_ptr, noc_ddrtiminga0::d32, noc_ddrtimingb0::d32, noc_ddrtimingc0::d32, noc_devtodev0::d32, noc_ddrmode::d32, DDR_STRIDE, rk3399_msch_regs::ddrmode, rk3399_msch_timings::ddrmode, rk3399_msch_regs::ddrtiminga0, rk3399_msch_timings::ddrtiminga0, rk3399_msch_regs::ddrtimingb0, rk3399_msch_timings::ddrtimingb0, rk3399_msch_regs::ddrtimingc0, rk3399_msch_timings::ddrtimingc0, rk3399_msch_regs::devtodev0, rk3399_msch_timings::devtodev0, info, rk3399_pmugrf_regs::os_reg2, params, pmucru_ptr, rk3399_pmucru_reg::pmucru_rstnhold_con, PRESET_GPIO0_HOLD, PRESET_GPIO1_HOLD, PRESET_SGRF_HOLD, rk3399_ddr_pctl, rk3399_msch, rk3399_pmugrf, setbits32, SYS_REG_ENC_BK, SYS_REG_ENC_BW, SYS_REG_ENC_CHINFO, SYS_REG_ENC_COL, SYS_REG_ENC_CS0_ROW, SYS_REG_ENC_CS1_ROW, SYS_REG_ENC_DBW, SYS_REG_ENC_DDRTYPE, SYS_REG_ENC_NUM_CH, SYS_REG_ENC_RANK, SYS_REG_ENC_ROW_3_4, and write32().

Referenced by sdram_init().

|

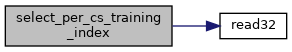

static |

Definition at line 627 of file sdram.c.

References LPDDR4, and params.

Referenced by data_training_ca(), and data_training_wdql().

Definition at line 598 of file sdram.c.

References clrbits32, clrsetbits32, rk3399_ddr_pctl_regs::denali_ctl, rk3399_ddr_publ_regs::denali_phy, rk3399_ddr_pctl, rk3399_ddr_publ, and setbits32.

Referenced by data_training_wl().

|

static |

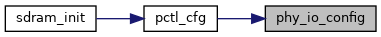

Definition at line 481 of file sdram.c.

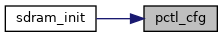

References clrbits32, clrsetbits32, copy_to_reg(), rk3399_ddr_pctl_regs::denali_ctl, rk3399_ddr_publ_regs::denali_phy, rk3399_ddr_pi_regs::denali_pi, params, phy_io_config(), PWRUP_SREFRESH_EXIT, read32(), rk3399_ddr_pctl, rk3399_ddr_pi, rk3399_ddr_publ, set_ds_odt(), set_memory_map(), setbits32, START, stopwatch_expired(), stopwatch_init_msecs_expire(), and write32().

Referenced by sdram_init().

|

static |

Definition at line 117 of file sdram.c.

References clrbits32, rk3399_ddr_publ_regs::denali_phy, MHz, and setbits32.

Referenced by sdram_init().

|

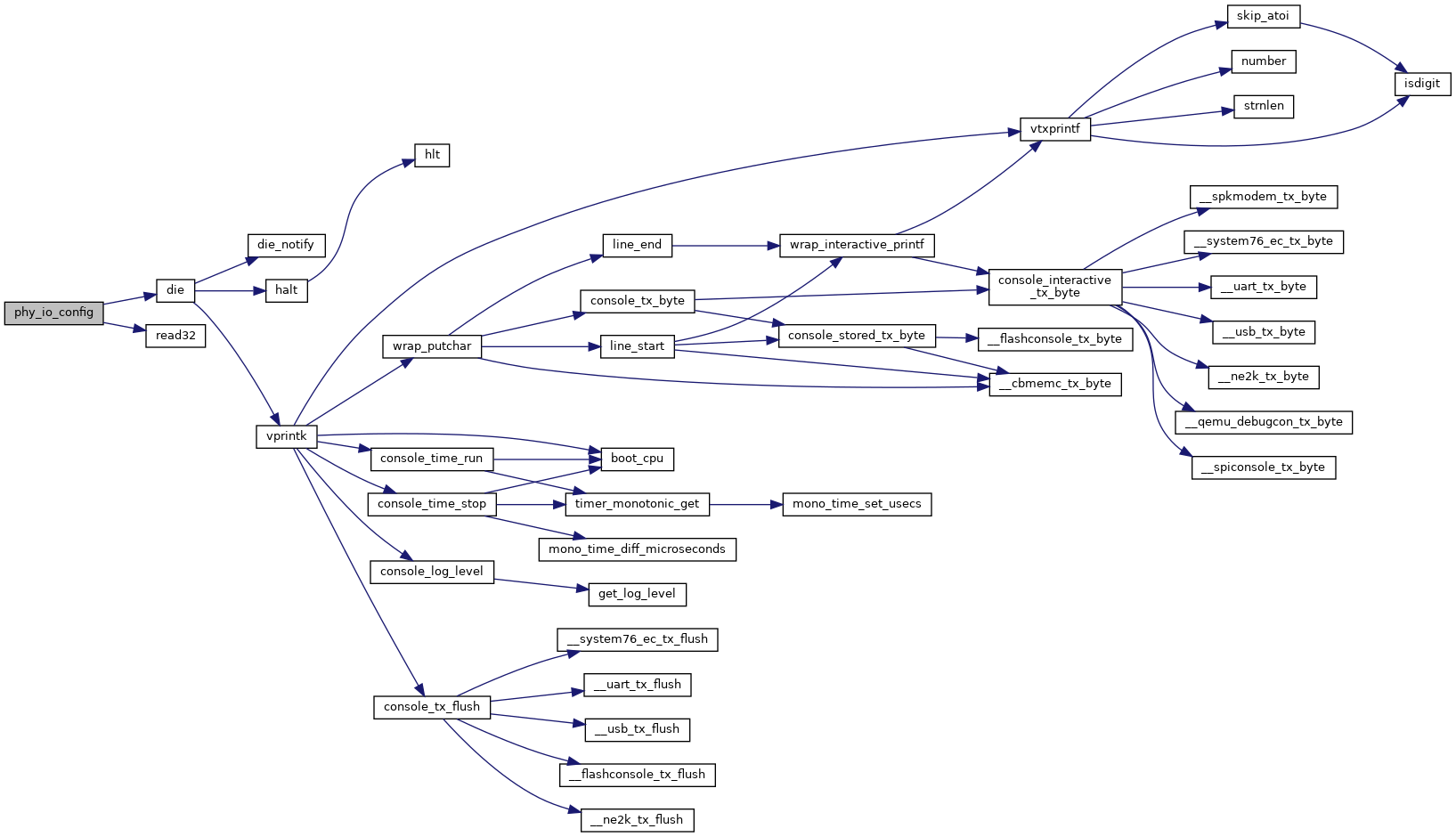

static |

Definition at line 331 of file sdram.c.

References clrsetbits32, DDR3, rk3399_ddr_publ_regs::denali_phy, die(), LPDDR3, LPDDR4, MHz, params, PHY_DRV_ODT_120, PHY_DRV_ODT_240, PHY_DRV_ODT_34_3, PHY_DRV_ODT_40, PHY_DRV_ODT_48, PHY_DRV_ODT_60, read32(), and rk3399_ddr_publ.

Referenced by pctl_cfg().

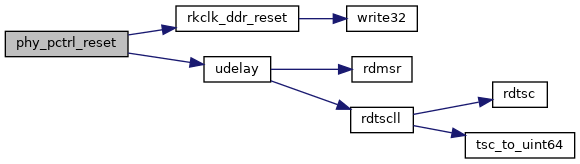

Definition at line 105 of file sdram.c.

References rkclk_ddr_reset(), and udelay().

Referenced by sdram_init().

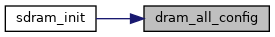

| void sdram_init | ( | const struct rk3399_sdram_params * | params | ) |

Definition at line 1109 of file sdram.c.

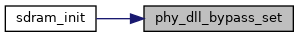

References BIOS_ERR, BIOS_INFO, board_reset(), data_training(), DDR3, die(), dram_all_config(), LPDDR3, LPDDR4, MHz, params, pctl_cfg(), phy_dll_bypass_set(), phy_pctrl_reset(), PI_FULL_TRAINING, printk, rk3399_ddr_publ, rkclk_configure_ddr(), set_ddrconfig(), switch_to_phy_index1(), and udelay().

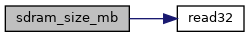

Definition at line 1158 of file sdram.c.

References ch, MiB, MIN, rk3399_pmugrf_regs::os_reg2, read32(), rk3399_pmugrf, SYS_REG_DEC_BK, SYS_REG_DEC_BW, SYS_REG_DEC_COL, SYS_REG_DEC_CS0_ROW, SYS_REG_DEC_CS1_ROW, SYS_REG_DEC_NUM_CH, SYS_REG_DEC_RANK, and SYS_REG_DEC_ROW_3_4.

Definition at line 581 of file sdram.c.

References clrsetbits32, rk3399_ddr_publ_regs::denali_phy, read32(), and rk3399_ddr_publ.

Referenced by data_training_ca(), data_training_rg(), data_training_rl(), data_training_wdql(), and data_training_wl().

|

static |

Definition at line 989 of file sdram.c.

References rk3399_msch_regs::ddrconf, rk3399_msch_regs::ddrsize, params, rk3399_msch, and write32().

Referenced by sdram_init().

|

static |

Definition at line 187 of file sdram.c.

References clrsetbits32, rk3399_ddr_publ_regs::denali_phy, LPDDR3, LPDDR4, params, PHY_DRV_ODT_240, PHY_DRV_ODT_34_3, PHY_DRV_ODT_40, PHY_DRV_ODT_48, PHY_DRV_ODT_Hi_Z, and rk3399_ddr_publ.

Referenced by pctl_cfg().

|

static |

Definition at line 147 of file sdram.c.

References rk3399_sdram_channel::bk, rk3399_sdram_channel::bw, clrsetbits32, rk3399_sdram_channel::col, DDR3, rk3399_sdram_channel::ddrconfig, rk3399_ddr_pctl_regs::denali_ctl, rk3399_ddr_pi_regs::denali_pi, params, rk3399_sdram_channel::rank, rk3399_ddr_pctl, rk3399_ddr_pi, and write32().

Referenced by pctl_cfg().

|

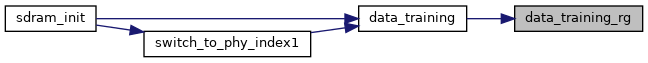

static |

Definition at line 1070 of file sdram.c.

References BIOS_ERR, board_reset(), rk3399_ddr_cic_regs::cic_ctrl0, rk3399_ddr_cic_regs::cic_status0, clrsetbits32, data_training(), rk3399_ddr_publ_regs::denali_phy, params, PI_FULL_TRAINING, printk, read32(), rk3399_ddr_cic, rk3399_ddr_publ, RK_CLRSETBITS, stopwatch_expired(), stopwatch_init_msecs_expire(), and write32().

Referenced by sdram_init().

|

static |

Definition at line 30 of file sdram.c.

Referenced by switch_to_phy_index1().

|

static |

Definition at line 22 of file sdram.c.

Referenced by dram_all_config(), override_write_leveling_value(), pctl_cfg(), and set_memory_map().

|

static |

Definition at line 24 of file sdram.c.

Referenced by data_training_ca(), data_training_rg(), data_training_rl(), data_training_wdql(), data_training_wl(), pctl_cfg(), and set_memory_map().

|

static |

Definition at line 26 of file sdram.c.

Referenced by data_training(), data_training_ca(), data_training_rg(), data_training_wl(), override_write_leveling_value(), pctl_cfg(), phy_io_config(), sdram_init(), select_per_cs_training_index(), set_ds_odt(), and switch_to_phy_index1().

|

static |

Definition at line 28 of file sdram.c.

Referenced by dram_all_config(), and set_ddrconfig().