|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

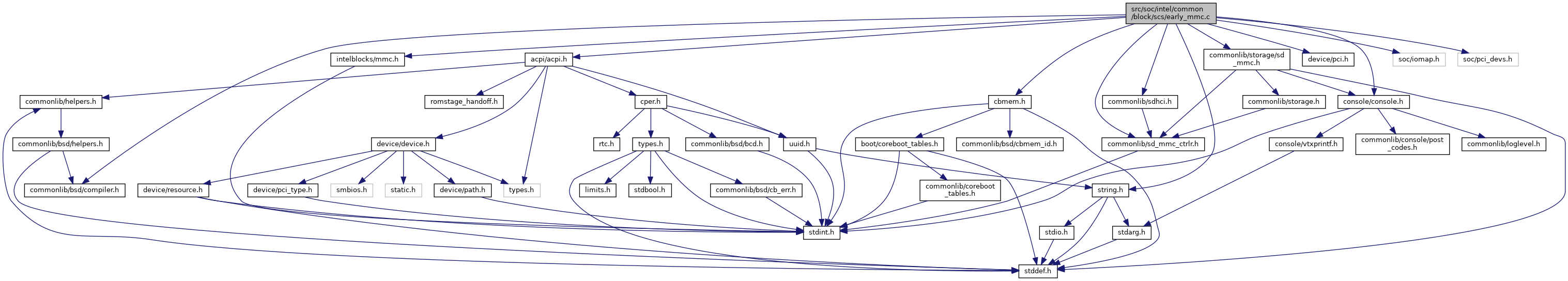

#include <acpi/acpi.h>#include <cbmem.h>#include <commonlib/storage/sd_mmc.h>#include <commonlib/sd_mmc_ctrlr.h>#include <commonlib/sdhci.h>#include <compiler.h>#include <console/console.h>#include <device/pci.h>#include <intelblocks/mmc.h>#include <soc/iomap.h>#include <soc/pci_devs.h>#include <string.h>

Go to the source code of this file.

Functions | |

| void | soc_sd_mmc_controller_quirks (struct sd_mmc_ctrlr *ctrlr) |

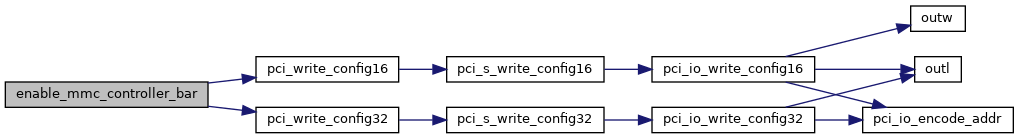

| static void | enable_mmc_controller_bar (void) |

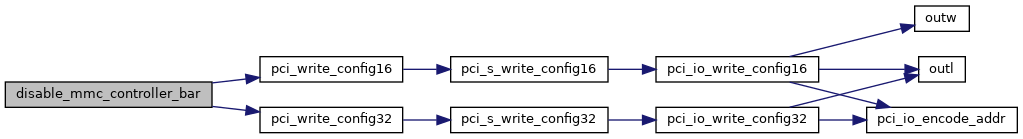

| static void | disable_mmc_controller_bar (void) |

| static void | set_early_mmc_wake_status (int32_t status) |

| int | early_mmc_wake_hw (void) |

Definition at line 38 of file early_mmc.c.

References PCH_DEV_EMMC, PCI_BASE_ADDRESS_0, PCI_COMMAND, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, pci_write_config16(), and pci_write_config32().

Referenced by early_mmc_wake_hw().

| int early_mmc_wake_hw | ( | void | ) |

Definition at line 61 of file early_mmc.c.

References acpi_is_wakeup_s3(), BIOS_ERR, CARD_IN_PROGRESS, container_of, storage_media::ctrlr, disable_mmc_controller_bar(), enable_mmc_controller_bar(), sdhci_ctrlr::ioaddr, media, memset(), mmc_send_op_cond(), new_pci_sdhci_controller(), NULL, PCH_DEV_EMMC, printk, sd_mmc_go_idle(), SET_BUS_WIDTH, SET_CLOCK, set_early_mmc_wake_status(), set_mmc_dll(), and soc_configure_mmc_gpios().

Definition at line 30 of file early_mmc.c.

References PCH_DEV_EMMC, PCI_BASE_ADDRESS_0, PCI_COMMAND, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, pci_write_config16(), and pci_write_config32().

Referenced by early_mmc_wake_hw().

Definition at line 45 of file early_mmc.c.

References BIOS_ERR, cbmem_add(), CBMEM_ID_MMC_STATUS, NULL, and printk.

Referenced by early_mmc_wake_hw().

| void soc_sd_mmc_controller_quirks | ( | struct sd_mmc_ctrlr * | ctrlr | ) |

Definition at line 16 of file early_mmc.c.

References BIOS_ERR, sd_mmc_ctrlr::f_max, sd_mmc_ctrlr::f_min, printk, and soc_get_mmc_frequencies().