|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

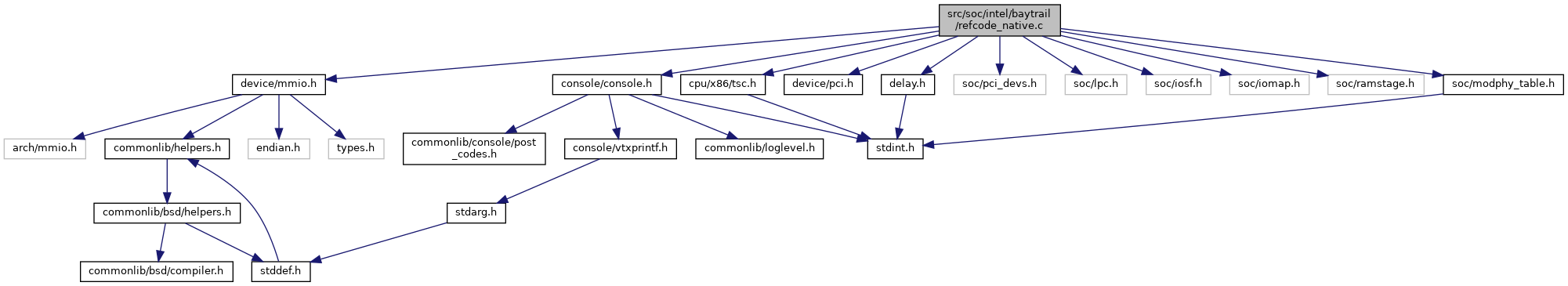

#include <device/mmio.h>#include <console/console.h>#include <cpu/x86/tsc.h>#include <device/pci.h>#include <delay.h>#include <soc/pci_devs.h>#include <soc/lpc.h>#include <soc/iosf.h>#include <soc/iomap.h>#include <soc/ramstage.h>#include <soc/modphy_table.h>

Go to the source code of this file.

Macros | |

| #define | IOSF_READ(op_read, port) (IOSF_OPCODE(op_read) | IOSF_PORT(port)) |

| #define | IOSF_WRITE(op_write, port) (IOSF_OPCODE(op_write) | IOSF_PORT(port)) |

| #define | BUNIT_BALIMIT0 0x0b |

| #define | AUNIT_AVCCTL 0x21 |

| #define | AUNIT_ACFCACV 0x60 |

| #define | CUNIT_ACCESS_CTRL_VIOL 0x41 |

| #define | CUINT_SSA_REGIONAL_TRUNKGATE_CTL 0x43 |

| #define | TUNIT_CTL 0x03 |

| #define | TUNIT_MISC_CTL 0x04 |

| #define | R_PCH_PMC_MTPMC1 0xb0 |

Functions | |

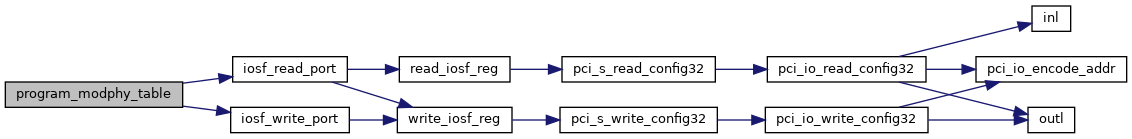

| static void | program_modphy_table (struct modphy_entry *table) |

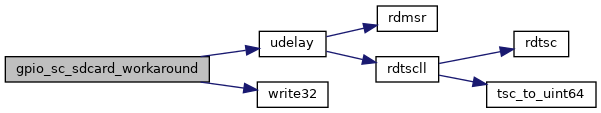

| static void | gpio_sc_sdcard_workaround (void) |

| static void | ssa_safe_config (void) |

| void | baytrail_run_reference_code (void) |

| #define AUNIT_ACFCACV 0x60 |

Definition at line 52 of file refcode_native.c.

| #define AUNIT_AVCCTL 0x21 |

Definition at line 51 of file refcode_native.c.

| #define BUNIT_BALIMIT0 0x0b |

Definition at line 50 of file refcode_native.c.

| #define CUINT_SSA_REGIONAL_TRUNKGATE_CTL 0x43 |

Definition at line 54 of file refcode_native.c.

| #define CUNIT_ACCESS_CTRL_VIOL 0x41 |

Definition at line 53 of file refcode_native.c.

| #define IOSF_READ | ( | op_read, | |

| port | |||

| ) | (IOSF_OPCODE(op_read) | IOSF_PORT(port)) |

Definition at line 15 of file refcode_native.c.

| #define IOSF_WRITE | ( | op_write, | |

| port | |||

| ) | (IOSF_OPCODE(op_write) | IOSF_PORT(port)) |

Definition at line 17 of file refcode_native.c.

| #define R_PCH_PMC_MTPMC1 0xb0 |

Definition at line 83 of file refcode_native.c.

| #define TUNIT_CTL 0x03 |

Definition at line 55 of file refcode_native.c.

| #define TUNIT_MISC_CTL 0x04 |

Definition at line 56 of file refcode_native.c.

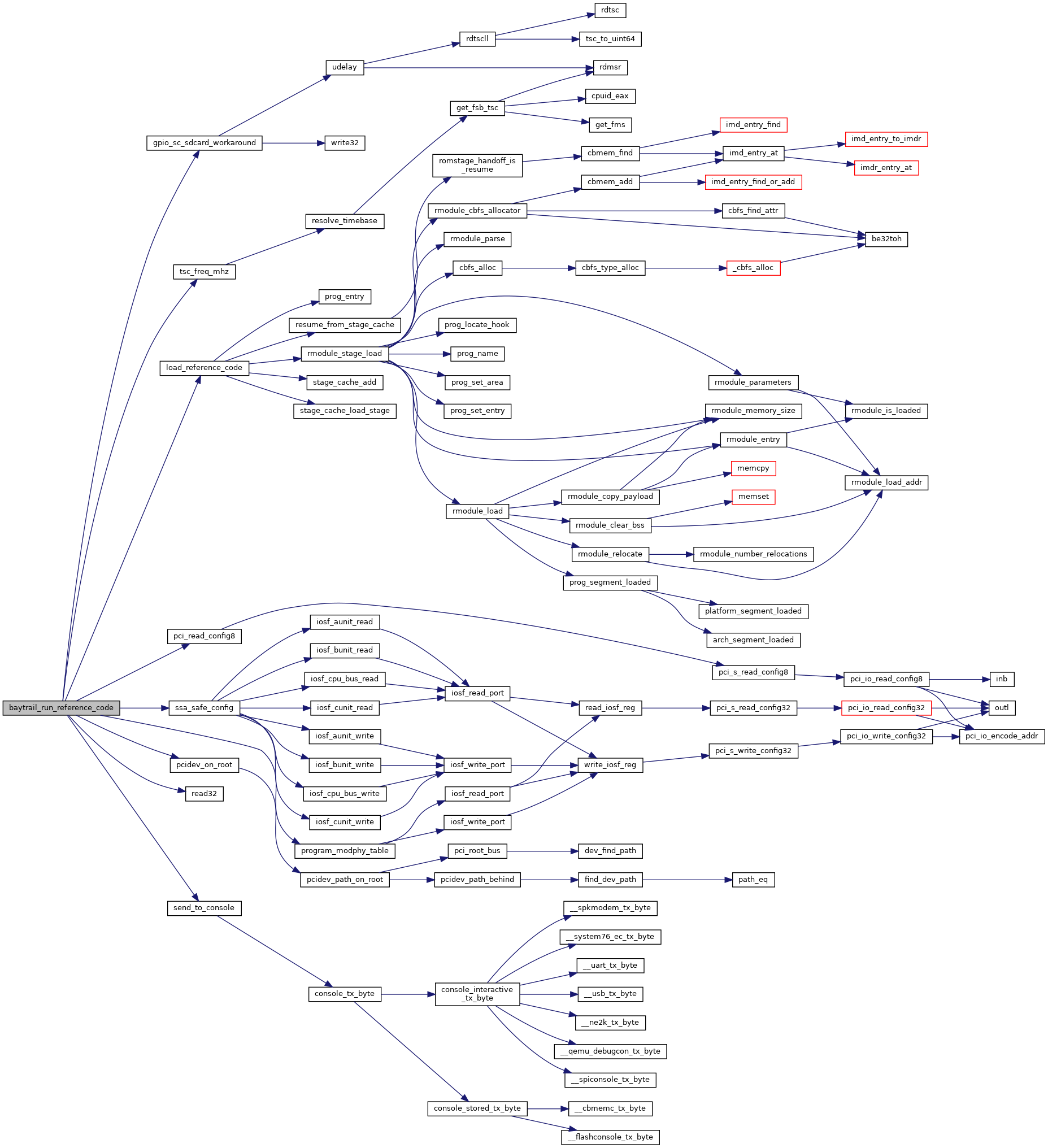

Definition at line 88 of file refcode_native.c.

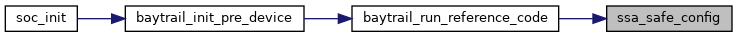

References BIOS_DEBUG, EFI_WRAPPER_VER, gpio_sc_sdcard_workaround(), load_reference_code(), LPC_DEV, LPC_FUNC, NULL, pci_read_config8(), pcidev_on_root(), PMC_BASE_ADDRESS, printk, program_modphy_table(), R_PCH_PMC_MTPMC1, read32(), reva0_modphy_table, revb0_modphy_table, REVID, RID_B_STEPPING_START, send_to_console(), setbits32, ssa_safe_config(), tsc_freq_mhz(), efi_wrapper_params::tsc_ticks_per_microsecond, and efi_wrapper_params::version.

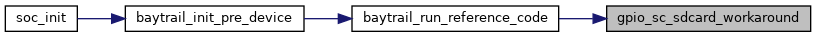

Referenced by baytrail_init_pre_device().

Definition at line 31 of file refcode_native.c.

References clrbits32, clrsetbits32, IO_BASE_ADDRESS, setbits32, udelay(), and write32().

Referenced by baytrail_run_reference_code().

|

static |

Definition at line 20 of file refcode_native.c.

References IOSF_READ, iosf_read_port(), IOSF_WRITE, iosf_write_port(), modphy_entry::mask, modphy_entry::op_read, modphy_entry::op_write, modphy_entry::port, modphy_entry::reg, and modphy_entry::value.

Referenced by baytrail_run_reference_code().

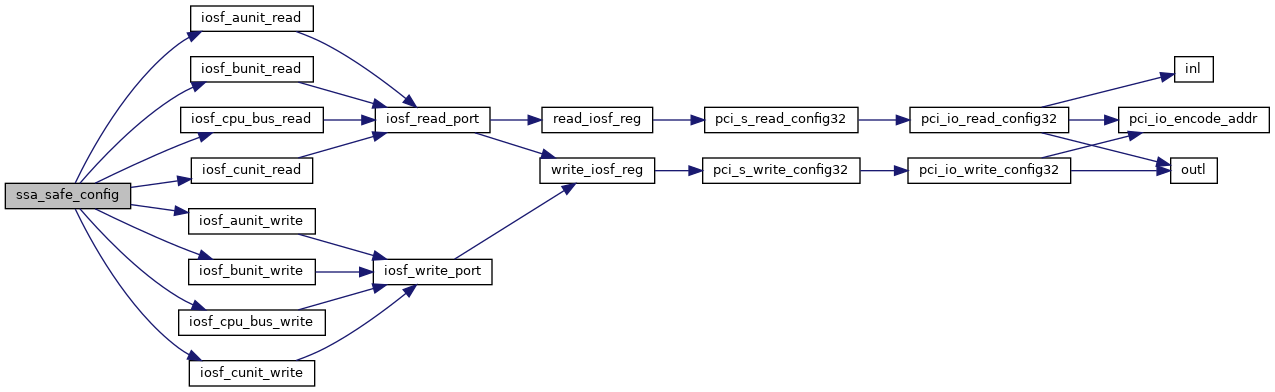

Definition at line 58 of file refcode_native.c.

References AUNIT_ACFCACV, AUNIT_AVCCTL, BUNIT_BALIMIT0, CUINT_SSA_REGIONAL_TRUNKGATE_CTL, CUNIT_ACCESS_CTRL_VIOL, iosf_aunit_read(), iosf_aunit_write(), iosf_bunit_read(), iosf_bunit_write(), iosf_cpu_bus_read(), iosf_cpu_bus_write(), iosf_cunit_read(), iosf_cunit_write(), TUNIT_CTL, and TUNIT_MISC_CTL.

Referenced by baytrail_run_reference_code().