|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

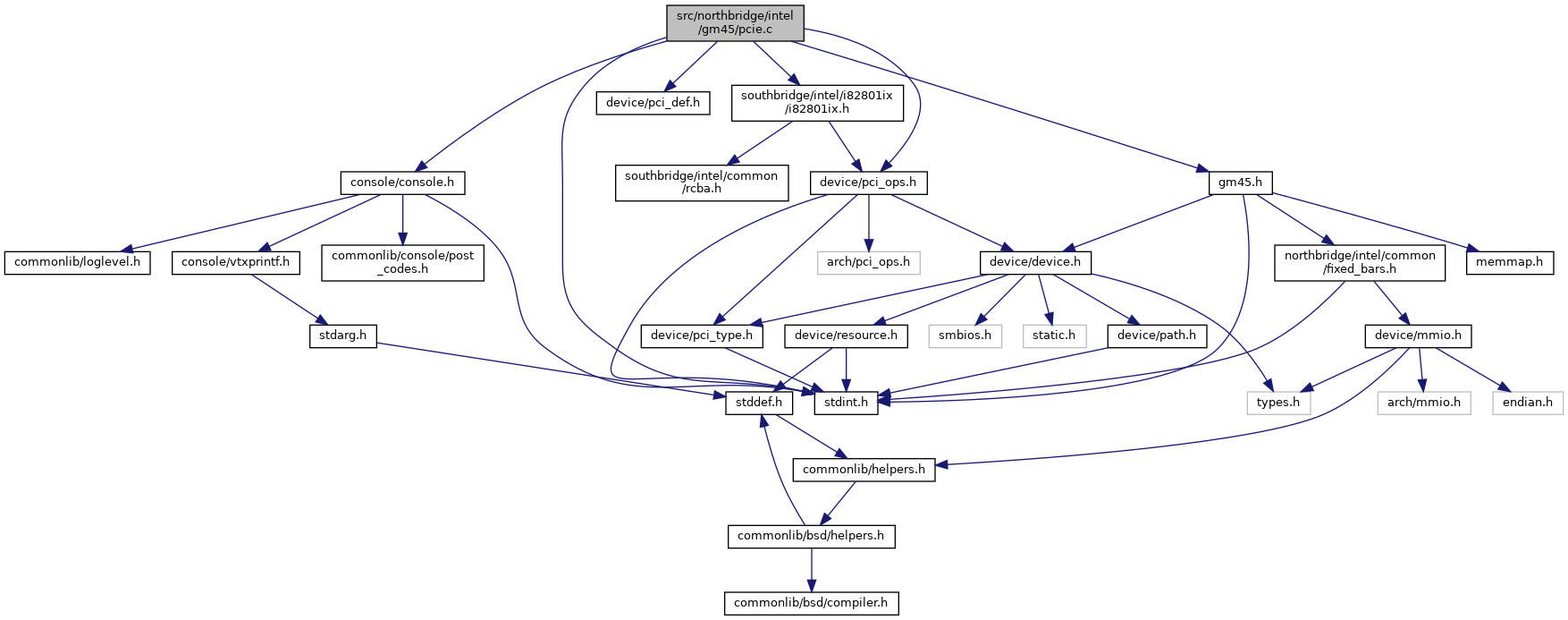

#include <stdint.h>#include <device/pci_ops.h>#include <device/pci_def.h>#include <console/console.h>#include <southbridge/intel/i82801ix/i82801ix.h>#include "gm45.h"

Go to the source code of this file.

Functions | |

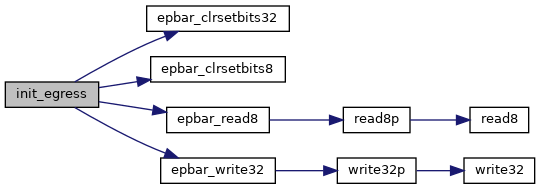

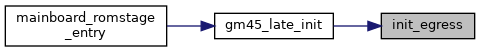

| static void | init_egress (void) |

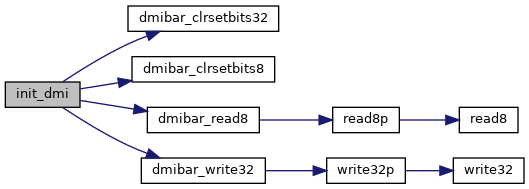

| static void | init_dmi (int b2step) |

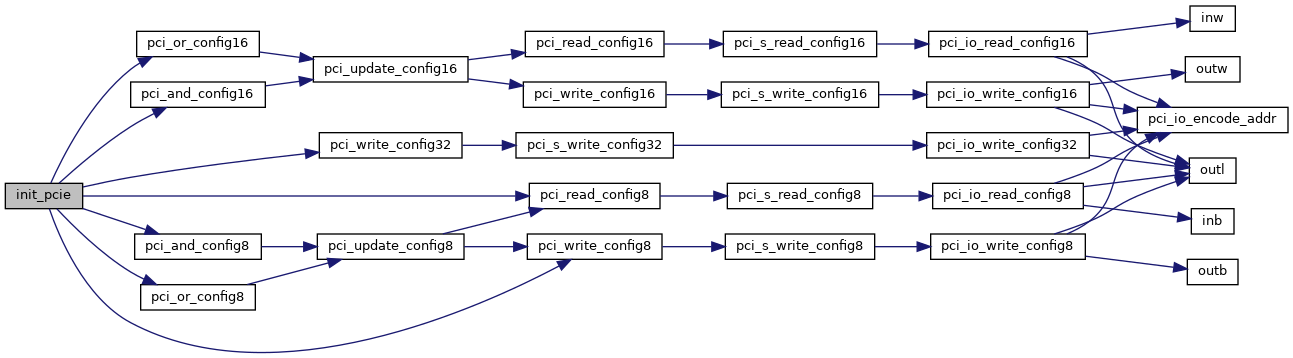

| static void | init_pcie (const int peg_enabled, const int sdvo_enabled, const int peg_x16) |

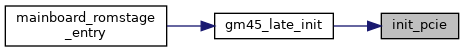

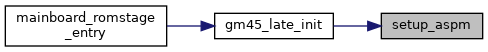

| static void | setup_aspm (const stepping_t stepping, const int peg_enabled) |

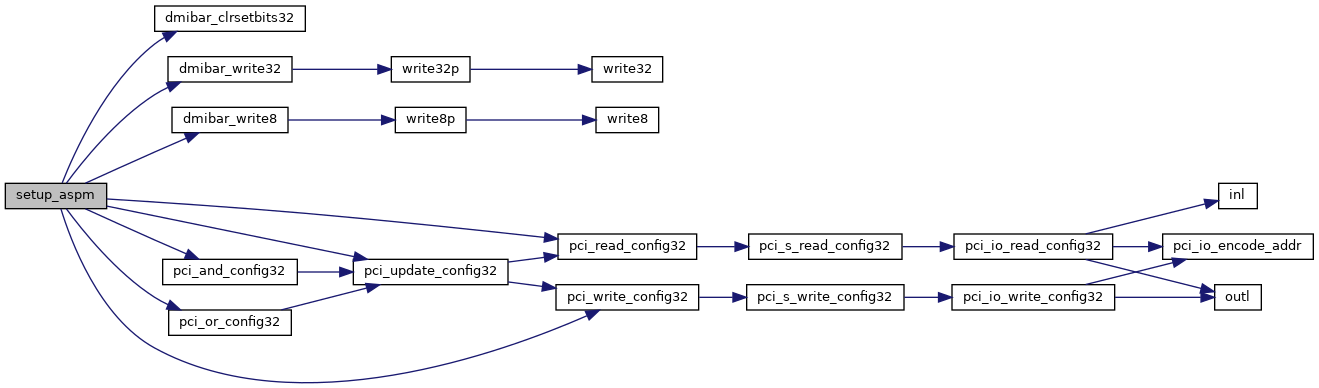

| static void | setup_rcrb (const int peg_enabled) |

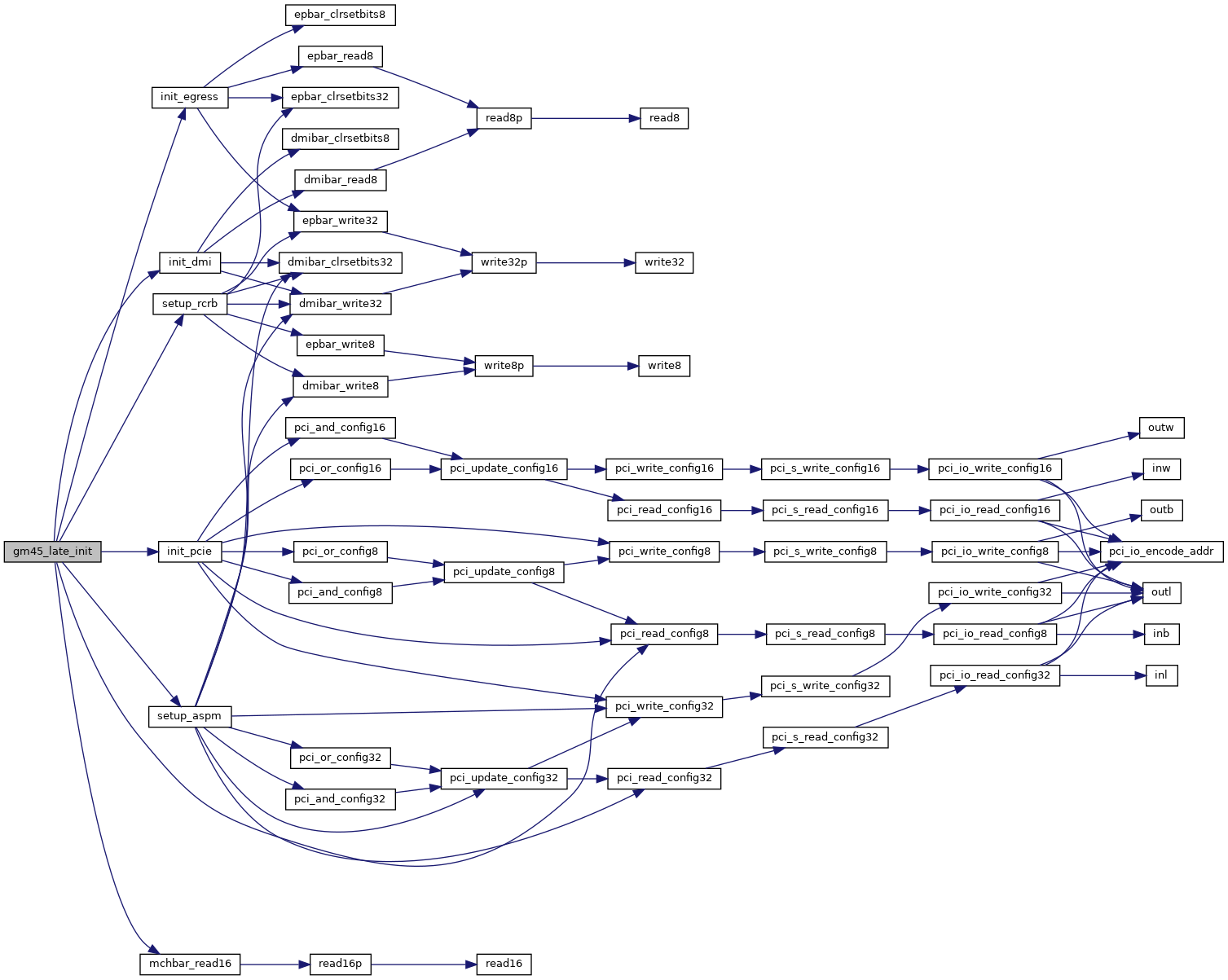

| void | gm45_late_init (const stepping_t stepping) |

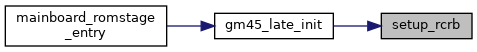

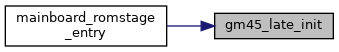

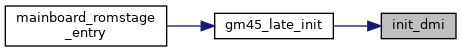

| void gm45_late_init | ( | const stepping_t | stepping | ) |

Definition at line 272 of file pcie.c.

References D0F0_DEVEN, init_dmi(), init_egress(), init_pcie(), mchbar_read16(), PCI_DEV, pci_read_config8(), setup_aspm(), setup_rcrb(), stepping, and STEPPING_B2.

Referenced by mainboard_romstage_entry().

|

static |

Definition at line 46 of file pcie.c.

References dmibar_clrbits32, dmibar_clrbits8, dmibar_clrsetbits32(), dmibar_clrsetbits8(), dmibar_read8(), dmibar_setbits32, dmibar_write32(), DMIPVCCAP1, DMIVC0RCTL, DMIVC1RCTL, DMIVC1RSTS, and VC1NP.

Referenced by gm45_late_init().

Definition at line 11 of file pcie.c.

References EP_PORTARB, epbar_clrbits8, epbar_clrsetbits32(), epbar_clrsetbits8(), epbar_read8(), epbar_setbits32, epbar_write32(), EPPVCCAP1, EPVC0RCTL, EPVC1MTS, EPVC1RCAP, EPVC1RCTL, and EPVC1RSTS.

Referenced by gm45_late_init().

|

static |

Definition at line 92 of file pcie.c.

References BIOS_DEBUG, D0F0_DEVEN, D1F0_VC0RCTL, D1F0_VCCAP, pci_and_config16(), pci_and_config8(), PCI_DEV, pci_or_config16(), pci_or_config8(), pci_read_config8(), pci_write_config32(), pci_write_config8(), PEG_CAP, PEGLC, printk, and SLOTCAP.

Referenced by gm45_late_init().

|

static |

Definition at line 136 of file pcie.c.

References dmibar_clrbits16, dmibar_clrbits32, dmibar_clrsetbits32(), dmibar_setbits16, dmibar_setbits8, dmibar_write32(), dmibar_write8(), DMILCAP, DMILCTL, LPC_IS_MOBILE, pci_and_config32(), PCI_DEV, pci_or_config32(), pci_read_config32(), pci_update_config32(), pci_write_config32(), stepping, STEPPING_B0, STEPPING_B1, and STEPPING_B2.

Referenced by gm45_late_init().

|

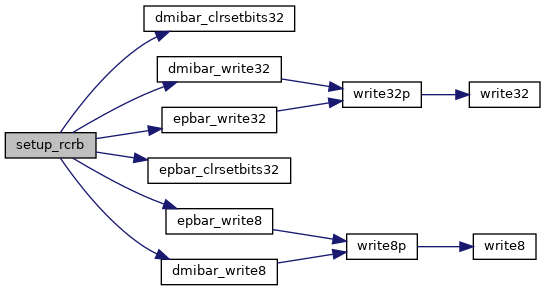

static |

Definition at line 243 of file pcie.c.

References dmibar_clrsetbits32(), dmibar_write32(), dmibar_write8(), DMIESD, DMILE1A, DMILE1D, DMILE2A, DMILE2D, epbar_clrsetbits32(), epbar_setbits8, epbar_write32(), epbar_write8(), EPESD, EPLE1A, EPLE1D, and EPLE2D.

Referenced by gm45_late_init().