|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

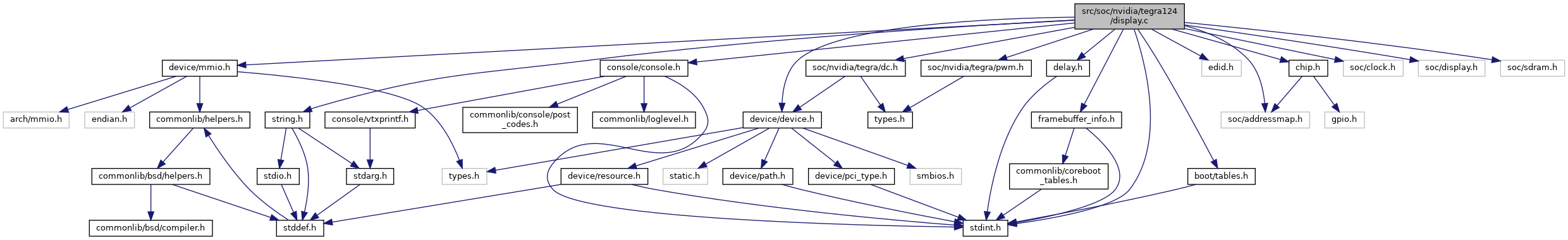

#include <device/mmio.h>#include <boot/tables.h>#include <console/console.h>#include <delay.h>#include <device/device.h>#include <edid.h>#include <soc/addressmap.h>#include <soc/clock.h>#include <soc/display.h>#include <soc/sdram.h>#include <soc/nvidia/tegra/dc.h>#include <soc/nvidia/tegra/pwm.h>#include <stdint.h>#include <string.h>#include <framebuffer_info.h>#include "chip.h"

Go to the source code of this file.

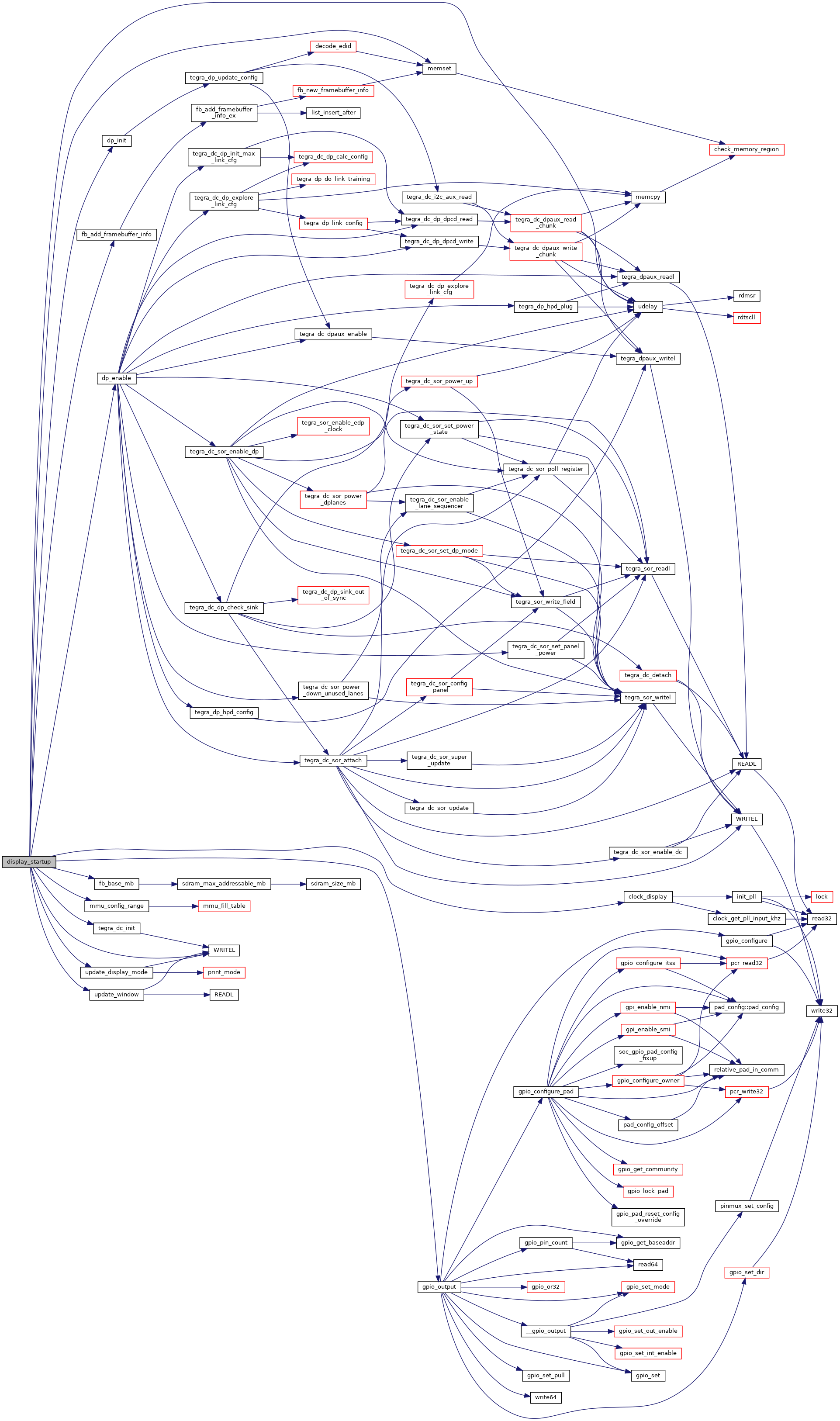

Functions | |

| unsigned long | READL (void *p) |

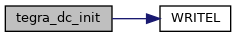

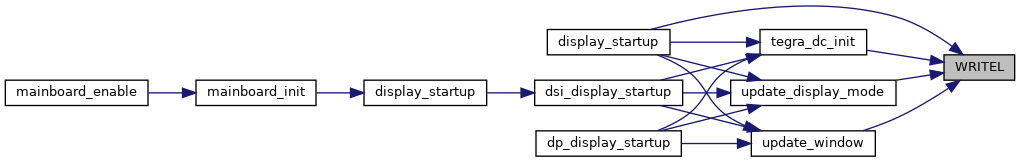

| void | WRITEL (unsigned long value, void *p) |

| static int | tegra_dc_calc_refresh (const struct soc_nvidia_tegra124_config *config) |

| static void | print_mode (const struct soc_nvidia_tegra124_config *config) |

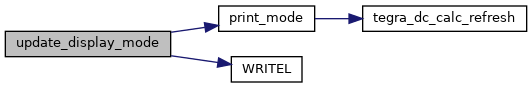

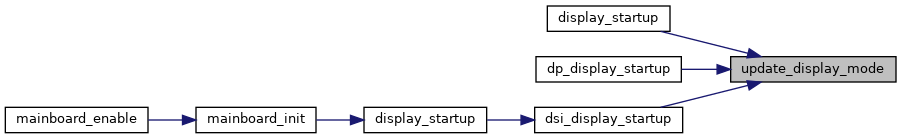

| static int | update_display_mode (struct display_controller *disp_ctrl, struct soc_nvidia_tegra124_config *config) |

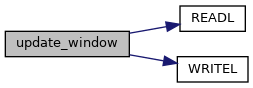

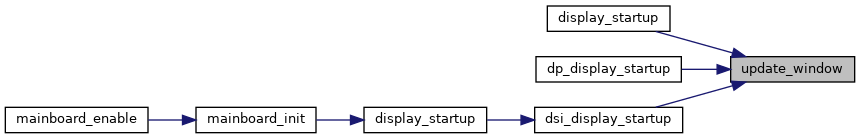

| static void | update_window (struct display_controller *disp_ctrl, struct soc_nvidia_tegra124_config *config) |

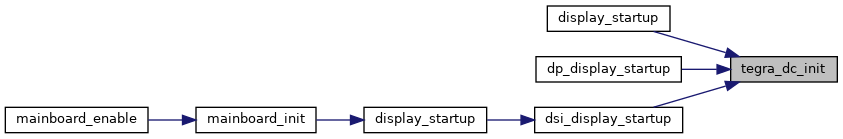

| static int | tegra_dc_init (struct display_controller *disp_ctrl) |

| uint32_t | fb_base_mb (void) |

| void | display_startup (struct device *dev) |

Variables | |

| struct tegra_dc | dc_data |

| int | dump = 0 |

Definition at line 198 of file display.c.

References ALIGN_UP, tegra_dc::base, BIOS_ERR, BIOS_INFO, BIOS_SPEW, BIOS_WARNING, device::chip_info, clock_display(), config, tegra_dc::config, dc_data, DCACHE_WRITETHROUGH, DIV_ROUND_UP, dp_enable(), dp_init(), fb_add_framebuffer_info(), fb_base_mb(), gpio_output(), memset(), MiB, mmu_config_range(), NV_PWM_CSR_ENABLE_SHIFT, NV_PWM_CSR_PULSE_WIDTH_SHIFT, tegra_dc::out, printk, TEGRA_ARM_DISPLAYA, tegra_dc_init(), TEGRA_PWM_BASE, udelay(), update_display_mode(), update_window(), and WRITEL().

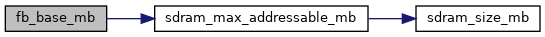

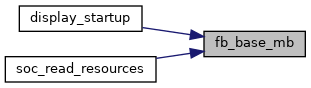

Definition at line 190 of file display.c.

References FB_SIZE_MB, and sdram_max_addressable_mb().

Referenced by display_startup(), and soc_read_resources().

|

static |

Definition at line 66 of file display.c.

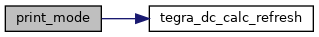

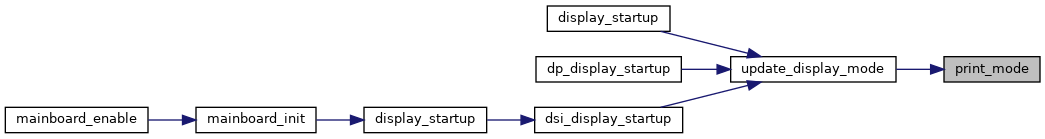

References BIOS_ERR, config, printk, refresh, and tegra_dc_calc_refresh().

Referenced by update_display_mode().

Definition at line 24 of file display.c.

Referenced by update_window().

|

static |

Definition at line 49 of file display.c.

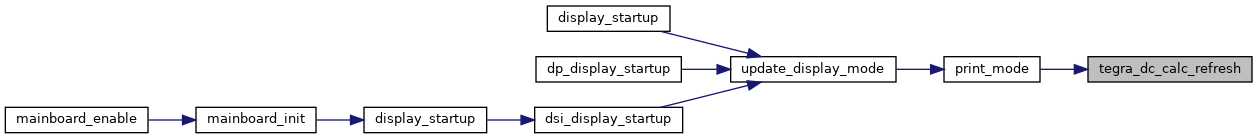

References config, and refresh.

Referenced by print_mode().

|

static |

Definition at line 154 of file display.c.

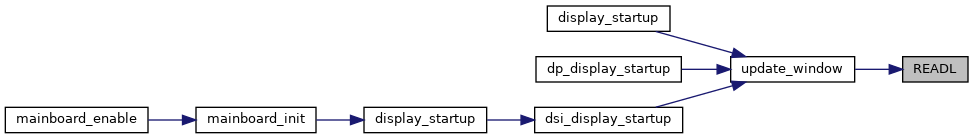

References dc_winbuf_reg::addr_h_offset, dc_winbuf_reg::addr_v_offset, dc_win_reg::blend_alpha_1bit, dc_win_reg::blend_layer_ctrl, dc_win_reg::blend_match_select, dc_win_reg::blend_nomatch_select, dc_win_reg::buffer_ctrl, dc_win_reg::byte_swap, display_controller::cmd, display_controller::com, dc_com_reg::crc_checksum, dc_win_reg::dda_increment, display_controller::disp, dc_disp_reg::disp_signal_opt0, dc_cmd_reg::disp_win_header, dc_win_reg::dv_ctrl, dc_win_reg::h_initial_dda, dc_cmd_reg::int_mask, dc_com_reg::pin_output_enb, dc_win_reg::pos, READ_MUX_ASSEMBLY, dc_winbuf_reg::start_addr_hi, dc_cmd_reg::state_access, dc_win_reg::v_initial_dda, display_controller::win, dc_win_reg::win_opt, display_controller::winbuf, WINDOW_A_SELECT, WRITE_MUX_ASSEMBLY, and WRITEL().

Referenced by display_startup(), dp_display_startup(), and dsi_display_startup().

|

static |

We want to use PLLD_out0, which is PLLD / 2: PixelClock = (PLLD / 2) / ShiftClockDiv / PixelClockDiv.

Currently most panels work inside clock range 50MHz~100MHz, and PLLD has some requirements to have VCO in range 500MHz~1000MHz (see clock.c for more detail). To simplify calculation, we set PixelClockDiv to 1 and ShiftClockDiv to 1. In future these values may be calculated by clock_display, to allow wider frequency range.

Note ShiftClockDiv is a 7.1 format value.

Definition at line 78 of file display.c.

References dc_disp_reg::back_porch, BIOS_DEBUG, config, display_controller::disp, dc_disp_reg::disp_active, dc_disp_reg::disp_clk_ctrl, dc_disp_reg::disp_timing_opt, dc_disp_reg::front_porch, PIXEL_CLK_DIVIDER_PCD1, PIXEL_CLK_DIVIDER_SHIFT, print_mode(), printk, dc_disp_reg::ref_to_sync, SHIFT_CLK_DIVIDER_SHIFT, dc_disp_reg::sync_width, and WRITEL().

Referenced by display_startup(), dp_display_startup(), and dsi_display_startup().

|

static |

Definition at line 121 of file display.c.

References dc_disp_reg::blend_background_color, display_controller::cmd, dc_win_reg::color_depth, COLOR_WHITE, config, dc_win_reg::dda_increment, display_controller::disp, dc_cmd_reg::disp_cmd, DISP_CTRL_MODE_C_DISPLAY, dc_cmd_reg::disp_win_header, GENERAL_ACT_REQ, GENERAL_UPDATE, H_DDA_INC, dc_win_reg::line_stride, dc_win_reg::prescaled_size, READL(), dc_win_reg::size, dc_winbuf_reg::start_addr, dc_cmd_reg::state_access, dc_cmd_reg::state_ctrl, V_DDA_INC, val, display_controller::win, WIN_A_ACT_REQ, WIN_A_UPDATE, WIN_ENABLE, dc_win_reg::win_opt, display_controller::winbuf, WINDOW_A_SELECT, WRITE_MUX_ACTIVE, and WRITEL().

Referenced by display_startup(), dp_display_startup(), and dsi_display_startup().

Definition at line 41 of file display.c.

Referenced by display_startup(), tegra_dc_init(), update_display_mode(), and update_window().

| struct tegra_dc dc_data |

Definition at line 1 of file display.c.

Referenced by display_startup().

| int dump = 0 |

Definition at line 23 of file display.c.

Referenced by biosemu(), biosemu_dev_check_exprom(), dapc_init(), pmm_setup(), READL(), southbridge_smi_handler(), and WRITEL().