|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

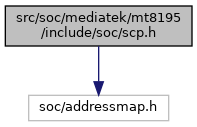

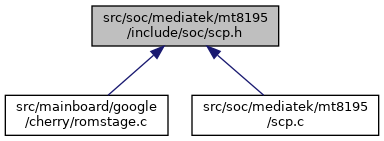

#include <soc/addressmap.h>

Go to the source code of this file.

Macros | |

| #define | SCP_SRAM_PDN_DISABLE_VAL 0xFFFFFFFF |

| #define | REG_L1TCM_SRAM_PDN (void *)(SCP_CFG_BASE + 0x2102C) |

Functions | |

| void | scp_rsi_enable (void) |

| void | scp_rsi_disable (void) |

| #define REG_L1TCM_SRAM_PDN (void *)(SCP_CFG_BASE + 0x2102C) |

Definition at line 16 of file scp.c.

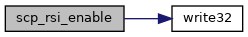

References REG_L1TCM_SRAM_PDN, SCP_SRAM_PDN_DISABLE_VAL, and write32().

Definition at line 6 of file scp.c.

References REG_L1TCM_SRAM_PDN, SCP_SRAM_PDN_DISABLE_VAL, val, and write32().

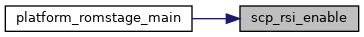

Referenced by platform_romstage_main().