|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

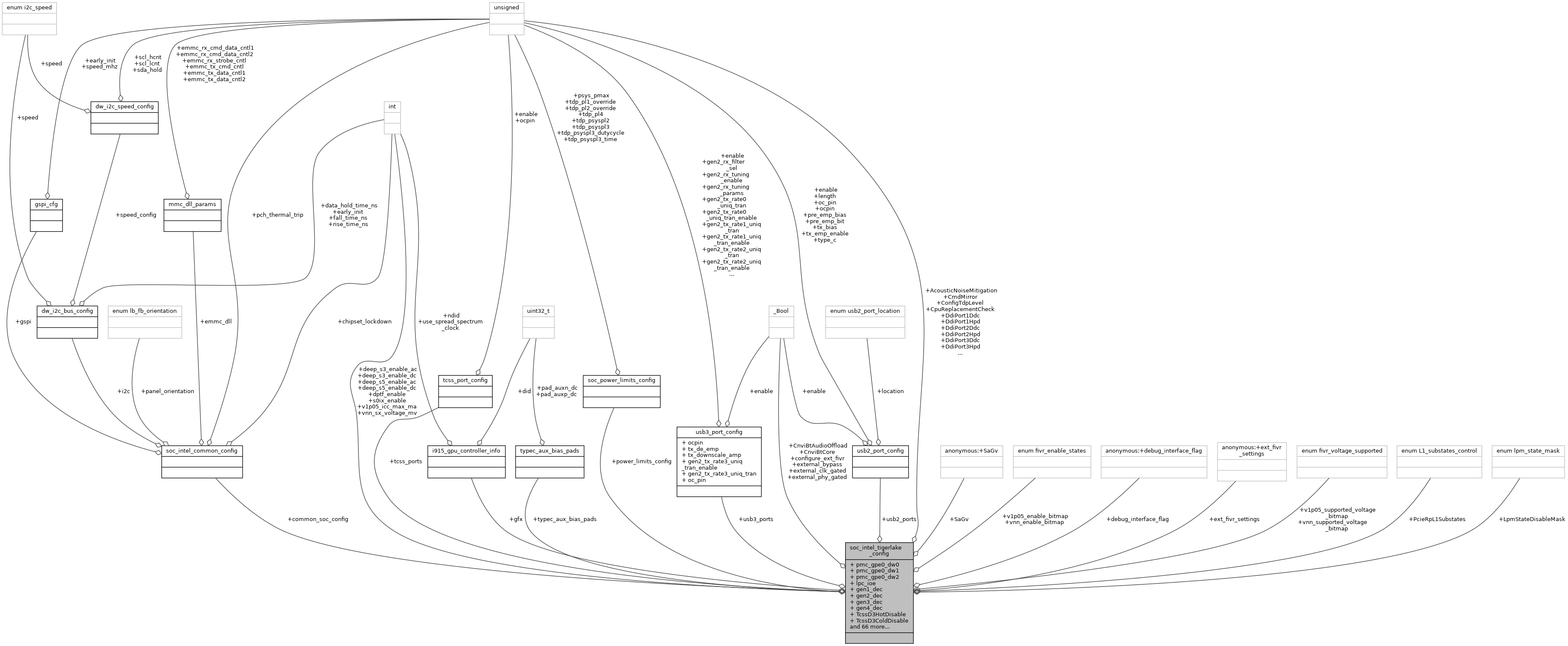

#include <chip.h>

Public Types | |

| enum | { SaGv_Disabled , SaGv_FixedPoint0 , SaGv_FixedPoint1 , SaGv_FixedPoint2 , SaGv_FixedPoint3 , SaGv_Enabled } |

| enum | { DEBUG_INTERFACE_RAM = (1 << 0) , DEBUG_INTERFACE_UART_8250IO = (1 << 1) , DEBUG_INTERFACE_USB3 = (1 << 3) , DEBUG_INTERFACE_LPSS_SERIAL_IO = (1 << 4) , DEBUG_INTERFACE_TRACEHUB = (1 << 5) } |

| anonymous enum |

| anonymous enum |

| struct soc_intel_common_config soc_intel_tigerlake_config::common_soc_config |

| enum { ... } soc_intel_tigerlake_config::debug_interface_flag |

| struct { ... } soc_intel_tigerlake_config::ext_fivr_settings |

| struct i915_gpu_controller_info soc_intel_tigerlake_config::gfx |

| uint8_t soc_intel_tigerlake_config::gpio_override_pm |

Definition at line 356 of file chip.h.

Referenced by mainboard_update_soc_chip_config().

| uint8_t soc_intel_tigerlake_config::gpio_pm[TOTAL_GPIO_COMM] |

Definition at line 368 of file chip.h.

Referenced by mainboard_update_soc_chip_config().

| uint16_t soc_intel_tigerlake_config::ITbtConnectTopologyTimeoutInMs |

| enum lpm_state_mask soc_intel_tigerlake_config::LpmStateDisableMask |

Definition at line 122 of file chip.h.

Referenced by mainboard_update_soc_chip_config().

| uint8_t soc_intel_tigerlake_config::PchHdaAudioLinkDmicEnable[MAX_HD_AUDIO_DMIC_LINKS] |

| uint8_t soc_intel_tigerlake_config::PchHdaAudioLinkSndwEnable[MAX_HD_AUDIO_SNDW_LINKS] |

| uint8_t soc_intel_tigerlake_config::PchHdaAudioLinkSspEnable[MAX_HD_AUDIO_SSP_LINKS] |

| uint8_t soc_intel_tigerlake_config::PchHdaIDispCodecDisconnect |

| uint8_t soc_intel_tigerlake_config::PcieClkSrcClkReq[CONFIG_MAX_PCIE_CLOCK_SRC] |

| uint8_t soc_intel_tigerlake_config::PcieClkSrcUsage[CONFIG_MAX_PCIE_CLOCK_SRC] |

| uint8_t soc_intel_tigerlake_config::PciePtm[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_tigerlake_config::PcieRpAdvancedErrorReporting[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_tigerlake_config::PcieRpClkReqDetect[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_tigerlake_config::PcieRpEnable[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_tigerlake_config::PcieRpHotPlug[CONFIG_MAX_ROOT_PORTS] |

| enum L1_substates_control soc_intel_tigerlake_config::PcieRpL1Substates[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_tigerlake_config::PcieRpLtrEnable[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_tigerlake_config::PcieRpSlotImplemented[CONFIG_MAX_ROOT_PORTS] |

| struct soc_power_limits_config soc_intel_tigerlake_config::power_limits_config[POWER_LIMITS_MAX] |

| enum { ... } soc_intel_tigerlake_config::SaGv |

| uint8_t soc_intel_tigerlake_config::SataPortsEnableDitoConfig[8] |

| uint8_t soc_intel_tigerlake_config::SerialIoGSpiCsMode[CONFIG_SOC_INTEL_COMMON_BLOCK_GSPI_MAX] |

| uint8_t soc_intel_tigerlake_config::SerialIoGSpiCsState[CONFIG_SOC_INTEL_COMMON_BLOCK_GSPI_MAX] |

| uint8_t soc_intel_tigerlake_config::SerialIoGSpiMode[CONFIG_SOC_INTEL_COMMON_BLOCK_GSPI_MAX] |

| uint8_t soc_intel_tigerlake_config::SerialIoI2cMode[CONFIG_SOC_INTEL_I2C_DEV_MAX] |

| uint8_t soc_intel_tigerlake_config::SerialIoUartMode[CONFIG_SOC_INTEL_UART_DEV_MAX] |

| struct tcss_port_config soc_intel_tigerlake_config::tcss_ports[MAX_TYPE_C_PORTS] |

| struct typec_aux_bias_pads soc_intel_tigerlake_config::typec_aux_bias_pads[MAX_TYPE_C_PORTS] |

| struct usb2_port_config soc_intel_tigerlake_config::usb2_ports[16] |

| struct usb3_port_config soc_intel_tigerlake_config::usb3_ports[10] |

| enum fivr_enable_states soc_intel_tigerlake_config::v1p05_enable_bitmap |

| enum fivr_voltage_supported soc_intel_tigerlake_config::v1p05_supported_voltage_bitmap |

| enum fivr_enable_states soc_intel_tigerlake_config::vnn_enable_bitmap |

| enum fivr_voltage_supported soc_intel_tigerlake_config::vnn_supported_voltage_bitmap |