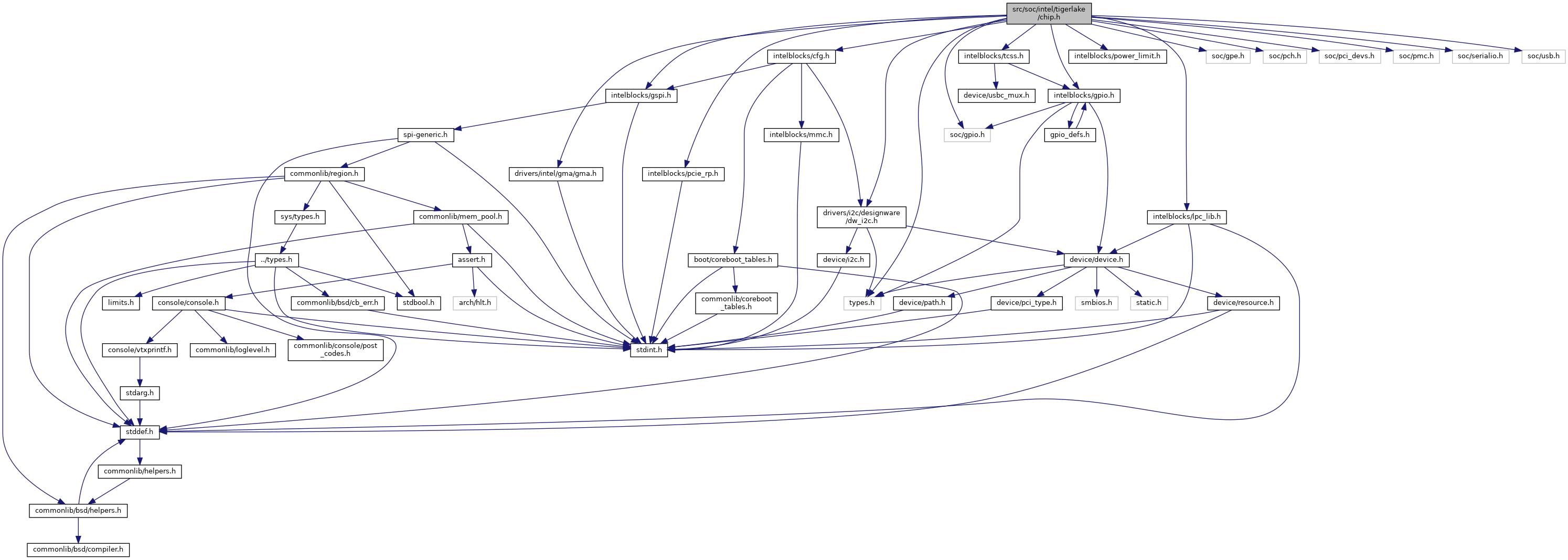

#include <drivers/i2c/designware/dw_i2c.h>

#include <drivers/intel/gma/gma.h>

#include <intelblocks/cfg.h>

#include <intelblocks/gpio.h>

#include <intelblocks/gspi.h>

#include <intelblocks/lpc_lib.h>

#include <intelblocks/pcie_rp.h>

#include <intelblocks/power_limit.h>

#include <intelblocks/tcss.h>

#include <soc/gpe.h>

#include <soc/gpio.h>

#include <soc/pch.h>

#include <soc/pci_devs.h>

#include <soc/pmc.h>

#include <soc/serialio.h>

#include <soc/usb.h>

#include <types.h>

Go to the source code of this file.

|

| enum | soc_intel_tigerlake_power_limits {

POWER_LIMITS_U_2_CORE

, POWER_LIMITS_U_4_CORE

, POWER_LIMITS_Y_2_CORE

, POWER_LIMITS_Y_4_CORE

,

POWER_LIMITS_H_6_CORE

, POWER_LIMITS_H_8_CORE

, POWER_LIMITS_MAX

} |

| |

| enum | fivr_enable_states {

FIVR_ENABLE_S0i1_S0i2 = BIT(0)

, FIVR_ENABLE_S0i3 = BIT(1)

, FIVR_ENABLE_S3 = BIT(2)

, FIVR_ENABLE_S4 = BIT(3)

,

FIVR_ENABLE_S5 = BIT(4)

, FIVR_ENABLE_S0i1_S0i2 = BIT(0)

, FIVR_ENABLE_S0i3 = BIT(1)

, FIVR_ENABLE_S3 = BIT(2)

,

FIVR_ENABLE_S4 = BIT(3)

, FIVR_ENABLE_S5 = BIT(4)

} |

| |

| enum | fivr_voltage_supported {

FIVR_RET_ACTIVE_SWITCH_SUPPORT = BIT(0)

, FIVR_VOLTAGE_NORMAL = BIT(1)

, FIVR_VOLTAGE_MIN_ACTIVE = BIT(2)

, FIVR_VOLTAGE_MIN_RETENTION = BIT(3)

,

FIVR_VOLTAGE_NORMAL = BIT(1)

, FIVR_VOLTAGE_MIN_ACTIVE = BIT(2)

, FIVR_VOLTAGE_MIN_RETENTION = BIT(3)

} |

| |

| enum | lpm_state_mask {

LPM_S0i2_0 = BIT(0)

, LPM_S0i2_1 = BIT(1)

, LPM_S0i2_2 = BIT(2)

, LPM_S0i3_0 = BIT(3)

,

LPM_S0i3_1 = BIT(4)

, LPM_S0i3_2 = BIT(5)

, LPM_S0i3_3 = BIT(6)

, LPM_S0i3_4 = BIT(7)

,

LPM_S0iX_ALL

, LPM_S0i2_0 = BIT(0)

, LPM_S0i2_1 = BIT(1)

, LPM_S0i2_2 = BIT(2)

,

LPM_S0i3_0 = BIT(3)

, LPM_S0i3_1 = BIT(4)

, LPM_S0i3_2 = BIT(5)

, LPM_S0i3_3 = BIT(6)

,

LPM_S0i3_4 = BIT(7)

, LPM_S0iX_ALL

} |

| |

| enum | slew_rate {

SLEW_FAST_2

, SLEW_FAST_4

, SLEW_FAST_8

, SLEW_FAST_16

,

SLEW_FAST_2

, SLEW_FAST_4

, SLEW_FAST_8

, SLEW_FAST_16

} |

| |

◆ FIVR_ENABLE_ALL_SX

| #define FIVR_ENABLE_ALL_SX |

Value:

Definition at line 63 of file chip.h.

◆ MAX_HD_AUDIO_DMIC_LINKS

| #define MAX_HD_AUDIO_DMIC_LINKS 2 |

◆ MAX_HD_AUDIO_SNDW_LINKS

| #define MAX_HD_AUDIO_SNDW_LINKS 4 |

◆ MAX_HD_AUDIO_SSP_LINKS

| #define MAX_HD_AUDIO_SSP_LINKS 6 |

◆ config_t

Definition at line 1 of file chip.h.

◆ fivr_enable_states

| Enumerator |

|---|

| FIVR_ENABLE_S0i1_S0i2 | |

| FIVR_ENABLE_S0i3 | |

| FIVR_ENABLE_S3 | |

| FIVR_ENABLE_S4 | |

| FIVR_ENABLE_S5 | |

| FIVR_ENABLE_S0i1_S0i2 | |

| FIVR_ENABLE_S0i3 | |

| FIVR_ENABLE_S3 | |

| FIVR_ENABLE_S4 | |

| FIVR_ENABLE_S5 | |

Definition at line 43 of file chip.h.

◆ fivr_voltage_supported

| Enumerator |

|---|

| FIVR_RET_ACTIVE_SWITCH_SUPPORT | |

| FIVR_VOLTAGE_NORMAL | |

| FIVR_VOLTAGE_MIN_ACTIVE | |

| FIVR_VOLTAGE_MIN_RETENTION | |

| FIVR_VOLTAGE_NORMAL | |

| FIVR_VOLTAGE_MIN_ACTIVE | |

| FIVR_VOLTAGE_MIN_RETENTION | |

Definition at line 57 of file chip.h.

◆ lpm_state_mask

| Enumerator |

|---|

| LPM_S0i2_0 | |

| LPM_S0i2_1 | |

| LPM_S0i2_2 | |

| LPM_S0i3_0 | |

| LPM_S0i3_1 | |

| LPM_S0i3_2 | |

| LPM_S0i3_3 | |

| LPM_S0i3_4 | |

| LPM_S0iX_ALL | |

| LPM_S0i2_0 | |

| LPM_S0i2_1 | |

| LPM_S0i2_2 | |

| LPM_S0i3_0 | |

| LPM_S0i3_1 | |

| LPM_S0i3_2 | |

| LPM_S0i3_3 | |

| LPM_S0i3_4 | |

| LPM_S0iX_ALL | |

Definition at line 67 of file chip.h.

◆ slew_rate

| Enumerator |

|---|

| SLEW_FAST_2 | |

| SLEW_FAST_4 | |

| SLEW_FAST_8 | |

| SLEW_FAST_16 | |

| SLEW_FAST_2 | |

| SLEW_FAST_4 | |

| SLEW_FAST_8 | |

| SLEW_FAST_16 | |

Definition at line 88 of file chip.h.

◆ soc_intel_tigerlake_power_limits

| Enumerator |

|---|

| POWER_LIMITS_U_2_CORE | |

| POWER_LIMITS_U_4_CORE | |

| POWER_LIMITS_Y_2_CORE | |

| POWER_LIMITS_Y_4_CORE | |

| POWER_LIMITS_H_6_CORE | |

| POWER_LIMITS_H_8_CORE | |

| POWER_LIMITS_MAX | |

Definition at line 29 of file chip.h.