|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

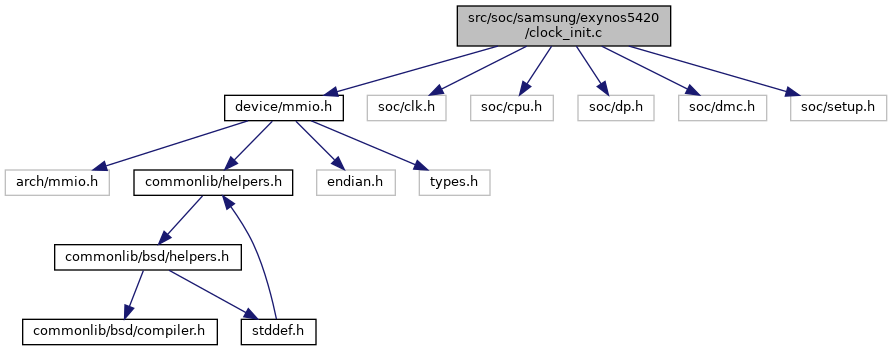

#include <device/mmio.h>#include <soc/clk.h>#include <soc/cpu.h>#include <soc/dp.h>#include <soc/dmc.h>#include <soc/setup.h>

Go to the source code of this file.

Functions | |

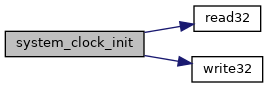

| void | system_clock_init (void) |

| void | clock_gate (void) |

Definition at line 202 of file clock_init.c.

Definition at line 12 of file clock_init.c.

References exynos5_clock::apll_con0, exynos5_clock::apll_con1, APLL_CON1_VAL, APLL_FOUT, exynos5_clock::apll_lock, APLL_LOCK_VAL, AUDIO0_SEL_EPLL, exynos5_clock::bpll_con0, exynos5_clock::bpll_con1, BPLL_CON1_VAL, exynos5_clock::bpll_lock, BPLL_LOCK_VAL, CLK_DIV2_RATIO, CLK_DIV4_RATIO, CLK_DIV_CDREX0_VAL, CLK_DIV_CDREX1_VAL, CLK_DIV_CPERI1_VAL, CLK_DIV_CPU0_VAL, CLK_DIV_DISP1_0_VAL, CLK_DIV_FSYS0_VAL, CLK_DIV_FSYS1_VAL, CLK_DIV_FSYS2_VAL, CLK_DIV_G2D, CLK_DIV_ISP0_VAL, CLK_DIV_ISP1_VAL, CLK_DIV_KFC_VAL, CLK_DIV_PERIC0_VAL, CLK_DIV_PERIC1_VAL, CLK_DIV_PERIC2_VAL, CLK_DIV_PERIC3_VAL, CLK_DIV_PERIC4_VAL, CLK_DIV_TOP0_VAL, CLK_DIV_TOP1_VAL, CLK_DIV_TOP2_VAL, CLK_SRC_CDREX_VAL, CLK_SRC_CPU_VAL, CLK_SRC_DISP1_0_VAL, CLK_SRC_FSYS0_VAL, CLK_SRC_ISP_VAL, CLK_SRC_KFC_VAL, CLK_SRC_PERIC0_VAL, CLK_SRC_PERIC1_VAL, CLK_SRC_TOP0_VAL, CLK_SRC_TOP1_VAL, CLK_SRC_TOP2_VAL, CLK_SRC_TOP3_VAL, CLK_SRC_TOP4_VAL, CLK_SRC_TOP5_VAL, CLK_SRC_TOP6_VAL, CLK_SRC_TOP7_VAL, clrbits32, exynos5_clock::cpll_con0, exynos5_clock::cpll_con1, CPLL_CON1_VAL, exynos5_clock::cpll_lock, CPLL_LOCK_VAL, DIV_MAU_VAL, DPLL_CON1_VAL, DPLL_LOCK_VAL, exynos5_clock::epll_con0, exynos5_clock::epll_con1, EPLL_CON1_VAL, exynos5_clock::epll_con2, EPLL_CON2_VAL, exynos5_clock::epll_lock, EPLL_LOCK_VAL, exynos_clock, exynos_mct, exynos5_mct::g_tcon, HPM_RATIO, IPLL_CON1_VAL, IPLL_LOCK_VAL, KPLL_CON1_VAL, KPLL_FOUT, KPLL_LOCK_VAL, exynos5_clock::mpll_con0, exynos5_clock::mpll_con1, MPLL_CON1_VAL, exynos5_clock::mpll_lock, MPLL_LOCK_VAL, MUX_HPM_SEL_MASK, PLL_LOCKED, read32(), RPLL_CON1_VAL, RPLL_CON2_VAL, RPLL_LOCK_VAL, set_pll, setbits32, SPLL_CON1_VAL, SPLL_LOCK_VAL, SRC_KFC_HPM_SEL, val, exynos5_clock::vpll_con0, exynos5_clock::vpll_con1, VPLL_CON1_VAL, exynos5_clock::vpll_lock, VPLL_LOCK_VAL, and write32().