|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

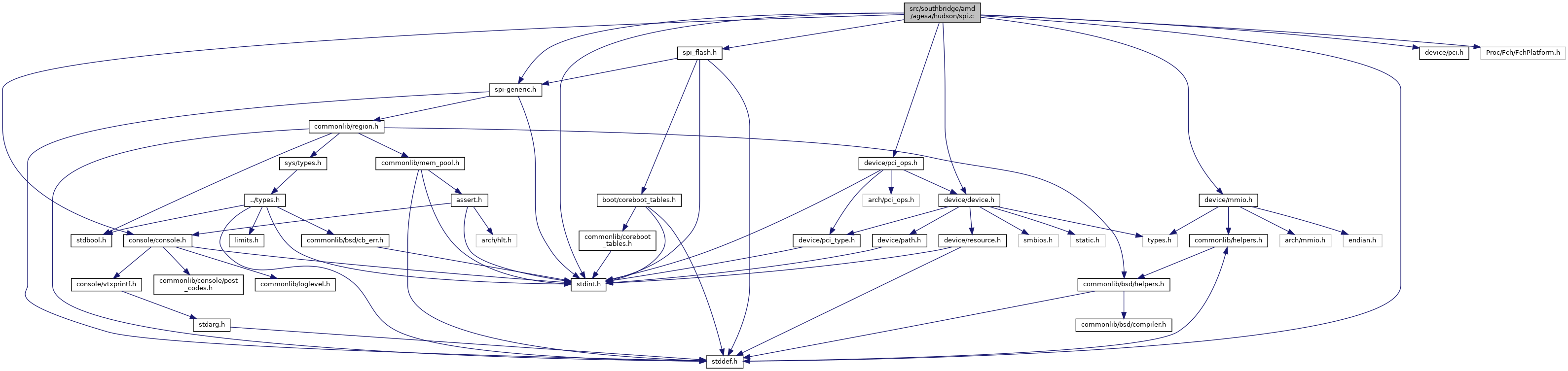

#include <stdint.h>#include <device/mmio.h>#include <console/console.h>#include <spi_flash.h>#include <spi-generic.h>#include <device/device.h>#include <device/pci.h>#include <device/pci_ops.h>#include <stddef.h>#include <Proc/Fch/FchPlatform.h>

Go to the source code of this file.

Macros | |

| #define | SPI_REG_OPCODE 0x0 |

| #define | SPI_REG_CNTRL01 0x1 |

| #define | SPI_REG_CNTRL02 0x2 |

| #define | CNTRL02_FIFO_RESET (1 << 4) |

| #define | CNTRL02_EXEC_OPCODE (1 << 0) |

| #define | SPI_REG_CNTRL03 0x3 |

| #define | CNTRL03_SPIBUSY (1 << 7) |

| #define | SPI_REG_FIFO 0xc |

| #define | SPI_REG_CNTRL11 0xd |

| #define | CNTRL11_FIFOPTR_MASK 0x07 |

| #define | AMD_SB_SPI_TX_LEN 8 |

Functions | |

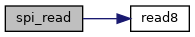

| static uint8_t | spi_read (uint8_t reg) |

| static void | spi_write (uint8_t reg, uint8_t val) |

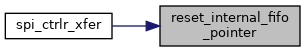

| static void | reset_internal_fifo_pointer (void) |

| static void | execute_command (void) |

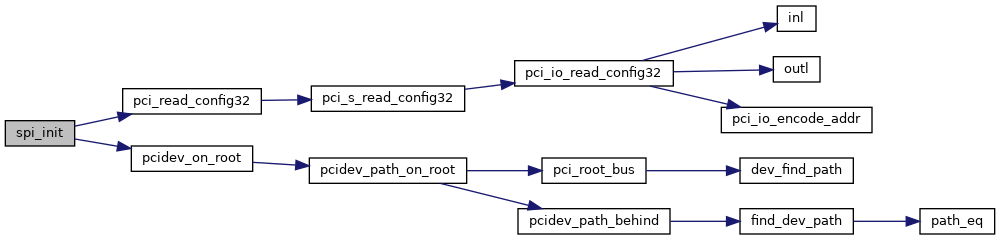

| void | spi_init (void) |

| Init all SPI controllers with default values and enable all SPI controller. More... | |

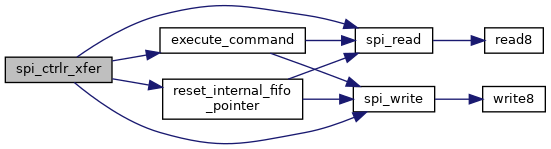

| static int | spi_ctrlr_xfer (const struct spi_slave *slave, const void *dout, size_t bytesout, void *din, size_t bytesin) |

| int | chipset_volatile_group_begin (const struct spi_flash *flash) |

| int | chipset_volatile_group_end (const struct spi_flash *flash) |

| static int | xfer_vectors (const struct spi_slave *slave, struct spi_op vectors[], size_t count) |

Variables | |

| static uintptr_t | spibar |

| static const struct spi_ctrlr | spi_ctrlr |

| const struct spi_ctrlr_buses | spi_ctrlr_bus_map [] |

| const size_t | spi_ctrlr_bus_map_count = ARRAY_SIZE(spi_ctrlr_bus_map) |

| int chipset_volatile_group_begin | ( | const struct spi_flash * | flash | ) |

| int chipset_volatile_group_end | ( | const struct spi_flash * | flash | ) |

Definition at line 55 of file spi.c.

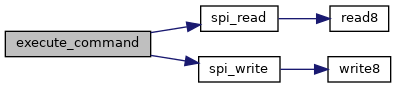

References CNTRL02_EXEC_OPCODE, CNTRL03_SPIBUSY, spi_read(), SPI_REG_CNTRL02, SPI_REG_CNTRL03, and spi_write().

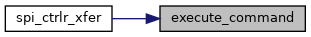

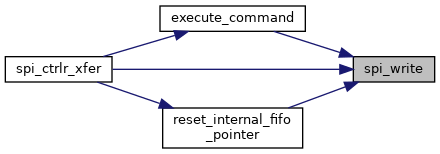

Referenced by spi_ctrlr_xfer().

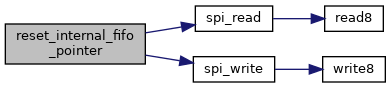

Definition at line 44 of file spi.c.

References CNTRL02_FIFO_RESET, CNTRL11_FIFOPTR_MASK, spi_read(), SPI_REG_CNTRL02, SPI_REG_CNTRL11, and spi_write().

Referenced by spi_ctrlr_xfer().

|

static |

Definition at line 75 of file spi.c.

References AMD_SB_SPI_TX_LEN, BIOS_DEBUG, CONFIG, count, execute_command(), printk, reset_internal_fifo_pointer(), spi_read(), SPI_REG_CNTRL01, SPI_REG_FIFO, SPI_REG_OPCODE, and spi_write().

Init all SPI controllers with default values and enable all SPI controller.

Definition at line 67 of file spi.c.

References pci_read_config32(), pcidev_on_root(), and spibar.

Definition at line 34 of file spi.c.

References read8(), and spibar.

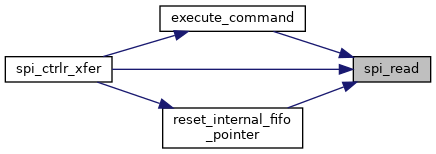

Referenced by execute_command(), reset_internal_fifo_pointer(), and spi_ctrlr_xfer().

Definition at line 39 of file spi.c.

References spibar, val, and write8().

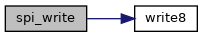

Referenced by execute_command(), reset_internal_fifo_pointer(), and spi_ctrlr_xfer().

| const struct spi_ctrlr_buses spi_ctrlr_bus_map[] |

| const size_t spi_ctrlr_bus_map_count = ARRAY_SIZE(spi_ctrlr_bus_map) |

|

static |

Definition at line 32 of file spi.c.

Referenced by fast_spi_clear_outstanding_status(), fast_spi_lock_bar(), fast_spi_pr_dlock(), fast_spi_set_opcode_menu(), fast_spi_set_strap_msg_data(), fast_spi_vscc0_lock(), spi_init(), spi_read(), and spi_write().