|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Enumerations | |

| enum | { BLSP1_UART1 , BLSP1_UART2 } |

Functions | |

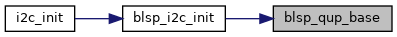

| static void * | blsp_qup_base (blsp_qup_id_t id) |

| #define BLSP_MINI_CORE_I2C (0x2u << BLSP_MINI_CORE_SHIFT) |

| #define BLSP_MINI_CORE_MASK (0xfu << BLSP_MINI_CORE_SHIFT) |

| #define clrsetbits32_i | ( | addr, | |

| clear, | |||

| set | |||

| ) | clrsetbits32(((void *)(addr)), (clear), (set)) |

| #define GCC_BLSP1_QUP1_I2C_APPS_CBCR (MSM_CLK_CTL_BASE + 0x2008) |

| #define GCC_BLSP1_QUP1_I2C_APPS_CFG_RCGR (MSM_CLK_CTL_BASE + 0x2010) |

| #define GCC_BLSP1_QUP1_I2C_APPS_CMD_RCGR (MSM_CLK_CTL_BASE + 0x200c) |

| #define GCC_BLSP1_QUP2_I2C_APPS_CBCR (MSM_CLK_CTL_BASE + 0x3010) |

| #define GCC_BLSP1_QUP2_I2C_APPS_CFG_RCGR (MSM_CLK_CTL_BASE + 0x3004) |

| #define GCC_BLSP1_QUP2_I2C_APPS_CMD_RCGR (MSM_CLK_CTL_BASE + 0x3000) |

| #define GCC_BLSP1_UART_APPS_CBCR | ( | x | ) | (GCC_BLSP1_UART_BCR(x) + 4) |

| #define GCC_BLSP1_UART_APPS_CFG_RCGR | ( | x | ) | (GCC_BLSP1_UART_APPS_CMD_RCGR(x) + 4) |

| #define GCC_BLSP1_UART_APPS_CMD_RCGR | ( | x | ) | (GCC_BLSP1_UART_APPS_CBCR(x) + 8) |

| #define GCC_BLSP1_UART_APPS_D | ( | x | ) | (GCC_BLSP1_UART_APPS_N(x) + 4) |

| #define GCC_BLSP1_UART_APPS_M | ( | x | ) | (GCC_BLSP1_UART_APPS_CFG_RCGR(x) + 4) |

| #define GCC_BLSP1_UART_APPS_N | ( | x | ) | (GCC_BLSP1_UART_APPS_M(x) + 4) |

| #define GCC_BLSP1_UART_BCR | ( | x | ) | (GCC_BLSP1_UART_BCR_BASE + (x) * 0xff0) |

| #define GCC_BLSP1_UART_BCR_BASE (GCC_CLK_CTL_REG + 0x2038) |

| #define GCC_BLSP1_UART_MISC | ( | x | ) | (GCC_BLSP1_UART_APPS_D(x) + 4) |

| #define GCC_CLK_BRANCH_ENA (GCC_CLK_CTL_REG + 0x6000) |

| #define GCNT_CNTCR (GCNT_GLOBAL_CTRL_BASE + 0x1000) |

| #define GCNT_CNTCV_HI (GCNT_GLOBAL_CTRL_BASE + 0x2004) |

| #define GCNT_CNTCV_LO (GCNT_GLOBAL_CTRL_BASE + 0x2000) |

| #define GCNT_GLB_CNTCV_HI (GCNT_GLOBAL_CTRL_BASE + 0x100c) |

| #define GCNT_GLB_CNTCV_LO (GCNT_GLOBAL_CTRL_BASE + 0x1008) |

| #define GPIO_CONFIG_ADDR | ( | x | ) | (TLMM_BASE_ADDR + 0x1000 * (x)) |

| #define GPIO_IN_OUT_ADDR | ( | x | ) | (GPIO_CONFIG_ADDR(x) + 4) |

| #define MSM_CLK_CTL_BASE GCC_CLK_CTL_REG |

|

inlinestatic |

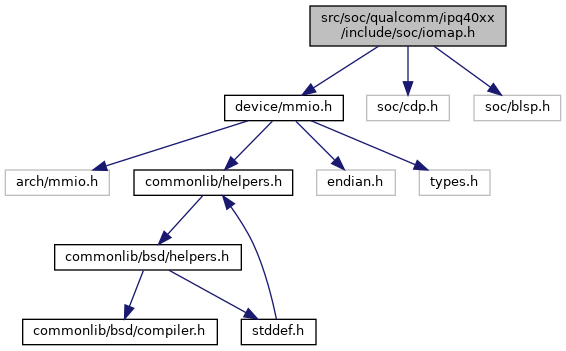

Definition at line 103 of file iomap.h.

References BLSP1_QUP0_BASE, BLSP1_QUP1_BASE, BLSP1_QUP2_BASE, BLSP1_QUP3_BASE, BLSP_QUP_ID_0, BLSP_QUP_ID_1, BLSP_QUP_ID_2, BLSP_QUP_ID_3, and NULL.

Referenced by blsp_i2c_init().