|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

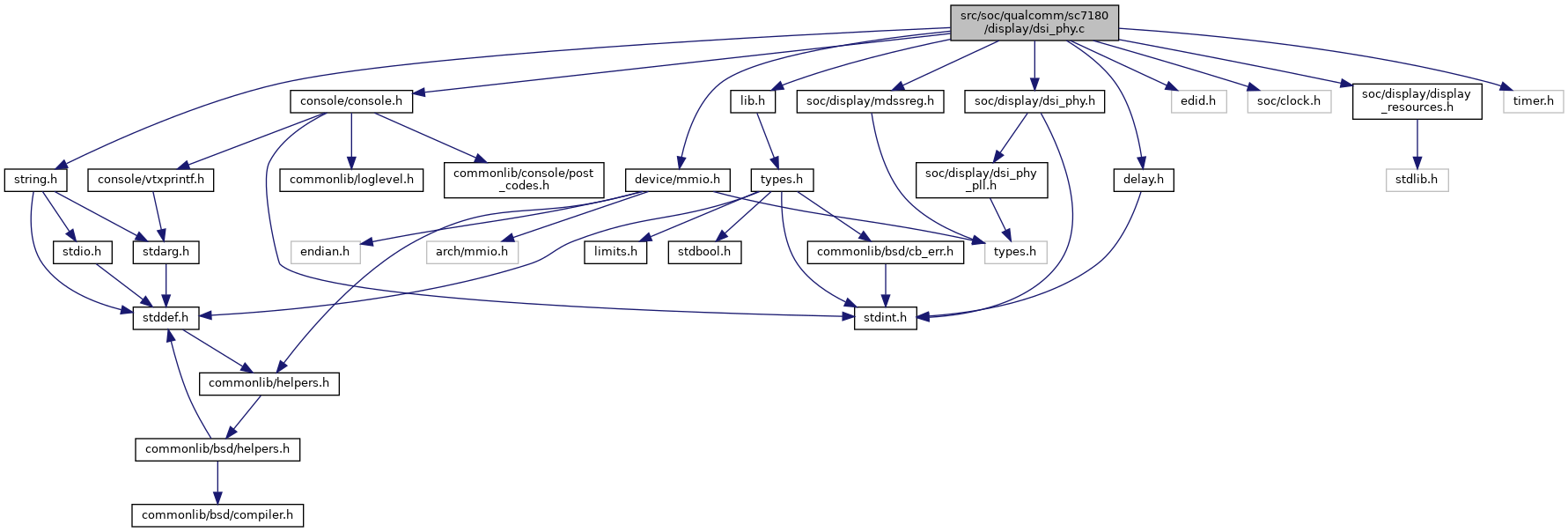

#include <console/console.h>#include <delay.h>#include <device/mmio.h>#include <edid.h>#include <lib.h>#include <soc/clock.h>#include <soc/display/dsi_phy.h>#include <soc/display/mdssreg.h>#include <soc/display/display_resources.h>#include <string.h>#include <timer.h>

Go to the source code of this file.

Data Structures | |

| struct | dsi_phy_divider_lut_entry_type |

| struct | dsi_phy_configtype |

Macros | |

| #define | HAL_DSI_PHY_PLL_READY_TIMEOUT_MS 150 /* ~15 ms */ |

| #define | HAL_DSI_PHY_REFGEN_TIMEOUT_MS 150 /* ~15 ms */ |

| #define | DSI_MAX_REFRESH_RATE 95 |

| #define | DSI_MIN_REFRESH_RATE 15 |

| #define | HAL_DSI_PLL_VCO_MIN_MHZ_2_2_0 1000 |

| #define | S_DIV_ROUND_UP(n, d) (((n) >= 0) ? (((n) + (d) - 1) / (d)) : (((n) - (d) + 1) / (d))) |

| #define | mult_frac(x, numer, denom) |

Enumerations | |

| enum | dsi_laneid_type { DSI_LANEID_0 = 0 , DSI_LANEID_1 , DSI_LANEID_2 , DSI_LANEID_3 , DSI_LANEID_CLK , DSI_LANEID_MAX , DSI_LANEID_FORCE_32BIT = 0x7FFFFFFF } |

Variables | |

| static struct dsi_phy_divider_lut_entry_type | pll_dividerlut_dphy [] |

| #define mult_frac | ( | x, | |

| numer, | |||

| denom | |||

| ) |

| #define S_DIV_ROUND_UP | ( | n, | |

| d | |||

| ) | (((n) >= 0) ? (((n) + (d) - 1) / (d)) : (((n) - (d) + 1) / (d))) |

| enum dsi_laneid_type |

|

static |

Definition at line 675 of file dsi_phy.c.

References BIOS_INFO, KHz, edid::mode, edid_mode::pixel_clock, and printk.

|

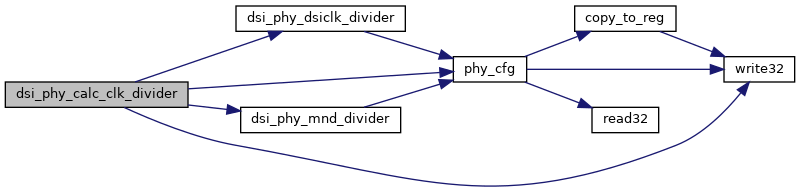

static |

Definition at line 536 of file dsi_phy.c.

References ARRAY_SIZE, dsi0_phy, dsi_phy_dsiclk_divider(), dsi_phy_mnd_divider(), HAL_DSI_PLL_VCO_MIN_MHZ_2_2_0, phy_cfg(), dsi_phy_regs::phy_cmn_clk_cfg0, dsi_phy_divider_lut_entry_type::phy_post_div, pll_dividerlut_dphy, dsi_phy_divider_lut_entry_type::pll_post_div, and write32().

|

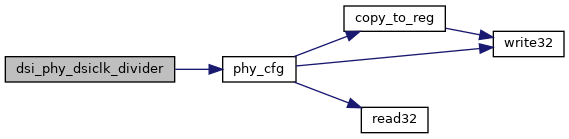

static |

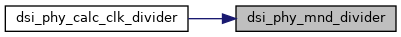

Definition at line 523 of file dsi_phy.c.

References phy_cfg().

Referenced by dsi_phy_calc_clk_divider().

|

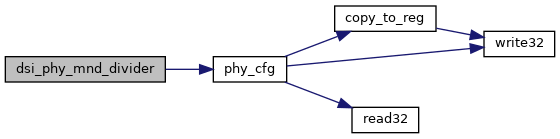

static |

Definition at line 489 of file dsi_phy.c.

References phy_cfg().

Referenced by dsi_phy_calc_clk_divider().

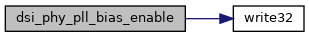

Definition at line 476 of file dsi_phy.c.

References phy_pll_qlink, dsi_phy_pll_qlink_regs::pll_system_muxes, and write32().

|

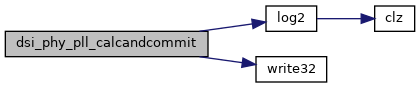

static |

Definition at line 612 of file dsi_phy.c.

References log2(), phy_pll_qlink, dsi_phy_pll_qlink_regs::pll_outdiv_rate, dsi_phy_divider_lut_entry_type::pll_post_div, dsi_phy_configtype::pll_post_div, and write32().

|

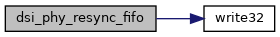

static |

Definition at line 411 of file dsi_phy.c.

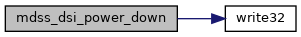

References dsi0_phy, dsi_phy_regs::phy_cmn_rbuf_ctrl, and write32().

Definition at line 450 of file dsi_phy.c.

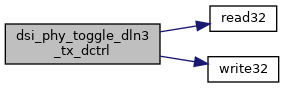

References dsi_phy_regs::dln0_tx_dctrl, dsi0_phy, DSI_LANEID_3, dsi_phy_regs::phy_ln_regs, read32(), and write32().

Definition at line 192 of file dsi_phy.c.

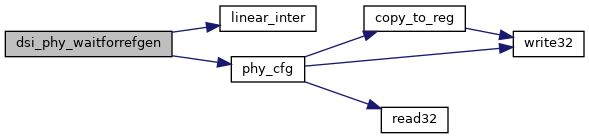

References BIOS_INFO, msm_dsi_phy_ctrl::clk_post, msm_dsi_phy_ctrl::clk_pre, msm_dsi_phy_ctrl::clk_pre_inc_by_2, msm_dsi_phy_ctrl::clk_prepare, msm_dsi_phy_ctrl::clk_trail, msm_dsi_phy_ctrl::clk_zero, DIV_ROUND_UP, msm_dsi_phy_ctrl::half_byte_clk_en, msm_dsi_phy_ctrl::hs_exit, msm_dsi_phy_ctrl::hs_prepare, msm_dsi_phy_ctrl::hs_rqst, msm_dsi_phy_ctrl::hs_trail, msm_dsi_phy_ctrl::hs_zero, linear_inter(), MAX, mult_frac, phy_cfg(), printk, S_DIV_ROUND_UP, msm_dsi_phy_ctrl::ta_get, msm_dsi_phy_ctrl::ta_go, and msm_dsi_phy_ctrl::ta_sure.

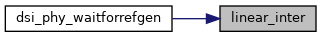

Definition at line 85 of file dsi_phy.c.

References MAX, and S_DIV_ROUND_UP.

Referenced by dsi_phy_waitforrefgen().

|

static |

Definition at line 192 of file dsi_phy.c.

Referenced by mdss_dsi_phy_setup().

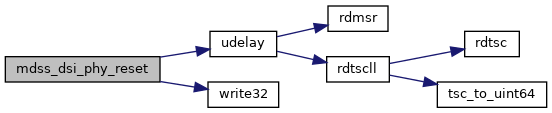

Definition at line 98 of file dsi_phy.c.

References dsi0_phy, dsi_phy_regs::phy_cmn_ctrl1, udelay(), and write32().

Referenced by mdss_dsi_phy_setup().

Definition at line 402 of file dsi_phy.c.

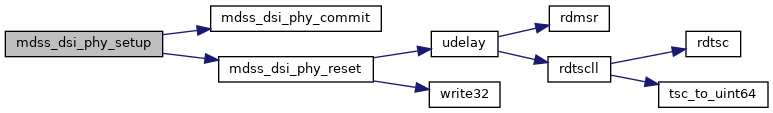

References mdss_dsi_phy_commit(), and mdss_dsi_phy_reset().

|

static |

Definition at line 117 of file dsi_phy.c.

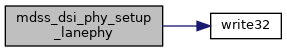

References dsi_phy_regs::dln0_cfg, dsi_phy_regs::dln0_hstx_str_ctrl, dsi_phy_regs::dln0_lprx_ctrl, dsi_phy_regs::dln0_lptx_str_ctrl, dsi_phy_regs::dln0_offset_bot_ctrl, dsi_phy_regs::dln0_offset_top_ctrl, dsi_phy_regs::dln0_pin_swap, dsi_phy_regs::dln0_tx_dctrl, dsi0_phy, DSI_LANEID_0, DSI_LANEID_CLK, dsi_phy_regs::phy_ln_regs, and write32().

|

static |

Definition at line 105 of file dsi_phy.c.

References dsi0_phy, dsi_phy_regs::phy_cmn_ctrl0, dsi_phy_regs::phy_cmn_pll_ctrl, dsi_phy_regs::phy_cmn_rbuf_ctrl, and write32().

|

static |

Definition at line 1 of file dsi_phy.c.

Referenced by dsi_phy_calc_clk_divider().