|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

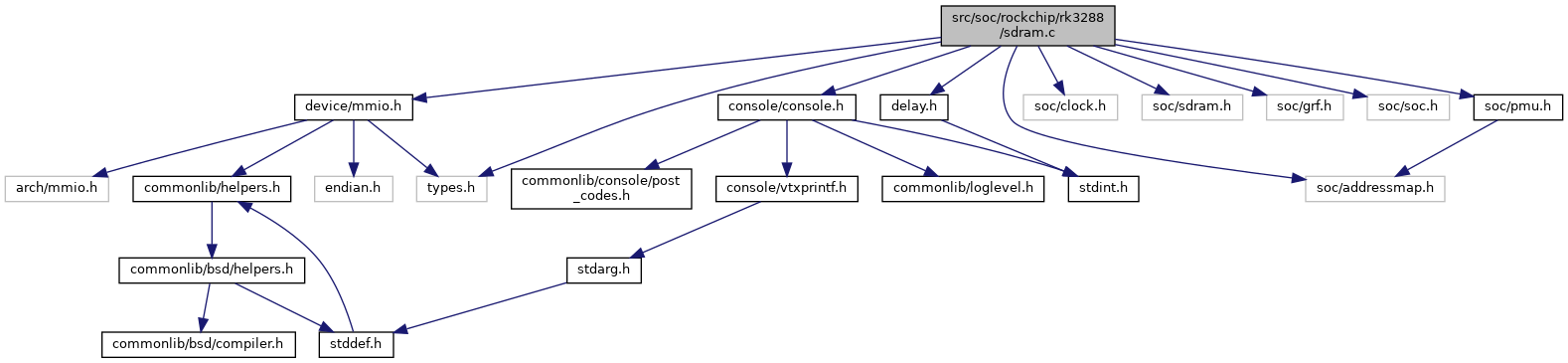

#include <device/mmio.h>#include <console/console.h>#include <delay.h>#include <soc/addressmap.h>#include <soc/clock.h>#include <soc/sdram.h>#include <soc/grf.h>#include <soc/soc.h>#include <soc/pmu.h>#include <types.h>

Go to the source code of this file.

Data Structures | |

| struct | rk3288_ddr_pctl_regs |

| struct | rk3288_ddr_publ_datx |

| struct | rk3288_ddr_publ_regs |

| struct | rk3288_msch_regs |

Macros | |

| #define | DFI_INIT_START (1 << 0) |

| #define | DFI_DRAM_CLK_SR_EN (1 << 0) |

| #define | DFI_DRAM_CLK_DPD_EN (1 << 1) |

| #define | DFI_PARITY_INTR_EN (1 << 0) |

| #define | DFI_PARITY_EN (1 << 1) |

| #define | TLP_RESP_TIME(n) (n << 16) |

| #define | LP_SR_EN (1 << 8) |

| #define | LP_PD_EN (1 << 0) |

| #define | TCTRL_DELAY_TIME(n) (n << 0) |

| #define | TPHY_WRDATA_TIME(n) (n << 0) |

| #define | TPHY_RDLAT_TIME(n) (n << 0) |

| #define | TDRAM_CLK_DIS_TIME(n) (n << 0) |

| #define | TDRAM_CLK_EN_TIME(n) (n << 0) |

| #define | RANK0_ODT_WRITE_SEL (1 << 3) |

| #define | RANK1_ODT_WRITE_SEL (1 << 11) |

| #define | ODT_LEN_BL8_W(n) (n<<16) |

| #define | ACDLLCR_DLLDIS (1 << 31) |

| #define | ACDLLCR_DLLSRST (1 << 30) |

| #define | DXDLLCR_DLLDIS (1 << 31) |

| #define | DXDLLCR_DLLSRST (1 << 30) |

| #define | DLLGCR_SBIAS (1 << 30) |

| #define | DQSRTT (1 << 9) |

| #define | DQRTT (1 << 10) |

| #define | PIR_INIT (1 << 0) |

| #define | PIR_DLLSRST (1 << 1) |

| #define | PIR_DLLLOCK (1 << 2) |

| #define | PIR_ZCAL (1 << 3) |

| #define | PIR_ITMSRST (1 << 4) |

| #define | PIR_DRAMRST (1 << 5) |

| #define | PIR_DRAMINIT (1 << 6) |

| #define | PIR_QSTRN (1 << 7) |

| #define | PIR_RVTRN (1 << 8) |

| #define | PIR_ICPC (1 << 16) |

| #define | PIR_DLLBYP (1 << 17) |

| #define | PIR_CTLDINIT (1 << 18) |

| #define | PIR_CLRSR (1 << 28) |

| #define | PIR_LOCKBYP (1 << 29) |

| #define | PIR_ZCALBYP (1 << 30) |

| #define | PIR_INITBYP (1u << 31) |

| #define | PGCR_DFTLMT(n) ((n) << 3) |

| #define | PGCR_DFTCMP(n) ((n) << 2) |

| #define | PGCR_DQSCFG(n) ((n) << 1) |

| #define | PGCR_ITMDMD(n) ((n) << 0) |

| #define | PGSR_IDONE (1 << 0) |

| #define | PGSR_DLDONE (1 << 1) |

| #define | PGSR_ZCDONE (1 << 2) |

| #define | PGSR_DIDONE (1 << 3) |

| #define | PGSR_DTDONE (1 << 4) |

| #define | PGSR_DTERR (1 << 5) |

| #define | PGSR_DTIERR (1 << 6) |

| #define | PGSR_DFTERR (1 << 7) |

| #define | PGSR_RVERR (1 << 8) |

| #define | PGSR_RVEIRR (1 << 9) |

| #define | PRT_ITMSRST(n) ((n) << 18) |

| #define | PRT_DLLLOCK(n) ((n) << 6) |

| #define | PRT_DLLSRST(n) ((n) << 0) |

| #define | PRT_DINIT0(n) ((n) << 0) |

| #define | PRT_DINIT1(n) ((n) << 19) |

| #define | PRT_DINIT2(n) ((n) << 0) |

| #define | PRT_DINIT3(n) ((n) << 17) |

| #define | DDRMD_LPDDR 0 |

| #define | DDRMD_DDR 1 |

| #define | DDRMD_DDR2 2 |

| #define | DDRMD_DDR3 3 |

| #define | DDRMD_LPDDR2_LPDDR3 4 |

| #define | DDRMD_MSK (7 << 0) |

| #define | DDRMD_CFG(n) ((n) << 0) |

| #define | PDQ_MSK (7 << 4) |

| #define | PDQ_CFG(n) ((n) << 4) |

| #define | DQSNRES_MSK (0x0f << 8) |

| #define | DQSNRES_CFG(n) ((n) << 8) |

| #define | DQSRES_MSK (0x0f << 4) |

| #define | DQSRES_CFG(n) ((n) << 4) |

| #define | TDQSCKMAX_VAL(n) (((n) >> 27) & 7) |

| #define | TDQSCK_VAL(n) (((n) >> 24) & 7) |

| #define | DQSGX_MSK (0x07 << 5) |

| #define | DQSGX_CFG(n) ((n) << 5) |

| #define | DQSGE_MSK (0x07 << 8) |

| #define | DQSGE_CFG(n) ((n) << 8) |

| #define | INIT_STATE (0) |

| #define | CFG_STATE (1) |

| #define | GO_STATE (2) |

| #define | SLEEP_STATE (3) |

| #define | WAKEUP_STATE (4) |

| #define | LP_TRIG_VAL(n) (((n) >> 4) & 7) |

| #define | PCTL_STAT_MSK (7) |

| #define | INIT_MEM (0) |

| #define | CONF (1) |

| #define | CONF_REQ (2) |

| #define | ACCESS (3) |

| #define | ACCESS_REQ (4) |

| #define | LOW_POWER (5) |

| #define | LOW_POWER_ENTRY_REQ (6) |

| #define | LOW_POWER_EXIT_REQ (7) |

| #define | PD_OUTPUT(n) ((n) << 0) |

| #define | PU_OUTPUT(n) ((n) << 5) |

| #define | PD_ONDIE(n) ((n) << 10) |

| #define | PU_ONDIE(n) ((n) << 15) |

| #define | ZDEN(n) ((n) << 28) |

| #define | SBIAS_BYPASS (1 << 23) |

| #define | MDDR_LPDDR2_CLK_STOP_IDLE(n) ((n) << 24) |

| #define | PD_IDLE(n) ((n) << 8) |

| #define | MDDR_EN (2 << 22) |

| #define | LPDDR2_EN (3 << 22) |

| #define | DDR2_EN (0 << 5) |

| #define | DDR3_EN (1 << 5) |

| #define | LPDDR2_S2 (0 << 6) |

| #define | LPDDR2_S4 (1 << 6) |

| #define | MDDR_LPDDR2_BL_2 (0 << 20) |

| #define | MDDR_LPDDR2_BL_4 (1 << 20) |

| #define | MDDR_LPDDR2_BL_8 (2 << 20) |

| #define | MDDR_LPDDR2_BL_16 (3 << 20) |

| #define | DDR2_DDR3_BL_4 (0) |

| #define | DDR2_DDR3_BL_8 (1) |

| #define | TFAW_CFG(n) (((n)-4) << 18) |

| #define | PD_EXIT_SLOW (0 << 17) |

| #define | PD_EXIT_FAST (1 << 17) |

| #define | PD_TYPE(n) ((n) << 16) |

| #define | BURSTLENGTH_CFG(n) (((n) >> 1) << 20) |

| #define | POWER_UP_START (1 << 0) |

| #define | POWER_UP_DONE (1 << 0) |

| #define | DESELECT_CMD (0) |

| #define | PREA_CMD (1) |

| #define | REF_CMD (2) |

| #define | MRS_CMD (3) |

| #define | ZQCS_CMD (4) |

| #define | ZQCL_CMD (5) |

| #define | RSTL_CMD (6) |

| #define | MRR_CMD (8) |

| #define | DPDE_CMD (9) |

| #define | LPDDR2_MA(n) (((n) & 0xff) << 4) |

| #define | LPDDR2_OP(n) (((n) & 0xff) << 12) |

| #define | START_CMD (1u << 31) |

| #define | BUSWRTORD(n) ((n) << 4) |

| #define | BUSRDTOWR(n) ((n) << 2) |

| #define | BUSRDTORD(n) ((n) << 0) |

| #define | MSCH_MAINDDR3(ch, n) |

| #define | PCTL_LPDDR3_ODT_EN(ch, n) |

| #define | PCTL_BST_DISABLE(ch, n) |

| #define | PUBL_LPDDR3_EN(ch, n) |

| #define | DDR3_DLL_ENABLE (0) |

| #define | DDR3_DLL_DISABLE (1) |

| #define | SYS_REG_ENC_ROW_3_4(n, ch) ((n) << (30 + (ch))) |

| #define | SYS_REG_DEC_ROW_3_4(n, ch) ((n >> (30 + ch)) & 0x1) |

| #define | SYS_REG_ENC_CHINFO(ch) (1 << (28 + (ch))) |

| #define | SYS_REG_ENC_DDRTYPE(n) ((n) << 13) |

| #define | SYS_REG_ENC_NUM_CH(n) (((n) - 1) << 12) |

| #define | SYS_REG_DEC_NUM_CH(n) (1 + ((n >> 12) & 0x1)) |

| #define | SYS_REG_ENC_RANK(n, ch) (((n) - 1) << (11 + ((ch) * 16))) |

| #define | SYS_REG_DEC_RANK(n, ch) (1 + ((n >> (11 + 16 * ch)) & 0x1)) |

| #define | SYS_REG_ENC_COL(n, ch) (((n) - 9) << (9 + ((ch) * 16))) |

| #define | SYS_REG_DEC_COL(n, ch) (9 + ((n >> (9 + 16 * ch)) & 0x3)) |

| #define | SYS_REG_ENC_BK(n, ch) |

| #define | SYS_REG_DEC_BK(n, ch) (3 - ((n >> (8 + 16 * ch)) & 0x1)) |

| #define | SYS_REG_ENC_CS0_ROW(n, ch) (((n) - 13) << (6 + ((ch) * 16))) |

| #define | SYS_REG_DEC_CS0_ROW(n, ch) (13 + ((n >> (6 + 16 * ch)) & 0x3)) |

| #define | SYS_REG_ENC_CS1_ROW(n, ch) (((n) - 13) << (4 + ((ch) * 16))) |

| #define | SYS_REG_DEC_CS1_ROW(n, ch) (13 + ((n >> (4 + 16 * ch)) & 0x3)) |

| #define | SYS_REG_ENC_BW(n, ch) ((2 >> (n)) << (2 + ((ch) * 16))) |

| #define | SYS_REG_DEC_BW(n, ch) (2 >> ((n >> (2 + 16 * ch)) & 0x3)) |

| #define | SYS_REG_ENC_DBW(n, ch) ((2 >> (n)) << (0 + ((ch) * 16))) |

| #define | SYS_REG_DEC_DBW(n, ch) (2 >> ((n >> (0 + 16 * ch)) & 0x3)) |

Variables | |

| static struct rk3288_ddr_pctl_regs *const | rk3288_ddr_pctl [2] |

| static struct rk3288_ddr_publ_regs *const | rk3288_ddr_publ [2] |

| static struct rk3288_msch_regs *const | rk3288_msch [2] |

| #define MSCH_MAINDDR3 | ( | ch, | |

| n | |||

| ) |

| #define PCTL_BST_DISABLE | ( | ch, | |

| n | |||

| ) |

| #define PCTL_LPDDR3_ODT_EN | ( | ch, | |

| n | |||

| ) |

| #define PUBL_LPDDR3_EN | ( | ch, | |

| n | |||

| ) |

| #define SYS_REG_ENC_BK | ( | n, | |

| ch | |||

| ) |

| check_member | ( | rk3288_ddr_pctl_regs | , |

| iptr | , | ||

| 0x03fc | |||

| ) |

| check_member | ( | rk3288_ddr_publ_regs | , |

| datx8. | dxdqstr[3], | ||

| 0x0294 | |||

| ) |

| check_member | ( | rk3288_msch_regs | , |

| devtodev | , | ||

| 0x003c | |||

| ) |

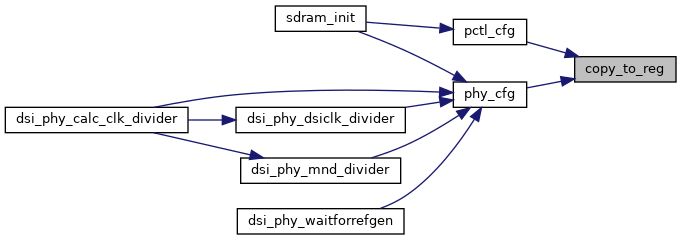

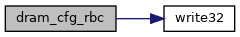

Definition at line 496 of file sdram.c.

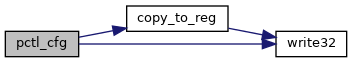

References write32().

Referenced by pctl_cfg(), and phy_cfg().

|

static |

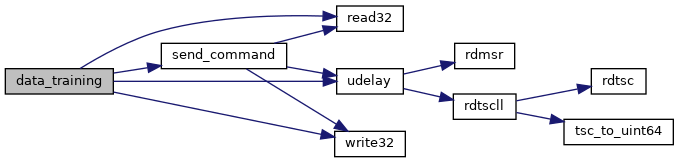

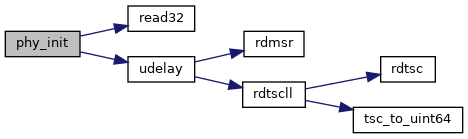

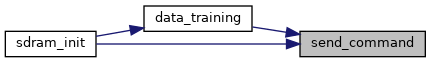

Definition at line 804 of file sdram.c.

References ARRAY_SIZE, clrbits32, rk3288_ddr_publ_regs::datx8, rk3288_ddr_publ_datx::dxgsr, LPDDR3, rk3288_ddr_publ_regs::pgcr, PGCR_DQSCFG, rk3288_ddr_publ_regs::pgsr, PGSR_DTERR, PGSR_RVEIRR, PGSR_RVERR, rk3288_ddr_publ_regs::pir, PIR_CLRSR, PIR_INIT, PIR_LOCKBYP, PIR_QSTRN, PIR_RVTRN, PIR_ZCALBYP, rk3288_ddr_pctl_regs::ppcfg, read32(), REF_CMD, rk3288_ddr_pctl, rk3288_ddr_publ, send_command(), setbits32, rk3288_ddr_pctl_regs::trefi, udelay(), and write32().

Referenced by sdram_init().

|

static |

Definition at line 554 of file sdram.c.

References DFI_DRAM_CLK_DPD_EN, DFI_DRAM_CLK_SR_EN, DFI_INIT_START, DFI_PARITY_EN, DFI_PARITY_INTR_EN, rk3288_ddr_pctl_regs::dfilpcfg0, rk3288_ddr_pctl_regs::dfiodtcfg, rk3288_ddr_pctl_regs::dfiodtcfg1, rk3288_ddr_pctl_regs::dfistcfg0, rk3288_ddr_pctl_regs::dfistcfg1, rk3288_ddr_pctl_regs::dfistcfg2, rk3288_ddr_pctl_regs::dfitctrldelay, rk3288_ddr_pctl_regs::dfitdramclkdis, rk3288_ddr_pctl_regs::dfitdramclken, rk3288_ddr_pctl_regs::dfitphyrdlat, rk3288_ddr_pctl_regs::dfitphyupdtype0, rk3288_ddr_pctl_regs::dfitphywrdata, rk3288_ddr_pctl_regs::dfiupdcfg, LP_PD_EN, LP_SR_EN, ODT_LEN_BL8_W, RANK0_ODT_WRITE_SEL, RANK1_ODT_WRITE_SEL, TCTRL_DELAY_TIME, TDRAM_CLK_DIS_TIME, TDRAM_CLK_EN_TIME, TLP_RESP_TIME, TPHY_RDLAT_TIME, TPHY_WRDATA_TIME, and write32().

Referenced by sdram_init().

|

static |

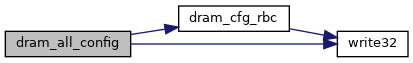

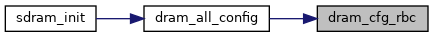

Definition at line 926 of file sdram.c.

References dram_cfg_rbc(), info, rk3288_pmu, rk3288_sgrf, RK_CLRSETBITS, rk3288_sgrf_regs::soc_con2, rk3288_pmu_regs::sys_reg, SYS_REG_ENC_BK, SYS_REG_ENC_BW, SYS_REG_ENC_CHINFO, SYS_REG_ENC_COL, SYS_REG_ENC_CS0_ROW, SYS_REG_ENC_CS1_ROW, SYS_REG_ENC_DBW, SYS_REG_ENC_DDRTYPE, SYS_REG_ENC_NUM_CH, SYS_REG_ENC_RANK, SYS_REG_ENC_ROW_3_4, and write32().

Referenced by sdram_init().

|

static |

Definition at line 912 of file sdram.c.

References clrbits32, clrsetbits32, rk3288_ddr_publ_regs::dcr, rk3288_msch_regs::ddrconf, PDQ_CFG, PDQ_MSK, rk3288_ddr_publ, rk3288_msch, and write32().

Referenced by dram_all_config().

|

static |

Definition at line 710 of file sdram.c.

References DDR3, rk3288_ddr_publ_regs::pgsr, PGSR_DLDONE, PGSR_IDONE, rk3288_ddr_publ_regs::pir, PIR_CLRSR, PIR_DRAMINIT, PIR_DRAMRST, PIR_ICPC, PIR_INIT, PIR_LOCKBYP, PIR_ZCALBYP, read32(), setbits32, and udelay().

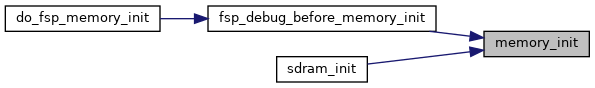

Referenced by fsp_debug_before_memory_init(), and sdram_init().

Definition at line 867 of file sdram.c.

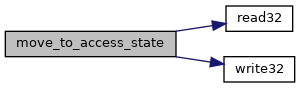

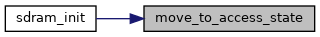

References __fallthrough, ACCESS, CFG_STATE, CONF, GO_STATE, INIT_MEM, LOW_POWER, LP_TRIG_VAL, PCTL_STAT_MSK, rk3288_ddr_publ_regs::pgsr, PGSR_DLDONE, read32(), rk3288_ddr_pctl, rk3288_ddr_publ, rk3288_ddr_pctl_regs::sctl, rk3288_ddr_pctl_regs::stat, WAKEUP_STATE, and write32().

Referenced by sdram_init().

|

static |

Definition at line 723 of file sdram.c.

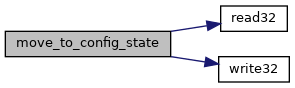

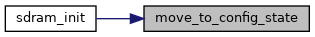

References __fallthrough, ACCESS, CFG_STATE, CONF, INIT_MEM, LOW_POWER, PCTL_STAT_MSK, rk3288_ddr_publ_regs::pgsr, PGSR_DLDONE, read32(), rk3288_ddr_pctl_regs::sctl, rk3288_ddr_pctl_regs::stat, WAKEUP_STATE, and write32().

Referenced by sdram_init().

|

static |

Definition at line 579 of file sdram.c.

References BURSTLENGTH_CFG, copy_to_reg(), DDR2_DDR3_BL_8, DDR3, DDR3_DLL_DISABLE, DDR3_EN, rk3288_ddr_pctl_regs::dfitphywrlat, rk3288_ddr_pctl_regs::dfitrddataen, LPDDR2_EN, LPDDR2_S4, LPDDR3, rk3288_ddr_pctl_regs::mcfg, MDDR_LPDDR2_CLK_STOP_IDLE, MSCH_MAINDDR3, PCTL_BST_DISABLE, PCTL_LPDDR3_ODT_EN, PD_EXIT_FAST, PD_EXIT_SLOW, PD_IDLE, PD_TYPE, PUBL_LPDDR3_EN, rk3288_ddr_pctl, rk3288_grf, rk3288_ddr_pctl_regs::scfg, setbits32, rk3288_grf_regs::soc_con0, rk3288_grf_regs::soc_con2, TFAW_CFG, rk3288_ddr_pctl_regs::togcnt1u, and write32().

Referenced by sdram_init().

|

static |

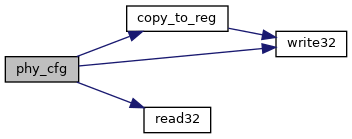

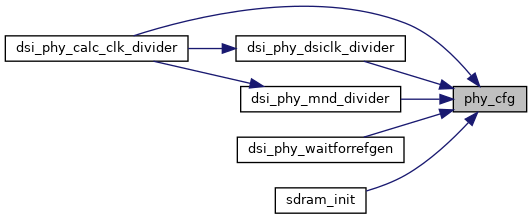

Definition at line 630 of file sdram.c.

References rk3288_msch_regs::activate, BUSRDTORD, BUSRDTOWR, BUSWRTORD, clrbits32, clrsetbits32, copy_to_reg(), rk3288_ddr_publ_regs::datx8, rk3288_ddr_publ_regs::dcr, DDR3, DDRMD_CFG, DDRMD_DDR3, DDRMD_LPDDR2_LPDDR3, DDRMD_MSK, rk3288_msch_regs::ddrtiming, rk3288_msch_regs::devtodev, DIV_ROUND_UP, DQRTT, DQSGE_CFG, DQSGE_MSK, DQSGX_CFG, DQSGX_MSK, DQSNRES_CFG, DQSNRES_MSK, DQSRES_CFG, DQSRES_MSK, DQSRTT, rk3288_ddr_publ_regs::dsgcr, rk3288_ddr_publ_regs::dtpr, rk3288_ddr_publ_regs::dxccr, rk3288_ddr_publ_datx::dxgcr, LPDDR3, MHz, MIN, rk3288_ddr_publ_regs::pgcr, PGCR_DFTCMP, PGCR_DFTLMT, PGCR_DQSCFG, PGCR_ITMDMD, PRT_DINIT0, PRT_DINIT1, PRT_DINIT2, PRT_DINIT3, PRT_DLLLOCK, PRT_DLLSRST, PRT_ITMSRST, rk3288_ddr_publ_regs::ptr, read32(), rk3288_msch_regs::readlatency, rk3288_ddr_publ, rk3288_msch, setbits32, TDQSCK_VAL, TDQSCKMAX_VAL, and write32().

Referenced by dsi_phy_calc_clk_divider(), dsi_phy_dsiclk_divider(), dsi_phy_mnd_divider(), dsi_phy_waitforrefgen(), and sdram_init().

|

static |

Definition at line 528 of file sdram.c.

References rk3288_ddr_publ_regs::acdllcr, ACDLLCR_DLLDIS, clrbits32, rk3288_ddr_publ_regs::datx8, rk3288_ddr_publ_regs::dllgcr, rk3288_ddr_publ_datx::dxdllcr, DXDLLCR_DLLDIS, MHz, rk3288_ddr_publ_regs::pir, PIR_DLLBYP, SBIAS_BYPASS, and setbits32.

Referenced by sdram_init().

|

static |

Definition at line 690 of file sdram.c.

References rk3288_ddr_publ_regs::pgsr, PGSR_DLDONE, PGSR_IDONE, PGSR_ZCDONE, rk3288_ddr_publ_regs::pir, PIR_CLRSR, PIR_DLLLOCK, PIR_DLLSRST, PIR_INIT, PIR_ITMSRST, PIR_ZCAL, read32(), setbits32, and udelay().

Referenced by sdram_init().

|

static |

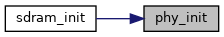

Definition at line 506 of file sdram.c.

References rk3288_ddr_publ_regs::acdllcr, ACDLLCR_DLLSRST, clrbits32, rk3288_ddr_publ_regs::datx8, rk3288_ddr_publ_datx::dxdllcr, DXDLLCR_DLLSRST, rkclk_ddr_reset(), setbits32, and udelay().

Referenced by sdram_init().

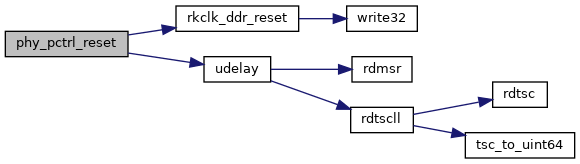

| void sdram_init | ( | const struct rk3288_sdram_params * | sdram_params | ) |

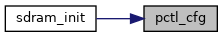

Definition at line 953 of file sdram.c.

References BIOS_INFO, clrsetbits32, data_training(), DDR3, DESELECT_CMD, dfi_cfg(), die(), dram_all_config(), LPDDR2_MA, LPDDR2_OP, LPDDR3, memory_init(), MHz, move_to_access_state(), move_to_config_state(), MRR_CMD, rk3288_ddr_pctl_regs::mrrcfg0, rk3288_ddr_pctl_regs::mrrstat0, MRS_CMD, pctl_cfg(), PD_ONDIE, PD_OUTPUT, rk3288_ddr_publ_regs::pgcr, phy_cfg(), phy_dll_bypass_set(), phy_init(), phy_pctrl_reset(), rk3288_ddr_pctl_regs::powctl, POWER_UP_DONE, POWER_UP_START, rk3288_ddr_pctl_regs::powstat, PREA_CMD, printk, PU_ONDIE, PU_OUTPUT, read32(), rk3288_ddr_pctl, rk3288_ddr_publ, rkclk_configure_ddr(), rkclk_ddr_phy_ctl_reset(), send_command(), set_bandwidth_ratio(), udelay(), write32(), ZDEN, rk3288_ddr_publ_regs::zq0cr, and rk3288_ddr_publ_regs::zq1cr.

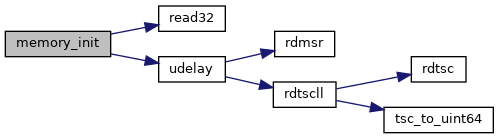

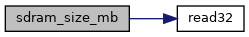

Definition at line 1069 of file sdram.c.

References ch, MiB, MIN, read32(), rk3288_pmu, rk3288_pmu_regs::sys_reg, SYS_REG_DEC_BK, SYS_REG_DEC_BW, SYS_REG_DEC_COL, SYS_REG_DEC_CS0_ROW, SYS_REG_DEC_CS1_ROW, SYS_REG_DEC_NUM_CH, SYS_REG_DEC_RANK, and SYS_REG_DEC_ROW_3_4.

|

static |

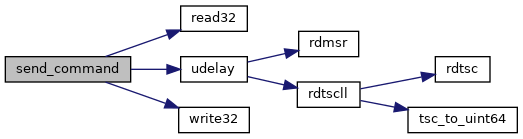

Definition at line 701 of file sdram.c.

References arg, rk3288_ddr_pctl_regs::mcmd, read32(), START_CMD, udelay(), and write32().

Referenced by data_training(), and sdram_init().

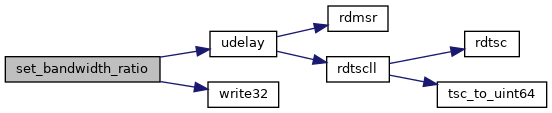

Definition at line 758 of file sdram.c.

References clrbits32, rk3288_ddr_publ_regs::datx8, rk3288_msch_regs::ddrtiming, rk3288_ddr_pctl_regs::dfistcfg0, rk3288_ddr_publ_datx::dxdllcr, DXDLLCR_DLLDIS, DXDLLCR_DLLSRST, rk3288_ddr_publ_datx::dxgcr, rk3288_ddr_pctl_regs::ppcfg, rk3288_ddr_pctl, rk3288_ddr_publ, rk3288_grf, rk3288_msch, RK_CLRBITS, RK_SETBITS, setbits32, rk3288_grf_regs::soc_con0, udelay(), and write32().

Referenced by sdram_init().

|

static |

Definition at line 223 of file sdram.c.

Referenced by data_training(), move_to_access_state(), pctl_cfg(), sdram_init(), and set_bandwidth_ratio().

|

static |

Definition at line 225 of file sdram.c.

Referenced by data_training(), dram_cfg_rbc(), move_to_access_state(), phy_cfg(), sdram_init(), and set_bandwidth_ratio().

|

static |

Definition at line 227 of file sdram.c.

Referenced by dram_cfg_rbc(), phy_cfg(), and set_bandwidth_ratio().