|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

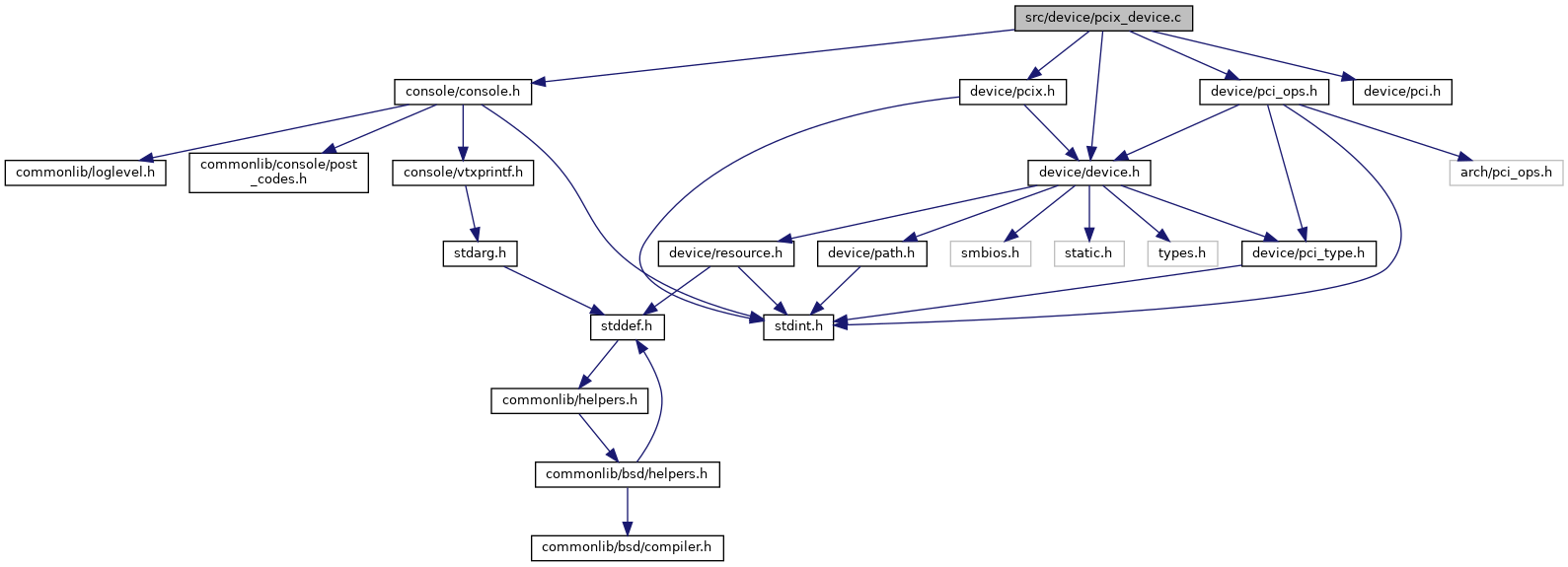

#include <console/console.h>#include <device/device.h>#include <device/pci.h>#include <device/pci_ops.h>#include <device/pcix.h>

Go to the source code of this file.

Functions | |

| static void | pcix_tune_dev (struct device *dev) |

| static void | pcix_tune_bus (struct bus *bus) |

| const char * | pcix_speed (u16 sstatus) |

| void | pcix_scan_bridge (struct device *dev) |

Variables | |

| static struct pci_operations | pcix_bus_ops_pci |

| Default device operations for PCI-X bridges. More... | |

| struct device_operations | default_pcix_ops_bus |

Definition at line 97 of file pcix_device.c.

| const char* pcix_speed | ( | u16 | sstatus | ) |

Definition at line 56 of file pcix_device.c.

References PCI_X_SSTATUS_CONVENTIONAL_PCI, PCI_X_SSTATUS_MFREQ, PCI_X_SSTATUS_MODE1_100MHZ, PCI_X_SSTATUS_MODE1_133MHZ, PCI_X_SSTATUS_MODE1_66MHZ, PCI_X_SSTATUS_MODE2_266MHZ_REF_100MHZ, PCI_X_SSTATUS_MODE2_266MHZ_REF_133MHZ, PCI_X_SSTATUS_MODE2_266MHZ_REF_66MHZ, PCI_X_SSTATUS_MODE2_533MHZ_REF_100MHZ, PCI_X_SSTATUS_MODE2_533MHZ_REF_133MHZ, and PCI_X_SSTATUS_MODE2_533MHZ_REF_66MHZ.

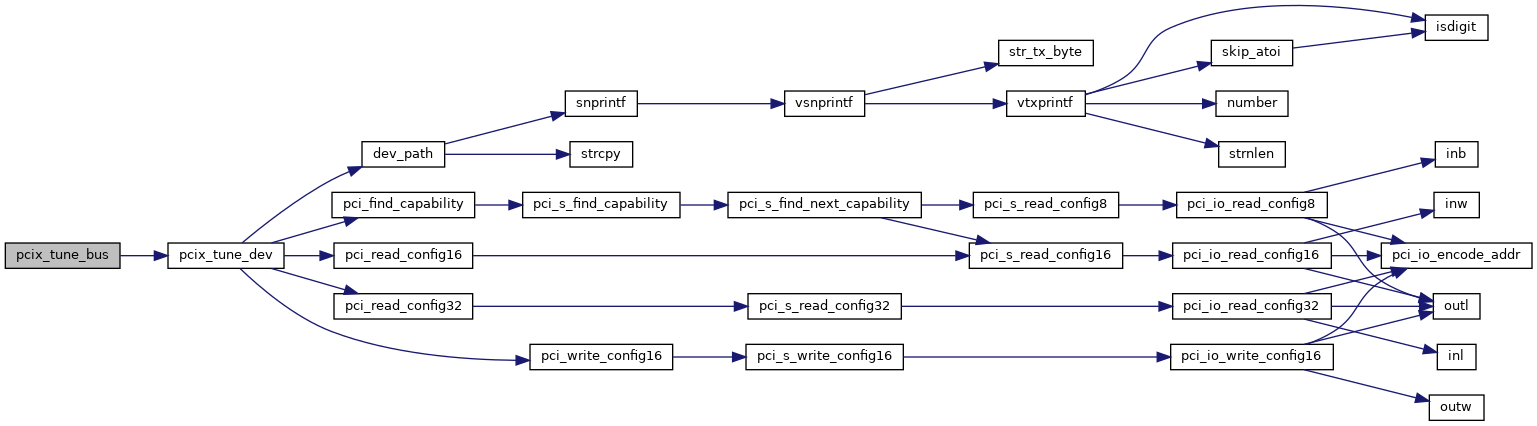

Definition at line 48 of file pcix_device.c.

References bus::children, pcix_tune_dev(), and device::sibling.

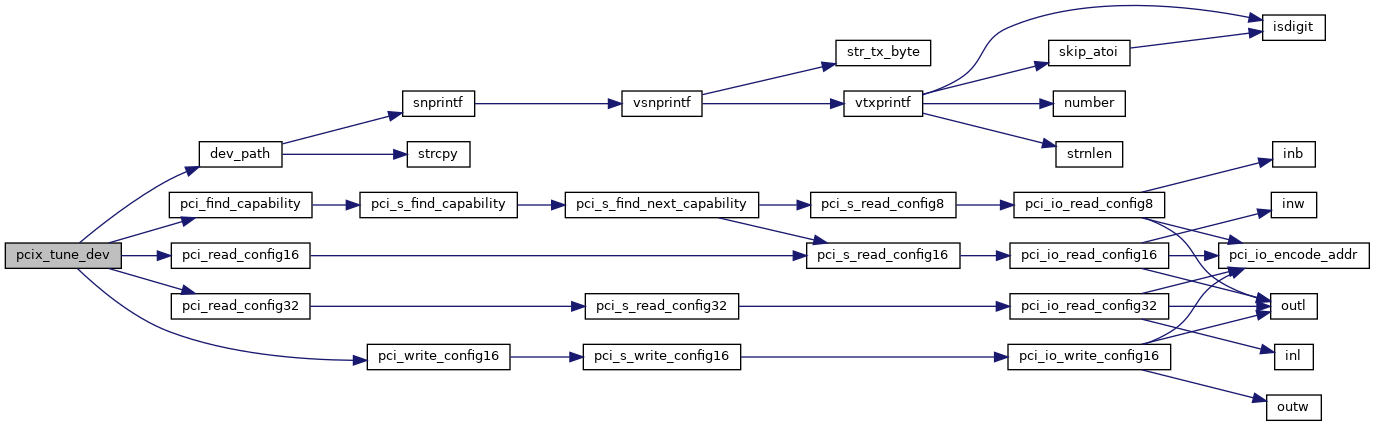

Definition at line 9 of file pcix_device.c.

References BIOS_DEBUG, dev_path(), device::hdr_type, PCI_CAP_ID_PCIX, pci_find_capability(), PCI_HEADER_TYPE_NORMAL, pci_read_config16(), pci_read_config32(), pci_write_config16(), PCI_X_CMD, PCI_X_CMD_DPERR_E, PCI_X_CMD_ERO, PCI_X_CMD_MAX_READ, PCI_X_CMD_MAX_SPLIT, PCI_X_STATUS, PCI_X_STATUS_MAX_READ, PCI_X_STATUS_MAX_SPLIT, and printk.

Referenced by pcix_tune_bus().

| struct device_operations default_pcix_ops_bus |

Definition at line 97 of file pcix_device.c.

Referenced by get_pci_bridge_ops().

|

static |

Default device operations for PCI-X bridges.

Definition at line 97 of file pcix_device.c.