|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

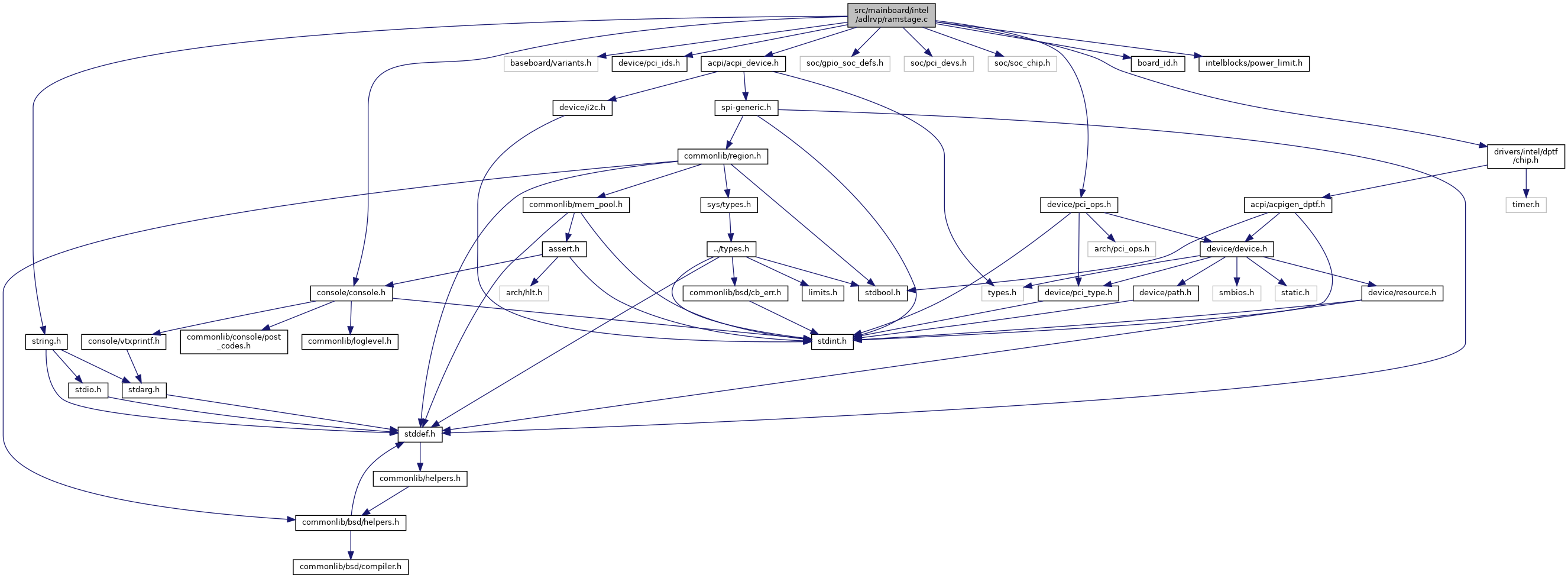

#include <acpi/acpi_device.h>#include <baseboard/variants.h>#include <console/console.h>#include <device/pci_ids.h>#include <device/pci_ops.h>#include <soc/gpio_soc_defs.h>#include <soc/pci_devs.h>#include <soc/soc_chip.h>#include <string.h>#include <drivers/intel/dptf/chip.h>#include "board_id.h"#include <intelblocks/power_limit.h>

Go to the source code of this file.

Data Structures | |

| struct | board_id_iom_port_config |

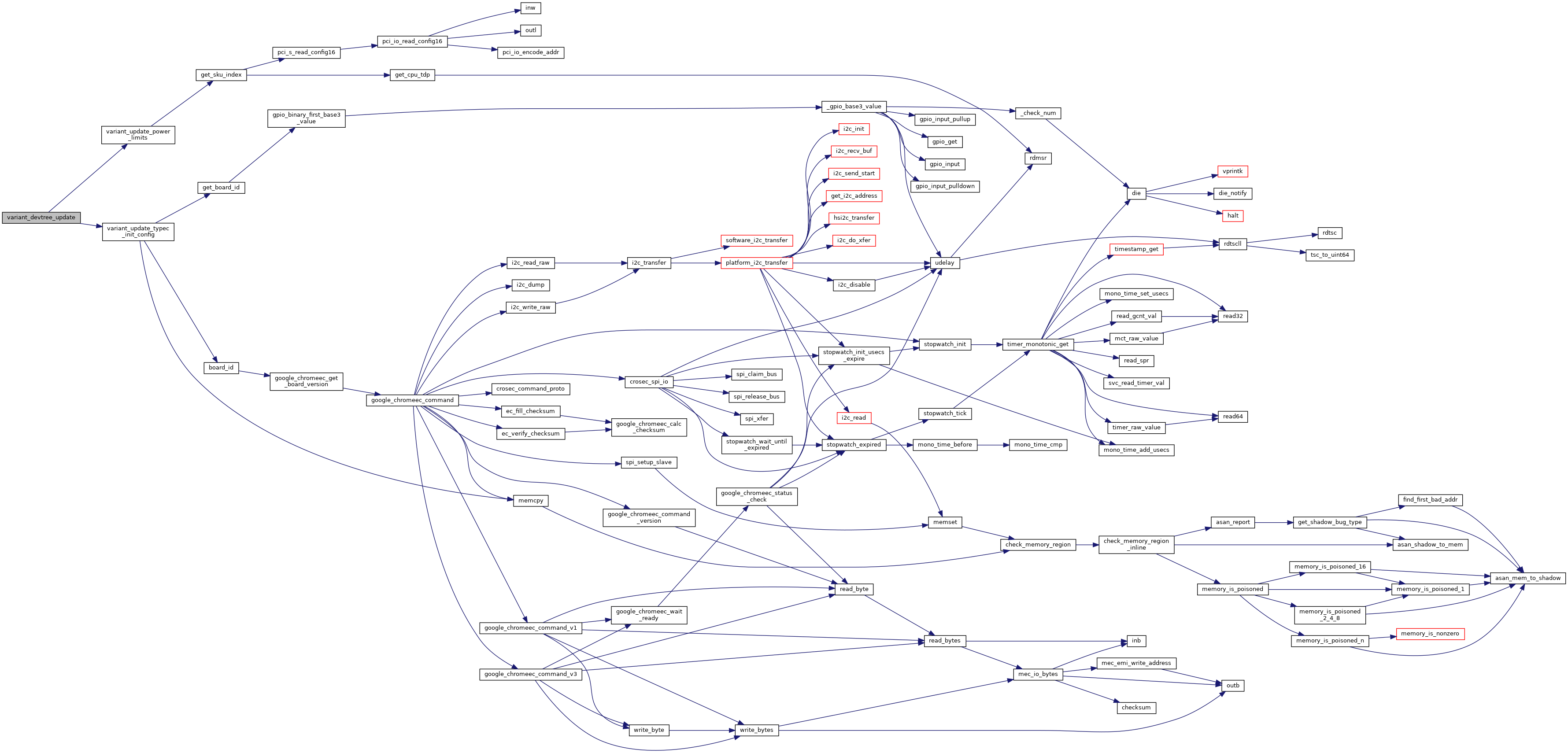

Functions | |

| WEAK_DEV_PTR (dptf_policy) | |

| void | variant_update_power_limits (void) |

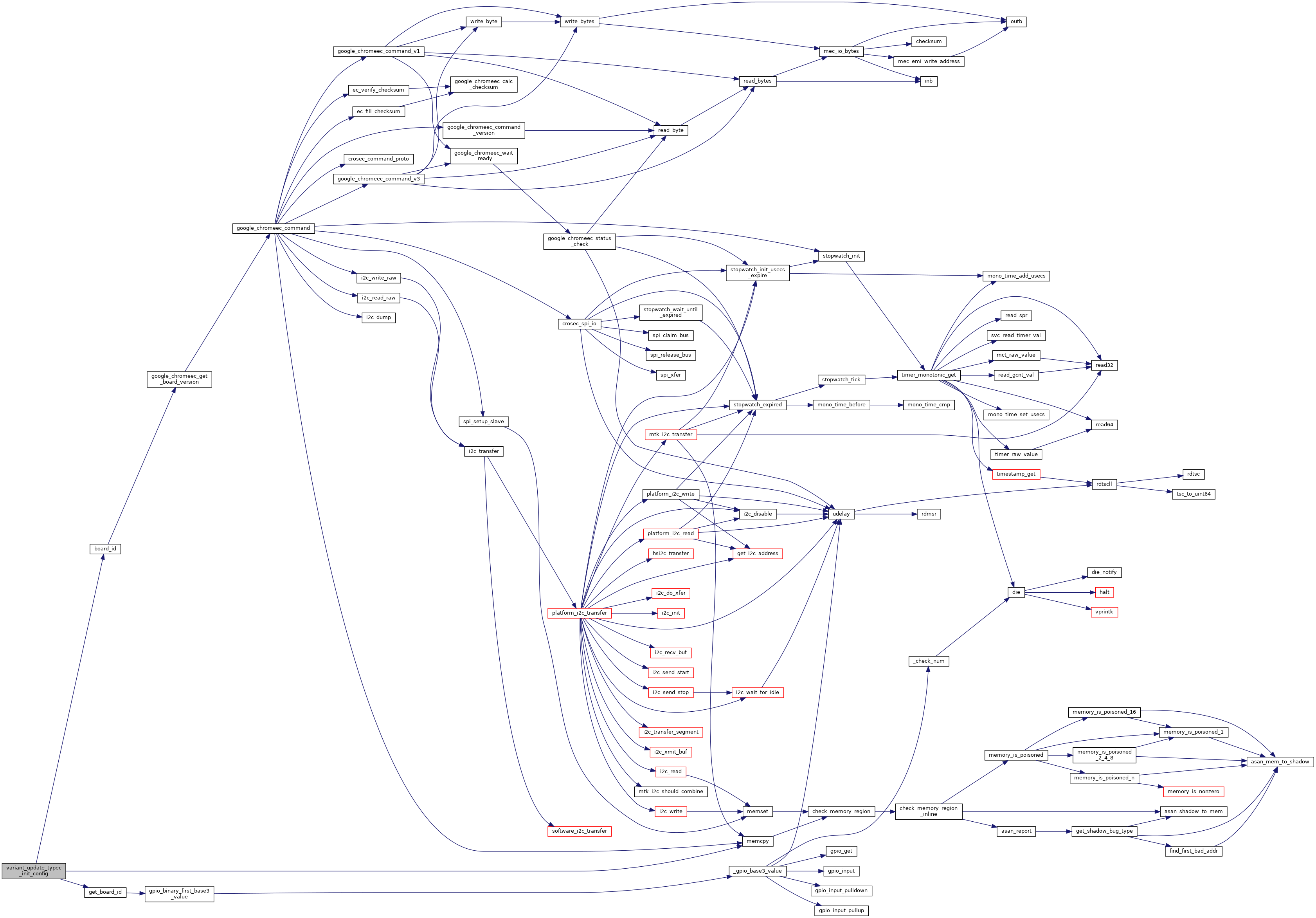

| static void | variant_update_typec_init_config (void) |

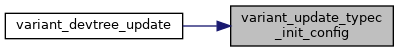

| void | variant_devtree_update (void) |

Variables | |

| const struct cpu_power_limits | limits [] |

| static const struct typec_aux_bias_pads | pad_config = { GPP_E23, GPP_E22 } |

| static const struct board_id_iom_port_config | port_config [] |

Definition at line 93 of file ramstage.c.

References variant_update_power_limits(), and variant_update_typec_init_config().

Definition at line 27 of file ramstage.c.

Definition at line 76 of file ramstage.c.

References ARRAY_SIZE, board_id(), config, CONFIG, config_of_soc, get_board_id(), memcpy(), board_id_iom_port_config::port, and port_config.

Referenced by variant_devtree_update().

| WEAK_DEV_PTR | ( | dptf_policy | ) |

| const struct cpu_power_limits limits[] |

Definition at line 1 of file ramstage.c.

|

static |

Definition at line 27 of file ramstage.c.

|

static |

Referenced by variant_update_typec_init_config().