|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

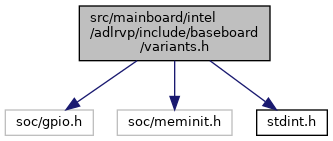

Go to the source code of this file.

Data Structures | |

| struct | cpu_power_limits |

Enumerations | |

| enum | adl_boardid { ADL_P_LP4_1 = 0x10 , ADL_P_LP4_2 = 0x11 , ADL_P_DDR5_1 = 0x12 , ADL_P_DDR5_2 = 0x16 , ADL_P_LP5_1 = 0x13 , ADL_P_LP5_2 = 0x17 , ADL_P_DDR4_1 = 0x14 , ADL_P_DDR4_2 = 0x3F , ADL_M_LP4 = 0x1 , ADL_M_LP5 = 0x2 , ADL_N_LP5 = 0x7 } |

Functions | |

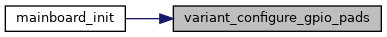

| void | variant_configure_gpio_pads (void) |

| void | variant_configure_early_gpio_pads (void) |

| size_t | variant_memory_sku (void) |

| const struct mb_cfg * | variant_memory_params (void) |

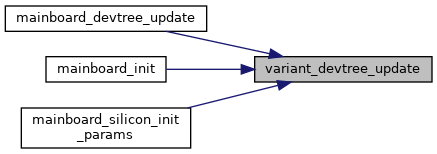

| void | variant_devtree_update (void) |

| void | variant_update_power_limits (void) |

| enum adl_boardid |

| Enumerator | |

|---|---|

| ADL_P_LP4_1 | |

| ADL_P_LP4_2 | |

| ADL_P_DDR5_1 | |

| ADL_P_DDR5_2 | |

| ADL_P_LP5_1 | |

| ADL_P_LP5_2 | |

| ADL_P_DDR4_1 | |

| ADL_P_DDR4_2 | |

| ADL_M_LP4 | |

| ADL_M_LP5 | |

| ADL_N_LP5 | |

Definition at line 10 of file variants.h.

Definition at line 117 of file early_gpio.c.

Definition at line 274 of file gpio.c.

Referenced by mainboard_init().

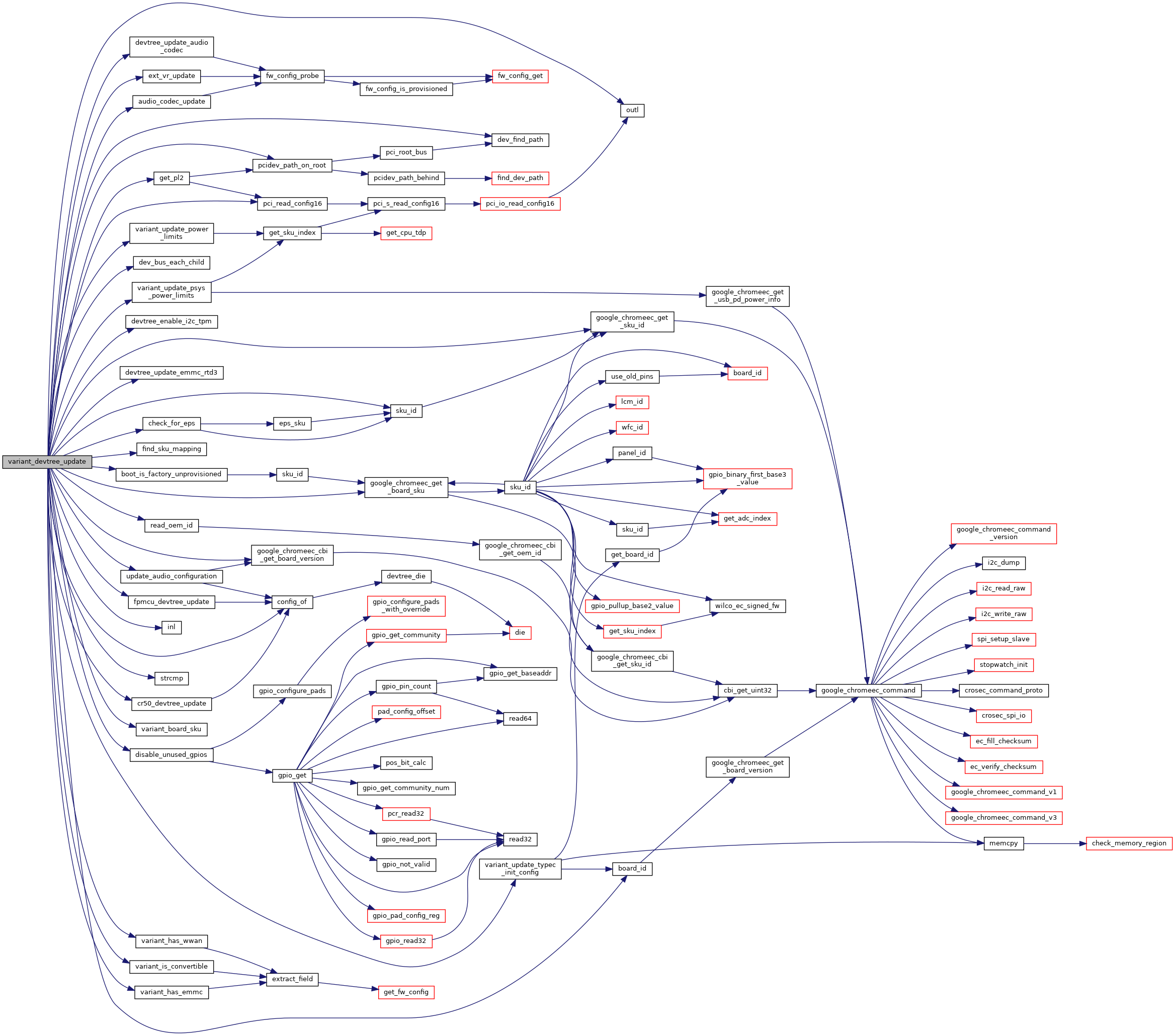

Definition at line 86 of file mainboard.c.

References __fallthrough, ABASE, soc_amd_picasso_config::acp_i2s_use_external_48mhz_osc, ACPI_GPIO_OUTPUT_ACTIVE_LOW, mmio_path::addr, APU_I2C0_BASE, ARRAY_SIZE, audio_codec_update(), B_PCH_OC_WDT_CTL_EN, B_PCH_OC_WDT_CTL_FORCE_ALL, B_PCH_OC_WDT_CTL_UNXP_RESET_STS, BIOS_INFO, board_id(), BOARD_ID_UNKNOWN, soc_amd_picasso_config::boostadj, boot_is_factory_unprovisioned(), check_for_eps(), config, CONFIG, config_of(), config_of_soc, cr50_devtree_update(), soc_amd_picasso_config::deemph_6db4, dev_bus_each_child(), dev_find_path(), DEV_PTR, DEVICE_PATH_I2C, DEVICE_PATH_MMIO, devtree_enable_i2c_tpm(), devtree_update_audio_codec(), devtree_update_emmc_rtd3(), disable_unused_gpios(), soc_amd_picasso_config::dp_vs_pemph_level, drivers_i2c_da7219_ops, drivers_i2c_generic_ops, soc_amd_picasso_config::edp_phy_override, soc_amd_picasso_config::edp_physel, soc_amd_picasso_config::edp_tuningset, soc_amd_picasso_config::emmc_config, ENABLE_EDP_TUNINGSET, device::enabled, ext_vr_update(), find_sku_mapping(), fpmcu_devtree_update(), get_pl2(), google_chromeec_cbi_get_board_version(), google_chromeec_get_board_sku(), google_chromeec_get_sku_id(), GPP_H0, inl(), limits, device::link_list, soc_amd_picasso_config::margin_deemph, device_path::mmio, NULL, OC0, OC1, OC2, outl(), device::path, PCH_DEV_GSPI1, PCH_DEV_PMC, PCH_DEVFN_EMMC, PCH_DEVFN_SATA, pci_read_config16(), pcidev_path_on_root(), PL2_ID_BARD_EKKO, PL2_ID_DEFAULT, PL2_ID_SONA_SYNDRA, printk, R_PCH_OC_WDT_CTL, read_oem_id(), RT58_I2C_ADDRESS, soc_amd_picasso_config::SD_EMMC_DISABLE, soc_amd_picasso_config::SD_EMMC_EMMC_HS200, sku, SKU_0_BARD, SKU_0_EKKO, SKU_0_NAUTILUS, SKU_0_PANTHEON, SKU_0_SONA, SKU_0_SYNDRA, SKU_0_VAYNE, SKU_1_BARD, SKU_1_EKKO, SKU_1_NAUTILUS_LTE, SKU_1_PANTHEON, SKU_1_SONA, SKU_1_SYNDRA, SKU_1_VAYNE, SKU_2_BARD, SKU_2_EKKO, SKU_2_PANTHEON, SKU_2_SYNDRA, SKU_2_VAYNE, SKU_3_BARD, SKU_3_EKKO, SKU_3_PANTHEON, SKU_3_SYNDRA, SKU_4_BARD, SKU_4_EKKO, SKU_4_PANTHEON, SKU_4_SYNDRA, SKU_5_BARD, SKU_5_EKKO, SKU_5_SYNDRA, SKU_6_BARD, SKU_6_EKKO, SKU_6_SYNDRA, SKU_7_BARD, SKU_7_EKKO, SKU_7_SYNDRA, SKU_BARLA_ALC5682_44, SKU_BARLA_ALC5682_45, SKU_BARLA_ALC5682_46, SKU_BARLA_ALC5682_47, sku_id(), sku_overwrite_mapping, SKU_TREEYA_ALC5682_AE, SKU_TREEYA_ALC5682_AF, strcmp(), sys_limits, soc_power_limits_config::tdp_pl2_override, soc_amd_picasso_config::timing, update_audio_configuration(), USB2_BIAS_0MV, USB2_BIAS_39MV, USB2_BIAS_56MV, USB2_HALF_BIT_PRE_EMP, USB2_PRE_EMP_ON, usb_oc_map_override, USB_PORT_COUNT, soc_amd_picasso_config::usb_port_overcurrent_pin, variant_board_sku(), variant_has_emmc(), variant_has_wwan(), variant_is_convertible(), variant_update_power_limits(), variant_update_psys_power_limits(), and variant_update_typec_init_config().

Referenced by mainboard_devtree_update(), mainboard_init(), and mainboard_silicon_init_params().

Definition at line 27 of file ramstage.c.