|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

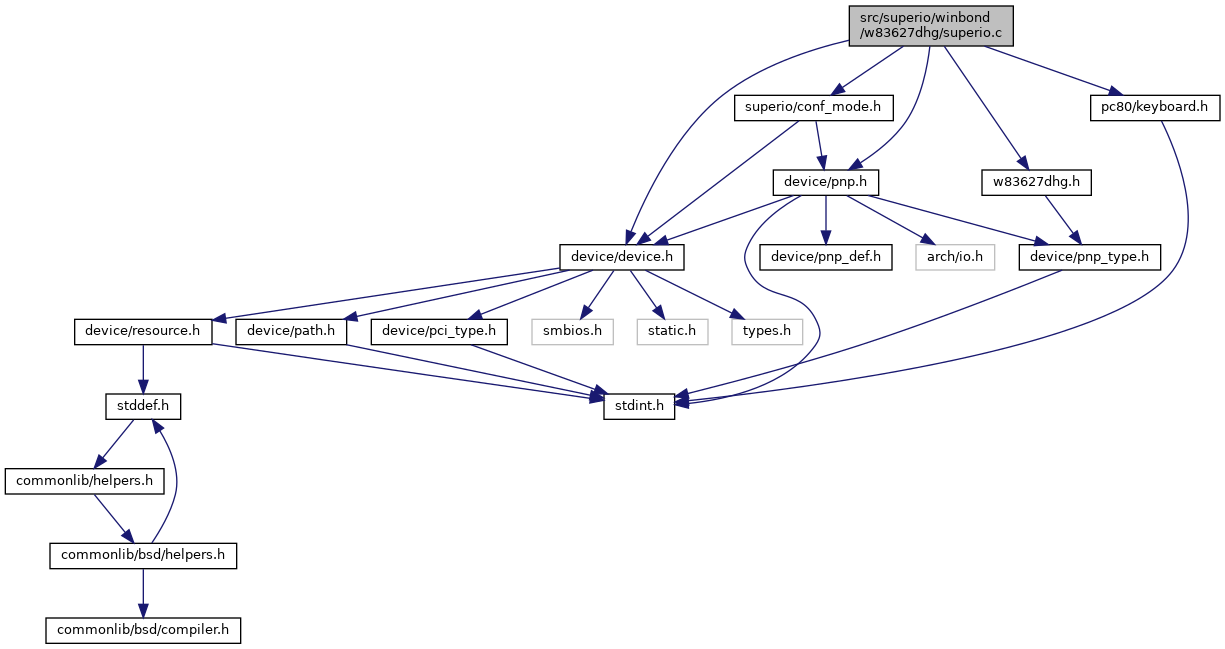

#include <device/device.h>#include <device/pnp.h>#include <superio/conf_mode.h>#include <pc80/keyboard.h>#include "w83627dhg.h"

Go to the source code of this file.

Functions | |

| static void | w83627dhg_enable_UR2 (struct device *dev) |

| static void | w83627dhg_init (struct device *dev) |

| static void | enable_dev (struct device *dev) |

Variables | |

| static struct device_operations | ops |

| static struct pnp_info | pnp_dev_info [] |

| struct chip_operations | superio_winbond_w83627dhg_ops |

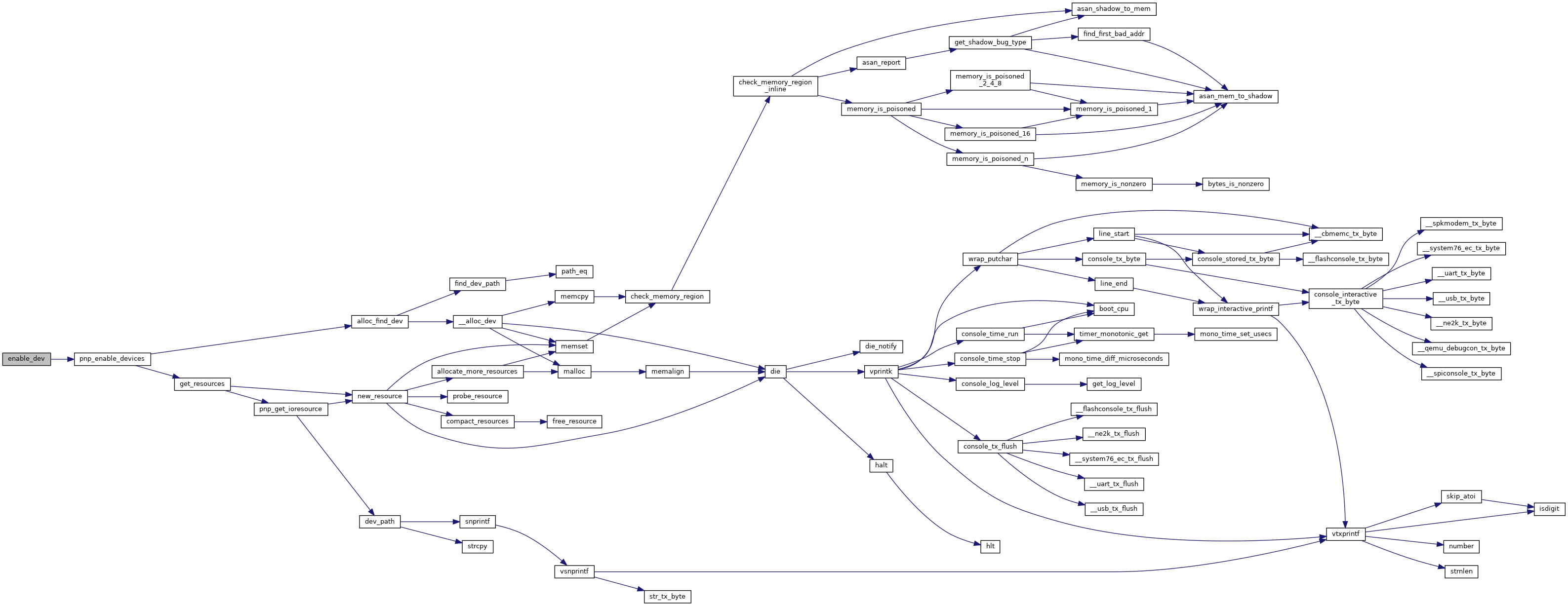

Definition at line 65 of file superio.c.

References ARRAY_SIZE, ops, pnp_dev_info, and pnp_enable_devices().

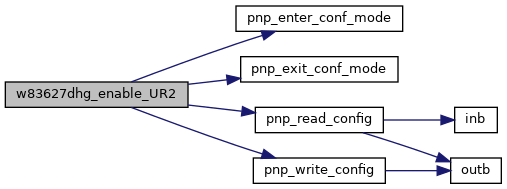

Definition at line 10 of file superio.c.

References pnp_enter_conf_mode(), pnp_exit_conf_mode(), pnp_read_config(), and pnp_write_config().

|

static |

Definition at line 21 of file superio.c.

Referenced by enable_dev().

|

static |

Definition at line 21 of file superio.c.

Referenced by enable_dev().

| struct chip_operations superio_winbond_w83627dhg_ops |