|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

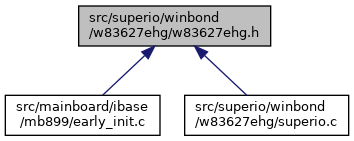

Go to the source code of this file.

Macros | |

| #define | W83627EHG_FDC 0 /* Floppy */ |

| #define | W83627EHG_PP 1 /* Parallel port */ |

| #define | W83627EHG_SP1 2 /* Com1 */ |

| #define | W83627EHG_SP2 3 /* Com2 */ |

| #define | W83627EHG_KBC 5 /* PS/2 keyboard & mouse */ |

| #define | W83627EHG_WDTO_PLED 8 /* Watchdog timer timeout, power LED */ |

| #define | W83627EHG_ACPI 10 /* ACPI */ |

| #define | W83627EHG_HWM 11 /* Hardware monitor */ |

| #define | W83627EHG_SFI_V 6 /* Serial flash interface (SFI) */ |

| #define | W83627EHG_GPIO_GAME_MIDI_V 7 /* GPIO1, GPIO6, game port, MIDI */ |

| #define | W83627EHG_GPIO_SUSLED_V 9 /* GPIO2, GPIO3, GPIO4, GPIO5, SUSLED */ |

| #define | W83627EHG_SFI ((1 << 8) | W83627EHG_SFI_V) |

| #define | W83627EHG_GPIO1 ((0 << 8) | W83627EHG_GPIO_GAME_MIDI_V) |

| #define | W83627EHG_GAME ((1 << 8) | W83627EHG_GPIO_GAME_MIDI_V) |

| #define | W83627EHG_MIDI ((2 << 8) | W83627EHG_GPIO_GAME_MIDI_V) |

| #define | W83627EHG_GPIO6 ((3 << 8) | W83627EHG_GPIO_GAME_MIDI_V) |

| #define | W83627EHG_GPIO2 ((0 << 8) | W83627EHG_GPIO_SUSLED_V) |

| #define | W83627EHG_GPIO3 ((1 << 8) | W83627EHG_GPIO_SUSLED_V) |

| #define | W83627EHG_GPIO4 ((2 << 8) | W83627EHG_GPIO_SUSLED_V) |

| #define | W83627EHG_GPIO5 ((3 << 8) | W83627EHG_GPIO_SUSLED_V) |

| #define W83627EHG_ACPI 10 /* ACPI */ |

Definition at line 12 of file w83627ehg.h.

| #define W83627EHG_FDC 0 /* Floppy */ |

Definition at line 6 of file w83627ehg.h.

| #define W83627EHG_GAME ((1 << 8) | W83627EHG_GPIO_GAME_MIDI_V) |

Definition at line 29 of file w83627ehg.h.

| #define W83627EHG_GPIO1 ((0 << 8) | W83627EHG_GPIO_GAME_MIDI_V) |

Definition at line 28 of file w83627ehg.h.

| #define W83627EHG_GPIO2 ((0 << 8) | W83627EHG_GPIO_SUSLED_V) |

Definition at line 33 of file w83627ehg.h.

| #define W83627EHG_GPIO3 ((1 << 8) | W83627EHG_GPIO_SUSLED_V) |

Definition at line 34 of file w83627ehg.h.

| #define W83627EHG_GPIO4 ((2 << 8) | W83627EHG_GPIO_SUSLED_V) |

Definition at line 35 of file w83627ehg.h.

| #define W83627EHG_GPIO5 ((3 << 8) | W83627EHG_GPIO_SUSLED_V) |

Definition at line 36 of file w83627ehg.h.

| #define W83627EHG_GPIO6 ((3 << 8) | W83627EHG_GPIO_GAME_MIDI_V) |

Definition at line 31 of file w83627ehg.h.

| #define W83627EHG_GPIO_GAME_MIDI_V 7 /* GPIO1, GPIO6, game port, MIDI */ |

Definition at line 17 of file w83627ehg.h.

| #define W83627EHG_GPIO_SUSLED_V 9 /* GPIO2, GPIO3, GPIO4, GPIO5, SUSLED */ |

Definition at line 18 of file w83627ehg.h.

| #define W83627EHG_HWM 11 /* Hardware monitor */ |

Definition at line 13 of file w83627ehg.h.

| #define W83627EHG_KBC 5 /* PS/2 keyboard & mouse */ |

Definition at line 10 of file w83627ehg.h.

| #define W83627EHG_MIDI ((2 << 8) | W83627EHG_GPIO_GAME_MIDI_V) |

Definition at line 30 of file w83627ehg.h.

| #define W83627EHG_PP 1 /* Parallel port */ |

Definition at line 7 of file w83627ehg.h.

| #define W83627EHG_SFI ((1 << 8) | W83627EHG_SFI_V) |

Definition at line 26 of file w83627ehg.h.

| #define W83627EHG_SFI_V 6 /* Serial flash interface (SFI) */ |

Definition at line 16 of file w83627ehg.h.

| #define W83627EHG_SP1 2 /* Com1 */ |

Definition at line 8 of file w83627ehg.h.

| #define W83627EHG_SP2 3 /* Com2 */ |

Definition at line 9 of file w83627ehg.h.

| #define W83627EHG_WDTO_PLED 8 /* Watchdog timer timeout, power LED */ |

Definition at line 11 of file w83627ehg.h.