|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

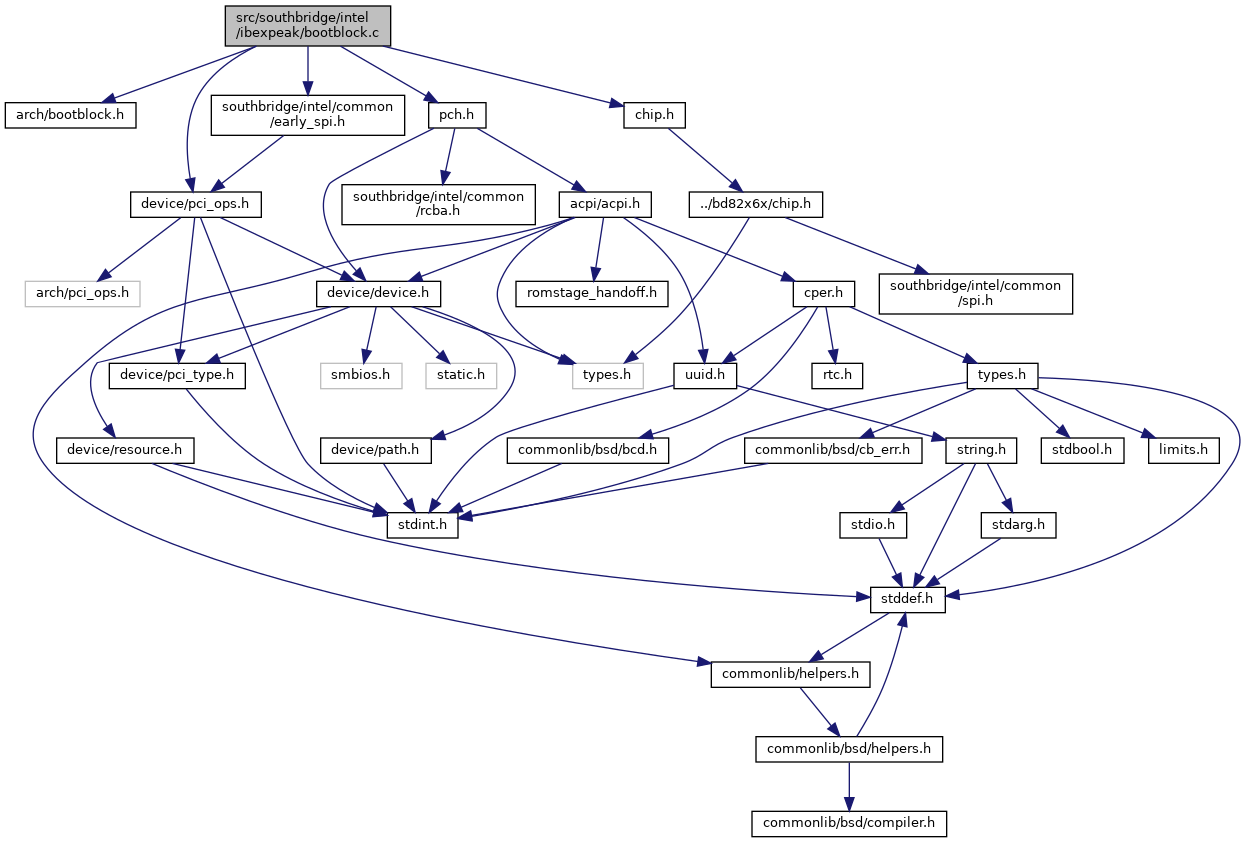

#include <arch/bootblock.h>#include <device/pci_ops.h>#include <southbridge/intel/common/early_spi.h>#include "pch.h"#include "chip.h"

Go to the source code of this file.

Functions | |

| static void | enable_port80_on_lpc (void) |

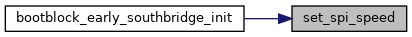

| static void | set_spi_speed (void) |

| static void | early_lpc_init (void) |

| void | bootblock_early_southbridge_init (void) |

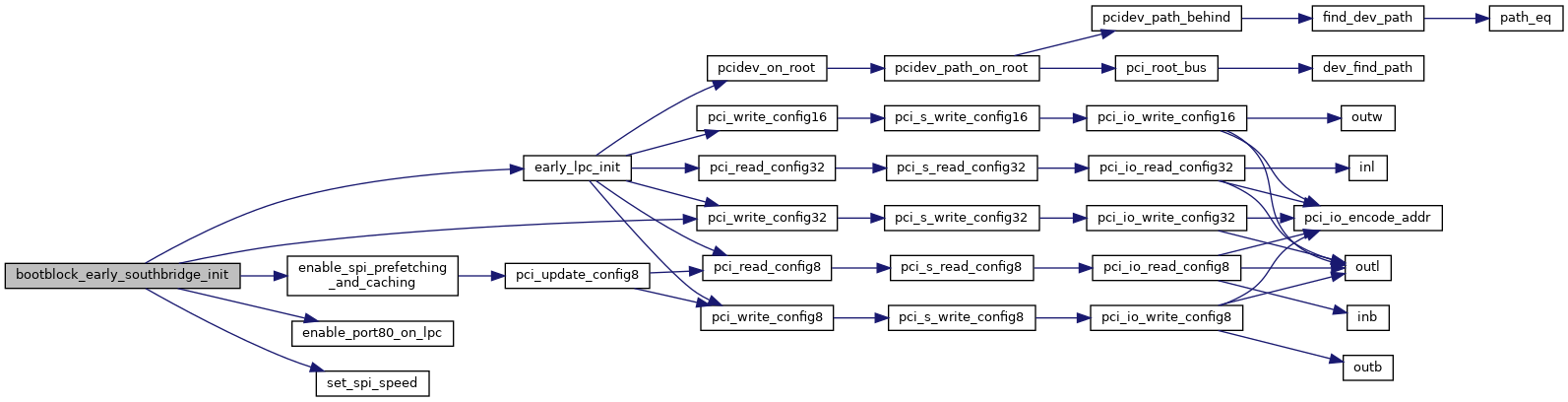

Definition at line 77 of file bootblock.c.

References early_lpc_init(), enable_port80_on_lpc(), enable_spi_prefetching_and_caching(), PCI_DEV, pci_write_config32(), RC, RCBA, RCBA32, and set_spi_speed().

Definition at line 34 of file bootblock.c.

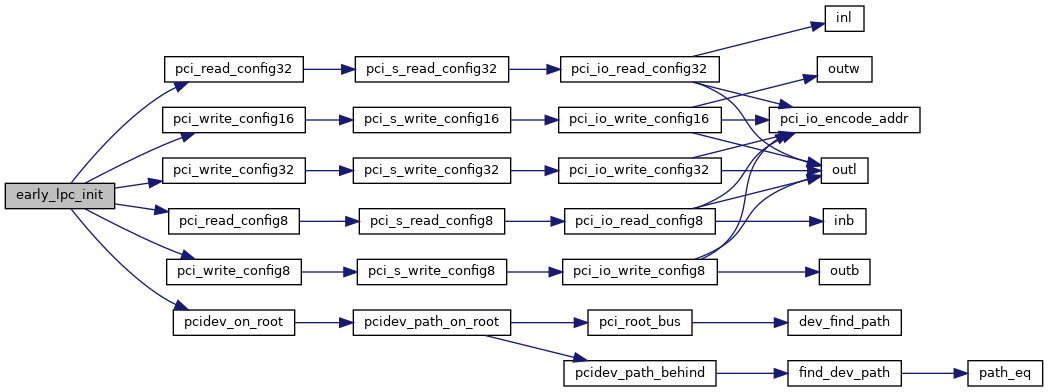

References device::chip_info, CNF1_LPC_EN, CNF2_LPC_EN, COMA_LPC_EN, COMB_LPC_EN, config, ETR3, ETR3_CF9GR, FDD_LPC_EN, GAMEH_LPC_EN, GAMEL_LPC_EN, GEN_PMCON_3, KBC_LPC_EN, LPC_EN, LPC_GEN1_DEC, LPC_GEN2_DEC, LPC_GEN3_DEC, LPC_GEN4_DEC, LPC_IO_DEC, LPT_LPC_EN, MC_LPC_EN, NULL, PCH_LPC_DEV, pci_read_config32(), pci_read_config8(), pci_write_config16(), pci_write_config32(), pci_write_config8(), and pcidev_on_root().

Referenced by bootblock_early_southbridge_init().

Definition at line 9 of file bootblock.c.

Referenced by bootblock_early_southbridge_init().

Definition at line 14 of file bootblock.c.

Referenced by bootblock_early_southbridge_init().