|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

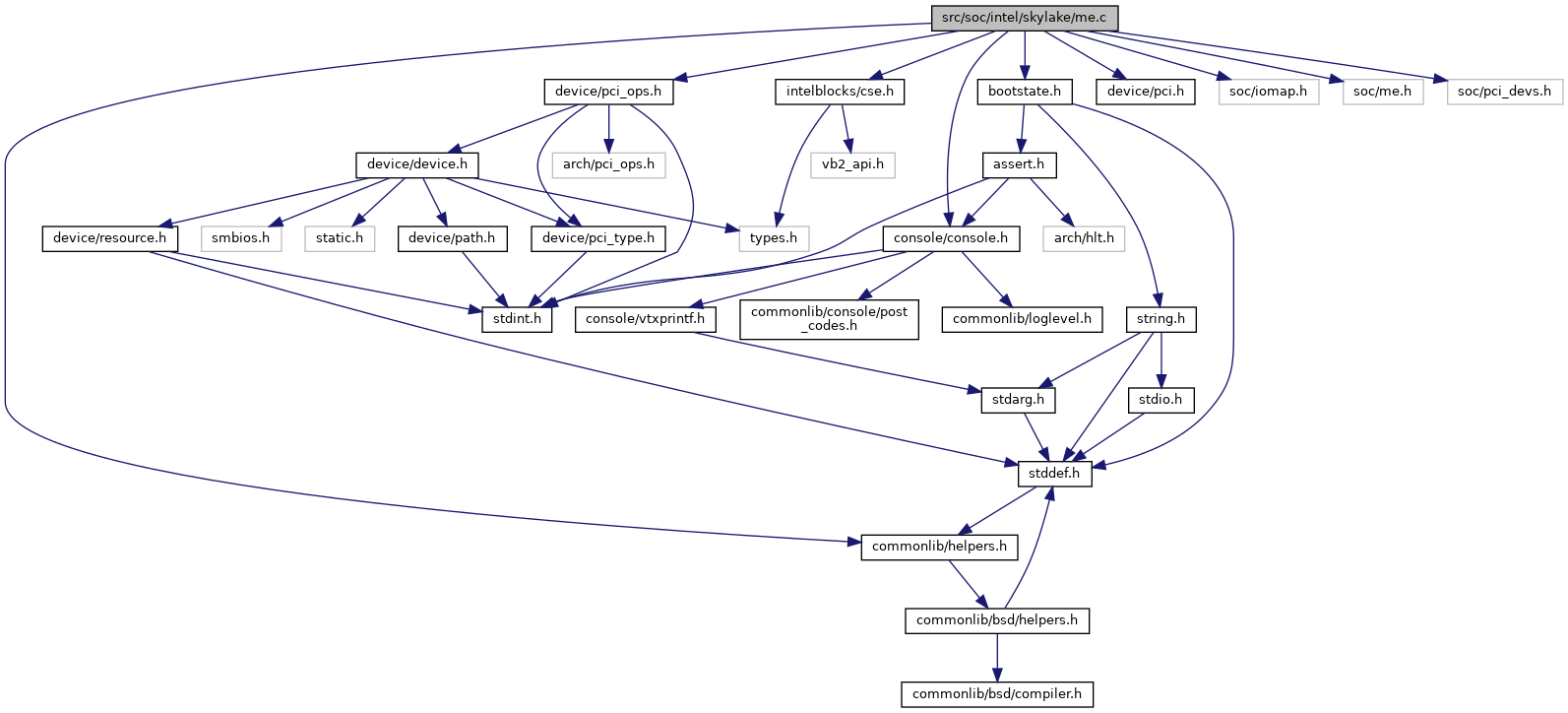

#include <device/pci_ops.h>#include <bootstate.h>#include <commonlib/helpers.h>#include <console/console.h>#include <device/pci.h>#include <intelblocks/cse.h>#include <soc/iomap.h>#include <soc/me.h>#include <soc/pci_devs.h>

Go to the source code of this file.

Functions | |

| void | intel_me_status (void) |

| int | send_global_reset (void) |

| BOOT_STATE_INIT_ENTRY (BS_DEV_ENABLE, BS_ON_EXIT, print_me_fw_version, NULL) | |

Variables | |

| static const char *const | me_cws_values [] |

| static const char *const | me_opstate_values [] |

| static const char *const | me_opmode_values [] |

| static const char *const | me_error_values [] |

| static const char *const | me_progress_values [] |

| static const char *const | me_pmevent_values [] |

| static const char *const | me_progress_rom_values [] |

| static const char *const | me_progress_bup_values [] |

| BOOT_STATE_INIT_ENTRY | ( | BS_DEV_ENABLE | , |

| BS_ON_EXIT | , | ||

| print_me_fw_version | , | ||

| NULL | |||

| ) |

Definition at line 184 of file me.c.

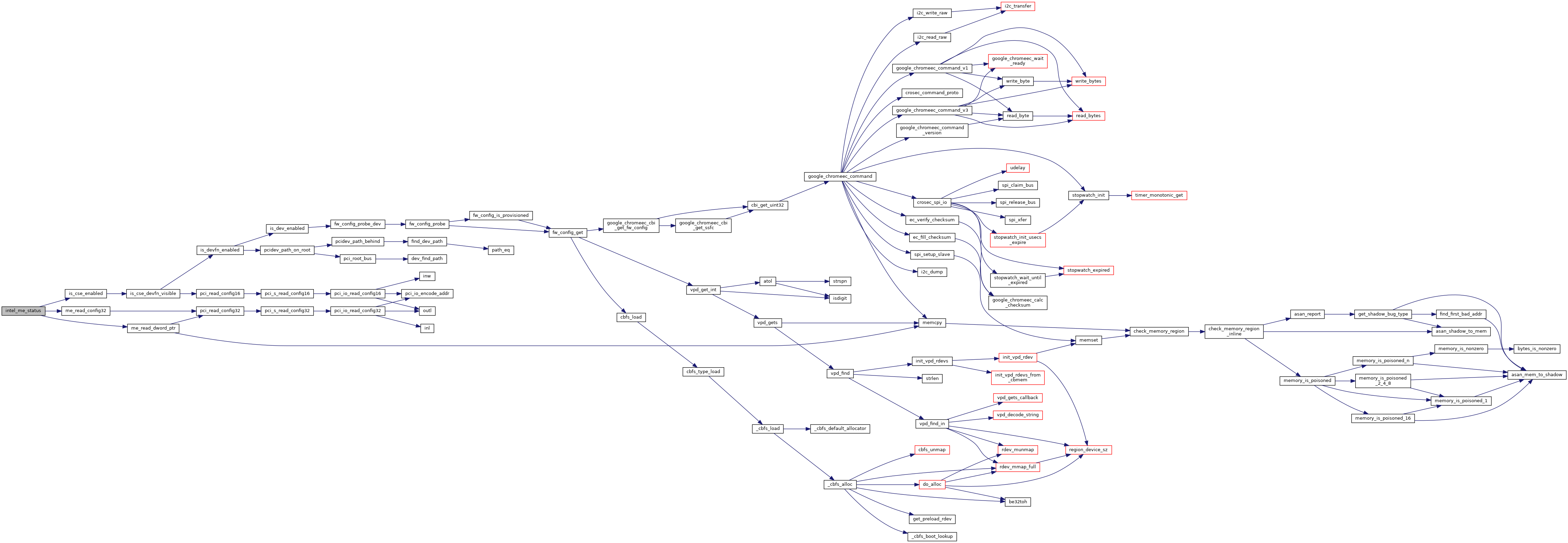

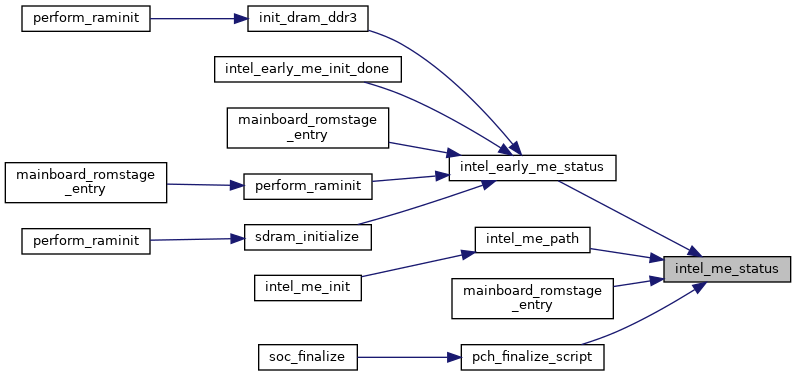

References ARRAY_SIZE, ARRAY_TO_ELEMENT, BIOS_DEBUG, BIOS_INFO, me_hfsts1::boot_options_present, me_hfs::boot_options_present, me_hfsts2::cpu_replaced_sts, me_hfsts2::cpu_replaced_valid, me_hfsts2::current_pmevent, me_hfs2::current_pmevent, me_hfs2::current_state, me_hfsts2::current_state, me_hfsts1::d0i3_support_valid, me_hfsts1::d3_support_valid, me_hfsts1::data, me_hfsts3::data, me_hfsts2::data, me_hfsts6::data, me_hfsts3::encrypt_key_check, me_hfsts3::encrypt_key_override, me_hfsts1::error_code, me_hfs::error_code, me_hfsts1::fields, me_hfsts3::fields, me_hfsts2::fields, me_hfsts6::fields, me_hfsts6::fpf_nvars, me_hfsts1::fpt_bad, me_hfs::fpt_bad, me_hfsts1::ft_bup_ld_flr, me_hfs::ft_bup_ld_flr, me_hfsts1::fw_init_complete, me_hfs::fw_init_complete, me_hfsts3::fw_sku, is_cse_enabled(), me_hfsts2::low_power_state, me_cws_values, me_error_values, ME_HFS2_PHASE_BUP, ME_HFS2_PHASE_HOST_COMM, ME_HFS2_PHASE_POLICY, ME_HFS2_PHASE_ROM, ME_HFS2_PHASE_UKERNEL, ME_HFS3_FW_SKU_CONSUMER, ME_HFS3_FW_SKU_CORPORATE, ME_HFS6_FPF_ERROR, ME_HFS6_FPF_NOT_COMMITTED, me_opmode_values, me_opstate_values, me_pmevent_values, me_progress_bup_values, me_progress_policy_values, me_progress_rom_values, me_progress_values, me_read_config32(), me_read_dword_ptr(), me_hfsts1::mfg_mode, me_hfs::mfg_mode, NULL, me_hfsts1::operation_mode, me_hfs::operation_mode, me_hfsts1::operation_state, me_hfs::operation_state, me_hfsts3::pch_config_change, PCI_ME_HFS, PCI_ME_HFS2, PCI_ME_HFSTS1, PCI_ME_HFSTS2, PCI_ME_HFSTS3, PCI_ME_HFSTS4, PCI_ME_HFSTS5, PCI_ME_HFSTS6, me_hfsts3::power_down_mitigation, printk, me_hfs2::progress_code, me_hfsts2::progress_code, me_hfsts1::update_in_progress, me_hfs::update_in_progress, me_hfsts1::working_state, and me_hfs::working_state.

Referenced by intel_early_me_status(), intel_me_path(), mainboard_romstage_entry(), and pch_finalize_script().

| int send_global_reset | ( | void | ) |

Definition at line 341 of file me.c.

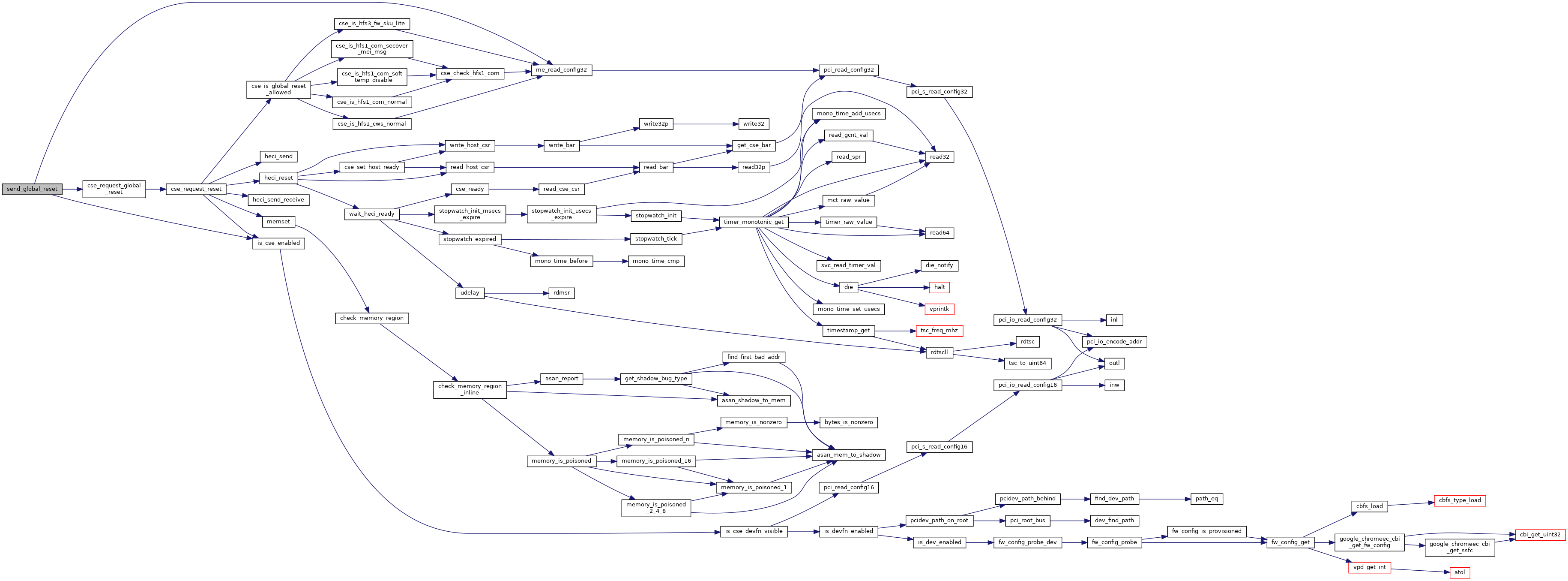

References cse_request_global_reset(), me_hfsts1::data, me_hfsts1::fields, is_cse_enabled(), me_read_config32(), me_hfsts1::operation_mode, and PCI_ME_HFSTS1.

Referenced by do_global_reset().

|

static |

Definition at line 14 of file me.c.

Referenced by intel_me_status().

|

static |

Definition at line 53 of file me.c.

Referenced by intel_me_status().

|

static |

Definition at line 44 of file me.c.

Referenced by intel_me_status().

|

static |

Definition at line 34 of file me.c.

Referenced by intel_me_status().

|

static |

Definition at line 74 of file me.c.

Referenced by intel_me_status().

|

static |

Definition at line 117 of file me.c.

Referenced by intel_me_status().

|

static |

Definition at line 111 of file me.c.

Referenced by intel_me_status().

|

static |

Definition at line 61 of file me.c.

Referenced by intel_me_status().