|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

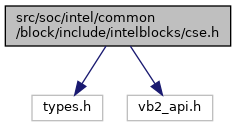

#include <types.h>#include <vb2_api.h>

Go to the source code of this file.

Data Structures | |

| struct | mkhi_hdr |

| struct | fw_version |

| struct | me_version |

| struct | me_fw_ver_resp |

| struct | cse_boot_perf_rsp |

Variables | |

| struct mkhi_hdr | __packed |

| anonymous enum |

| enum cse_boot_perf_data |

| enum cse_device_state |

| enum cse_tx_rx_status |

| enum csme_failure_reason |

| enum rst_req_type |

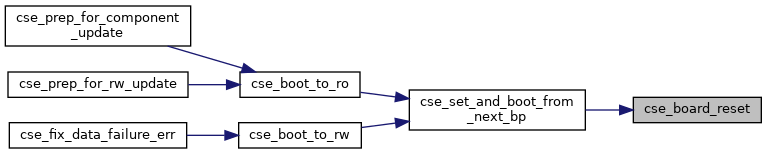

Definition at line 350 of file cse_lite.c.

Referenced by cse_set_and_boot_from_next_bp().

Definition at line 1023 of file cse.c.

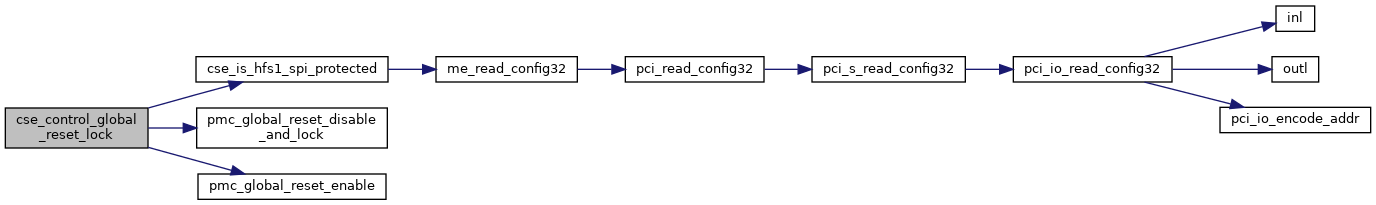

References CONFIG, cse_is_hfs1_spi_protected(), pmc_global_reset_disable_and_lock(), and pmc_global_reset_enable().

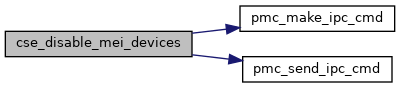

Definition at line 31 of file disable_heci.c.

References BIOS_ERR, CB_SUCCESS, PMC_IPC_MEI_DISABLE_ID, PMC_IPC_MEI_DISABLE_SUBID_DISABLE, pmc_make_ipc_cmd(), pmc_send_ipc_cmd(), and printk.

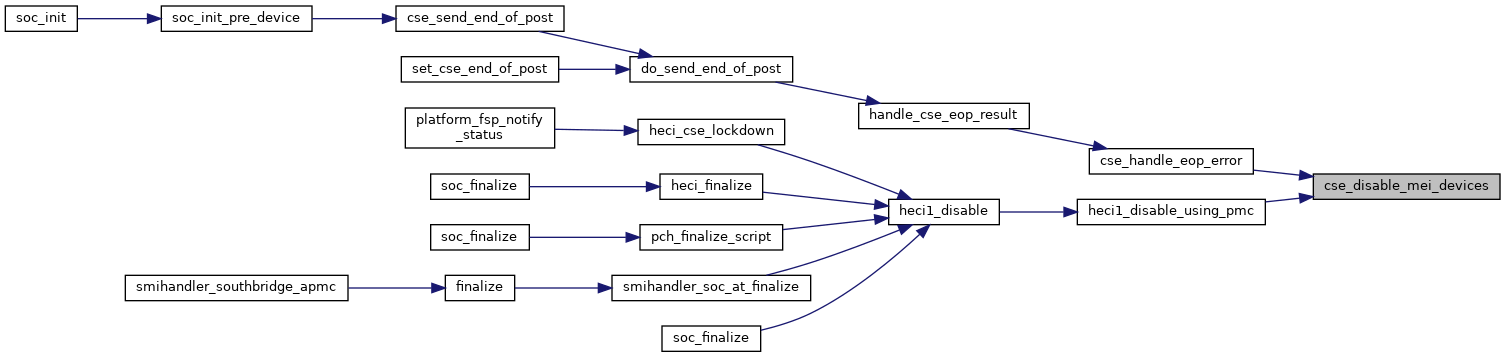

Referenced by cse_handle_eop_error(), and heci1_disable_using_pmc().

Definition at line 1042 of file cse_lite.c.

Referenced by mainboard_romstage_entry().

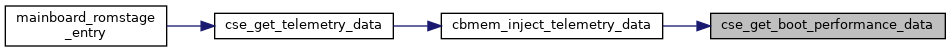

| bool cse_get_boot_performance_data | ( | struct cse_boot_perf_rsp * | boot_perf | ) |

Definition at line 133 of file cse_lite.c.

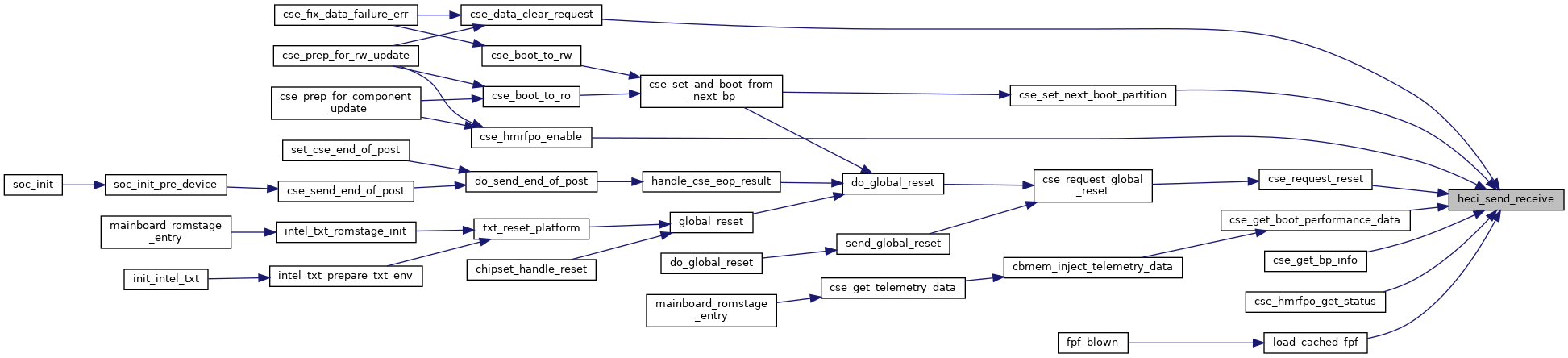

References __packed, BIOS_ERR, cse_boot_perf_rsp::hdr, HECI_MKHI_ADDR, heci_send_receive(), MKHI_BUP_COMMON_GET_BOOT_PERF_DATA, MKHI_GROUP_ID_BUP_COMMON, printk, and mkhi_hdr::result.

Referenced by cbmem_inject_telemetry_data().

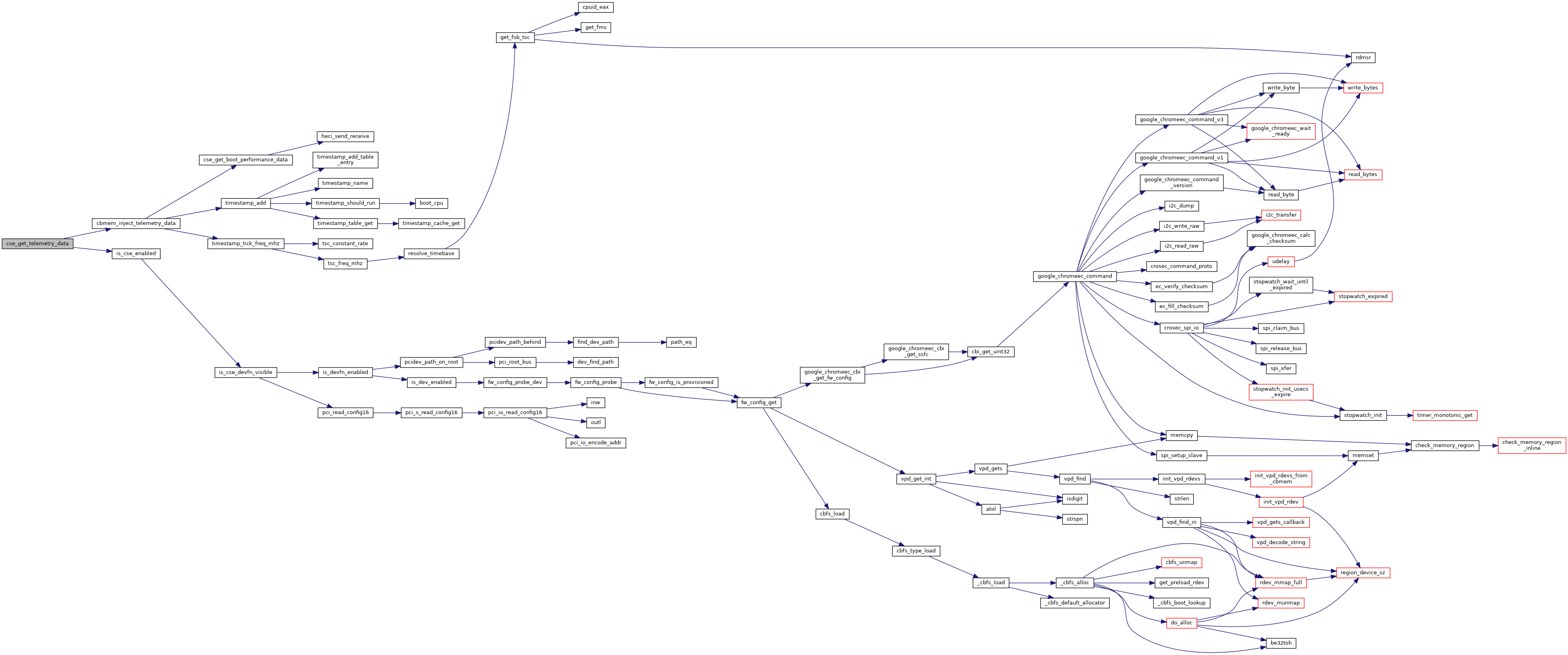

Definition at line 76 of file telemetry.c.

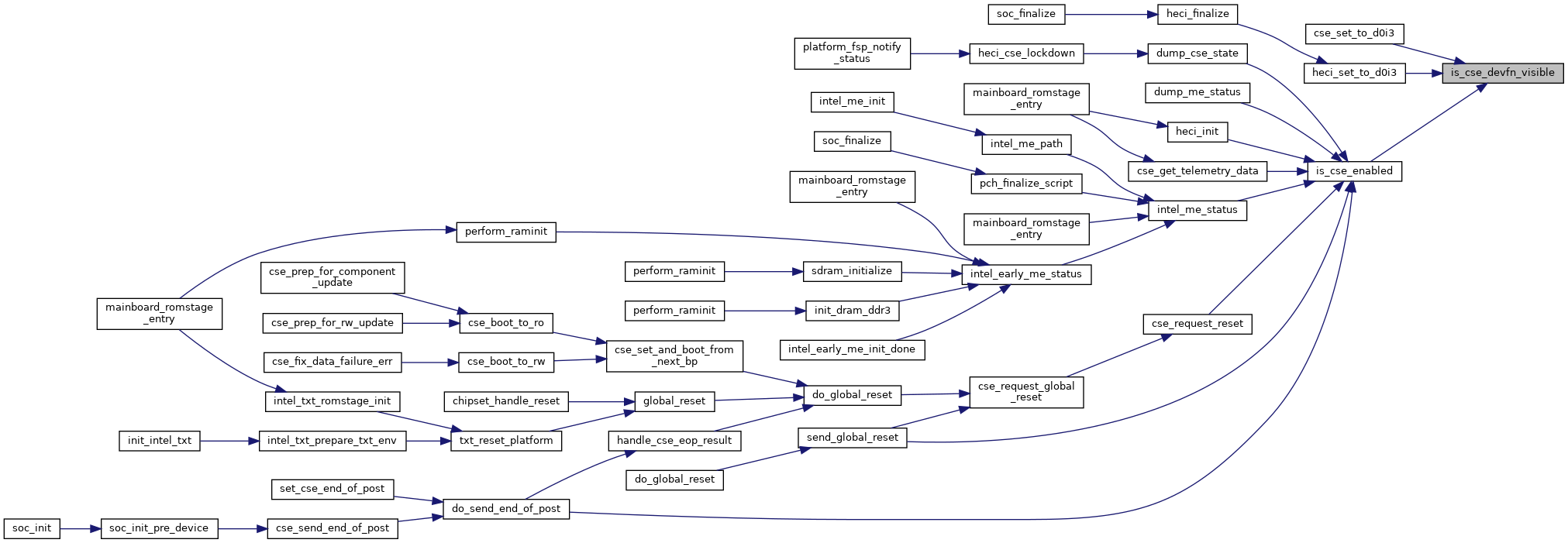

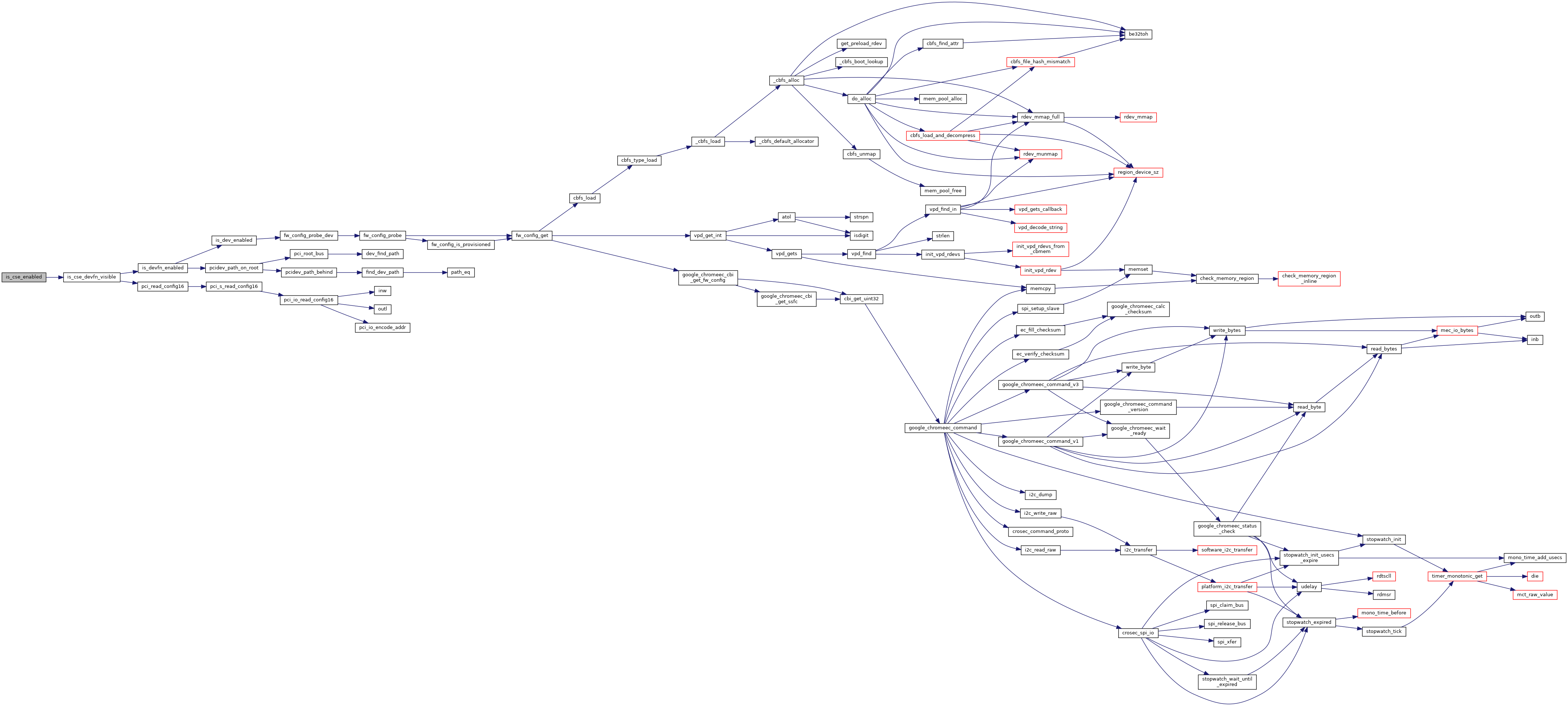

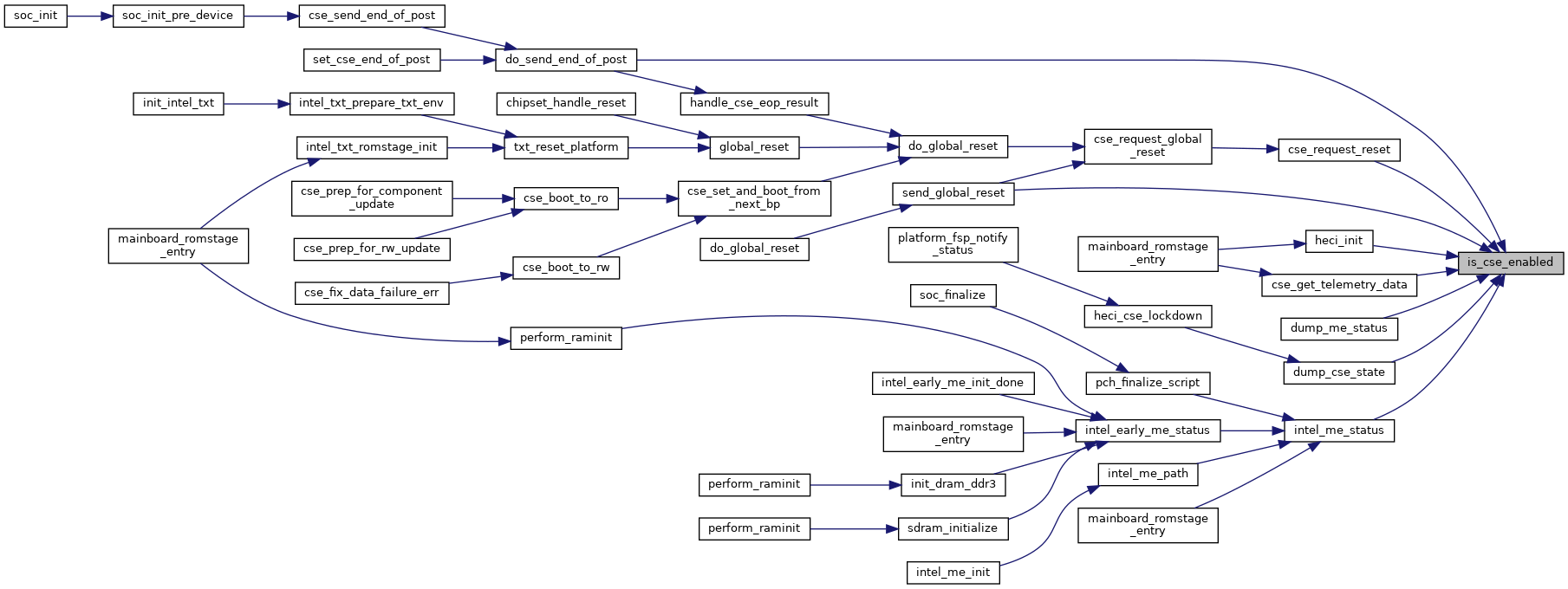

References BIOS_DEBUG, cbmem_inject_telemetry_data(), is_cse_enabled(), and printk.

Referenced by mainboard_romstage_entry().

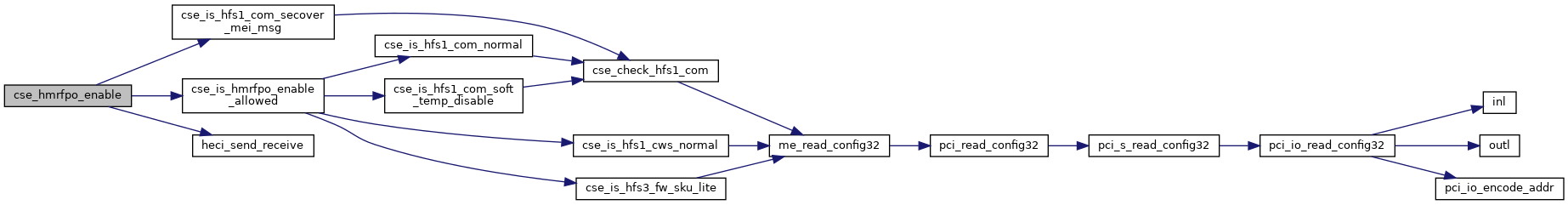

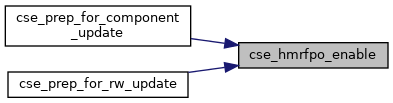

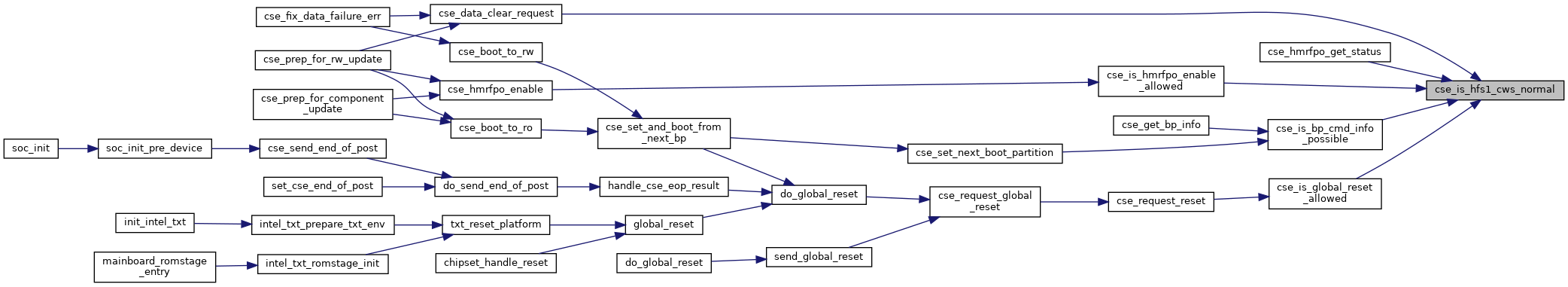

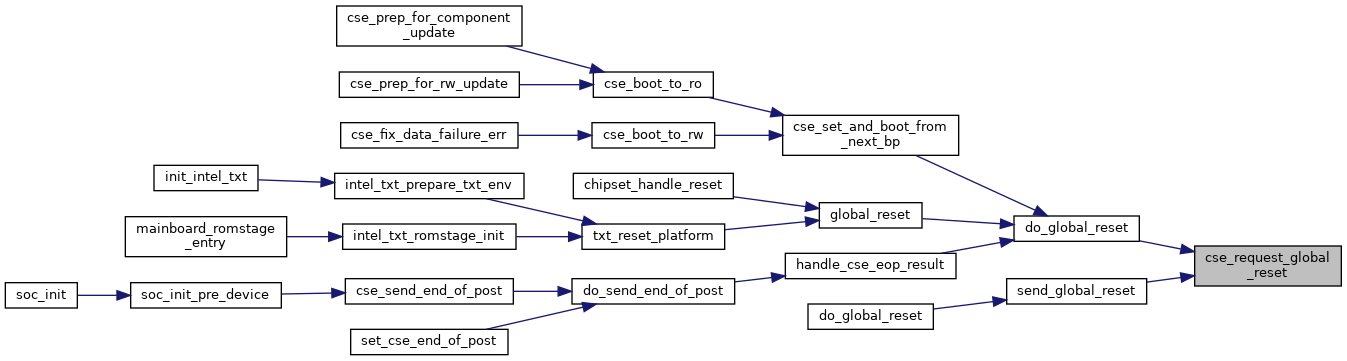

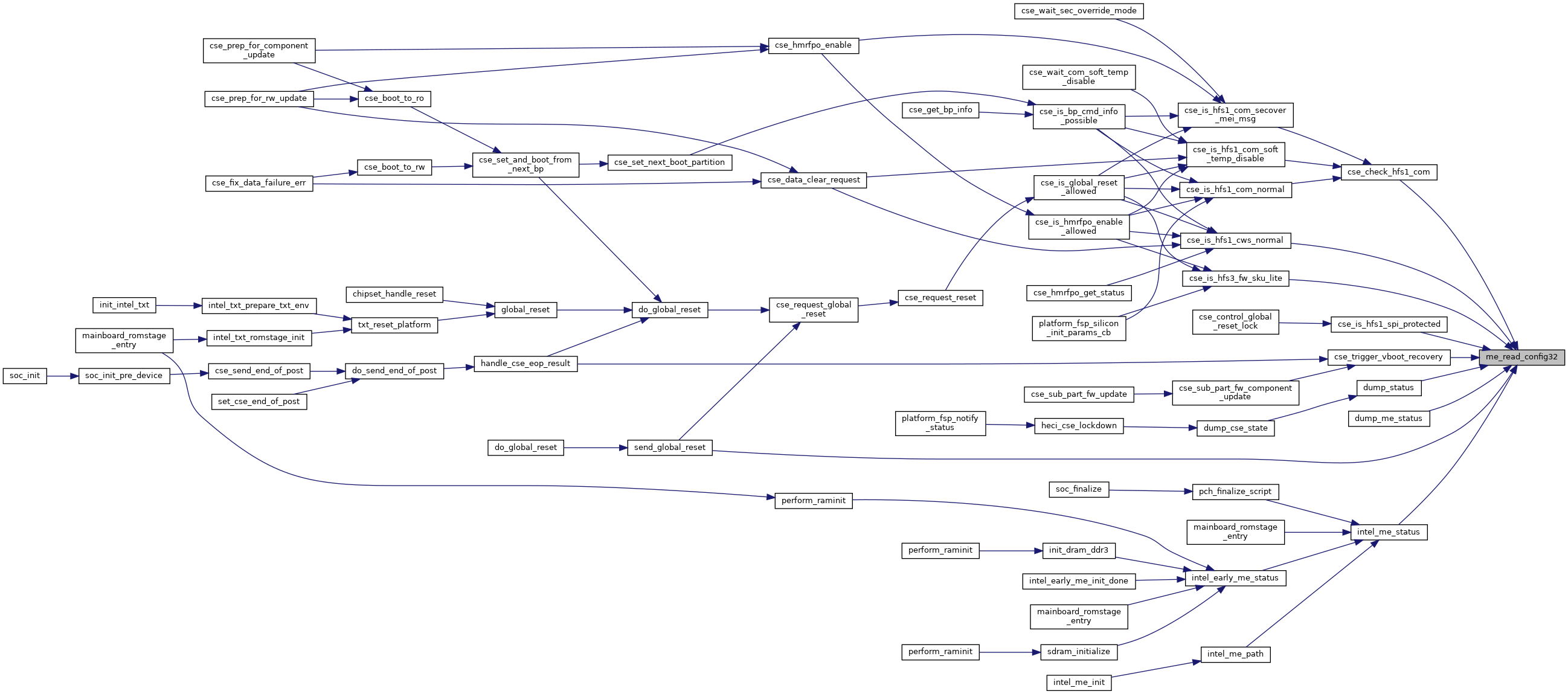

| int cse_hmrfpo_enable | ( | void | ) |

Definition at line 748 of file cse.c.

References __packed, BIOS_DEBUG, BIOS_ERR, cse_is_hfs1_com_secover_mei_msg(), cse_is_hmrfpo_enable_allowed(), HECI_MKHI_ADDR, heci_send_receive(), MKHI_GROUP_ID_HMRFPO, MKHI_HMRFPO_ENABLE, and printk.

Referenced by cse_prep_for_component_update(), and cse_prep_for_rw_update().

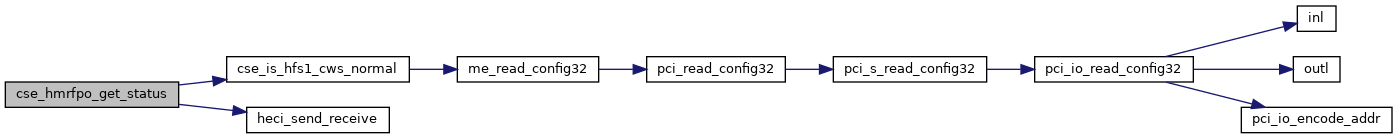

| int cse_hmrfpo_get_status | ( | void | ) |

Definition at line 812 of file cse.c.

References __packed, BIOS_ERR, BIOS_INFO, cse_is_hfs1_cws_normal(), HECI_MKHI_ADDR, heci_send_receive(), MKHI_GROUP_ID_HMRFPO, MKHI_HMRFPO_GET_STATUS, and printk.

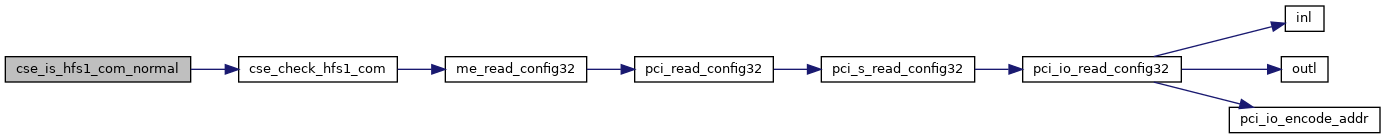

Definition at line 250 of file cse.c.

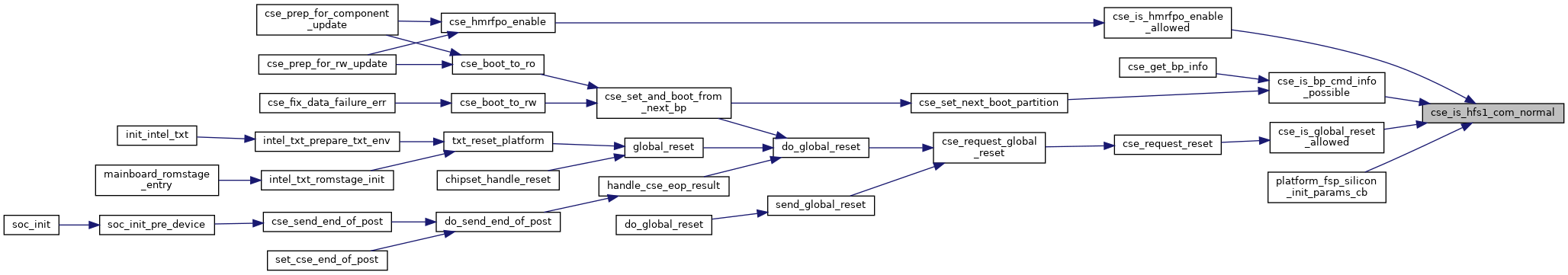

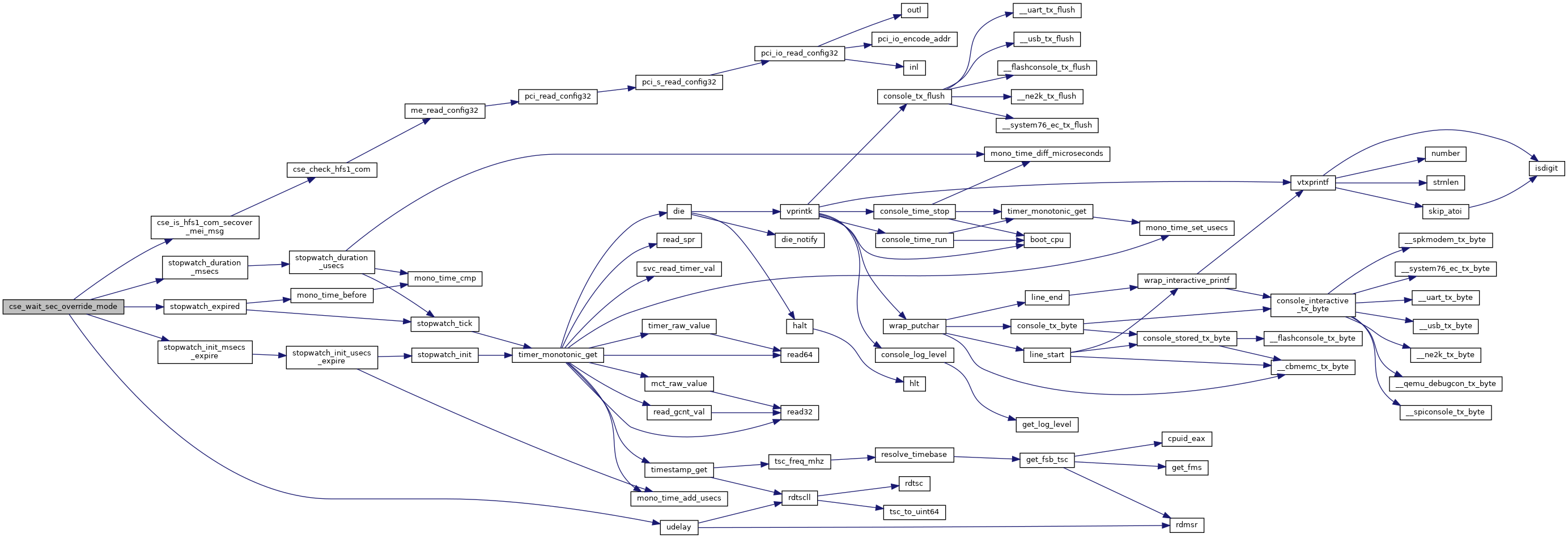

References cse_check_hfs1_com(), and ME_HFS1_COM_NORMAL.

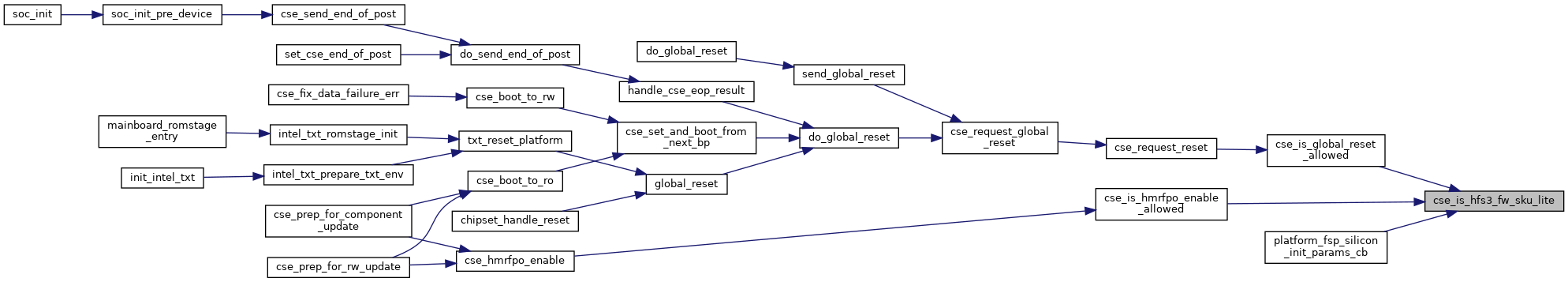

Referenced by cse_is_bp_cmd_info_possible(), cse_is_global_reset_allowed(), cse_is_hmrfpo_enable_allowed(), and platform_fsp_silicon_init_params_cb().

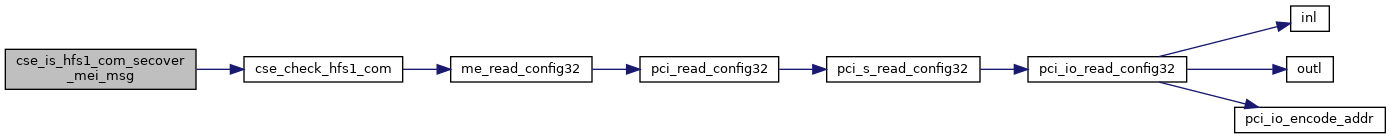

Definition at line 255 of file cse.c.

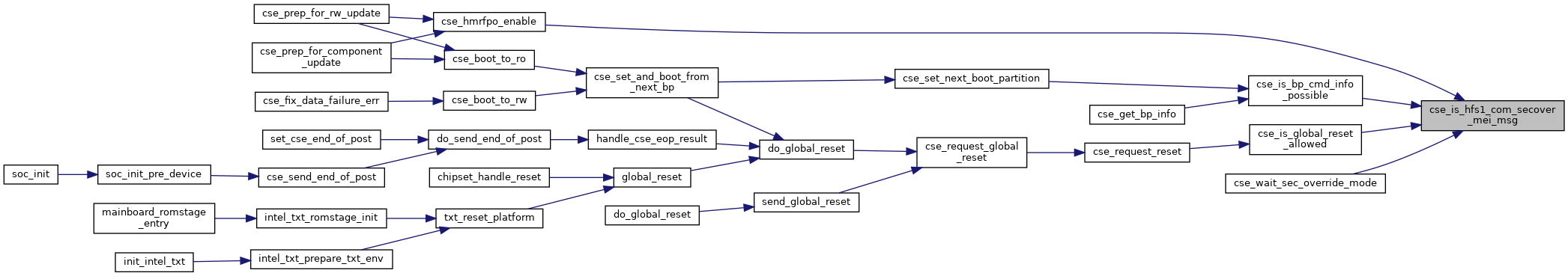

References cse_check_hfs1_com(), and ME_HFS1_COM_SECOVER_MEI_MSG.

Referenced by cse_hmrfpo_enable(), cse_is_bp_cmd_info_possible(), cse_is_global_reset_allowed(), and cse_wait_sec_override_mode().

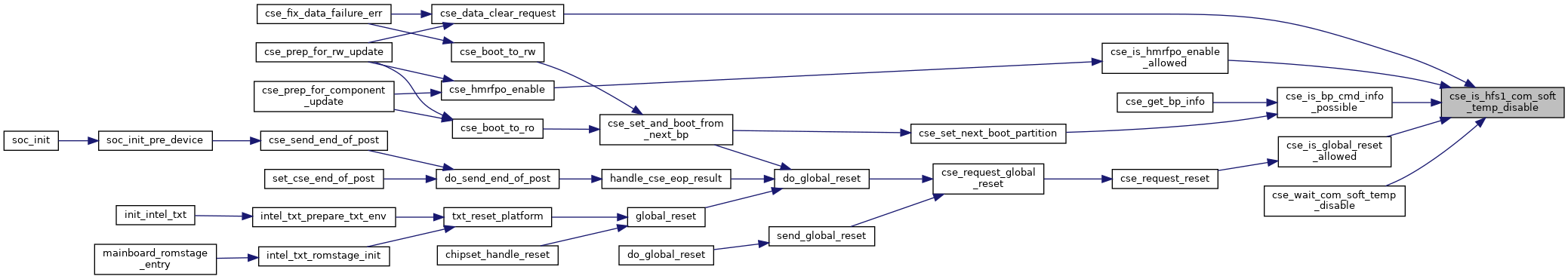

Definition at line 260 of file cse.c.

References cse_check_hfs1_com(), and ME_HFS1_COM_SOFT_TEMP_DISABLE.

Referenced by cse_data_clear_request(), cse_is_bp_cmd_info_possible(), cse_is_global_reset_allowed(), cse_is_hmrfpo_enable_allowed(), and cse_wait_com_soft_temp_disable().

Definition at line 241 of file cse.c.

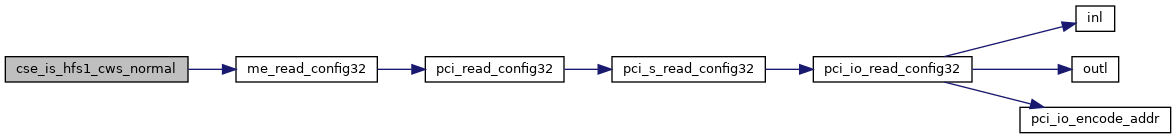

References me_hfsts1::data, me_hfsts1::fields, ME_HFS1_CWS_NORMAL, me_read_config32(), PCI_ME_HFSTS1, and me_hfsts1::working_state.

Referenced by cse_data_clear_request(), cse_hmrfpo_get_status(), cse_is_bp_cmd_info_possible(), cse_is_global_reset_allowed(), and cse_is_hmrfpo_enable_allowed().

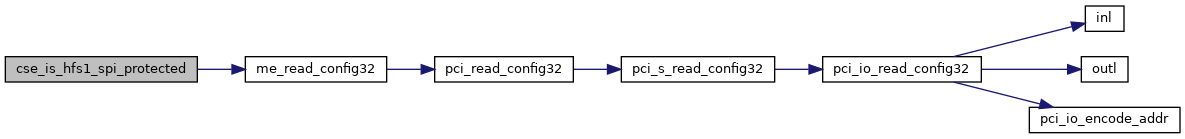

Definition at line 274 of file cse.c.

References me_hfsts1::data, me_hfsts1::fields, me_read_config32(), me_hfsts1::mfg_mode, and PCI_ME_HFSTS1.

Referenced by cse_control_global_reset_lock().

Definition at line 281 of file cse.c.

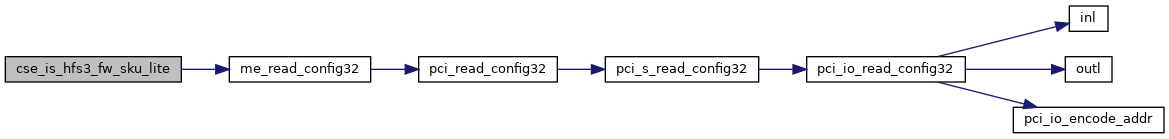

References me_hfsts3::data, me_hfsts3::fields, me_hfsts3::fw_sku, ME_HFS3_FW_SKU_LITE, me_read_config32(), and PCI_ME_HFSTS3.

Referenced by cse_is_global_reset_allowed(), cse_is_hmrfpo_enable_allowed(), and platform_fsp_silicon_init_params_cb().

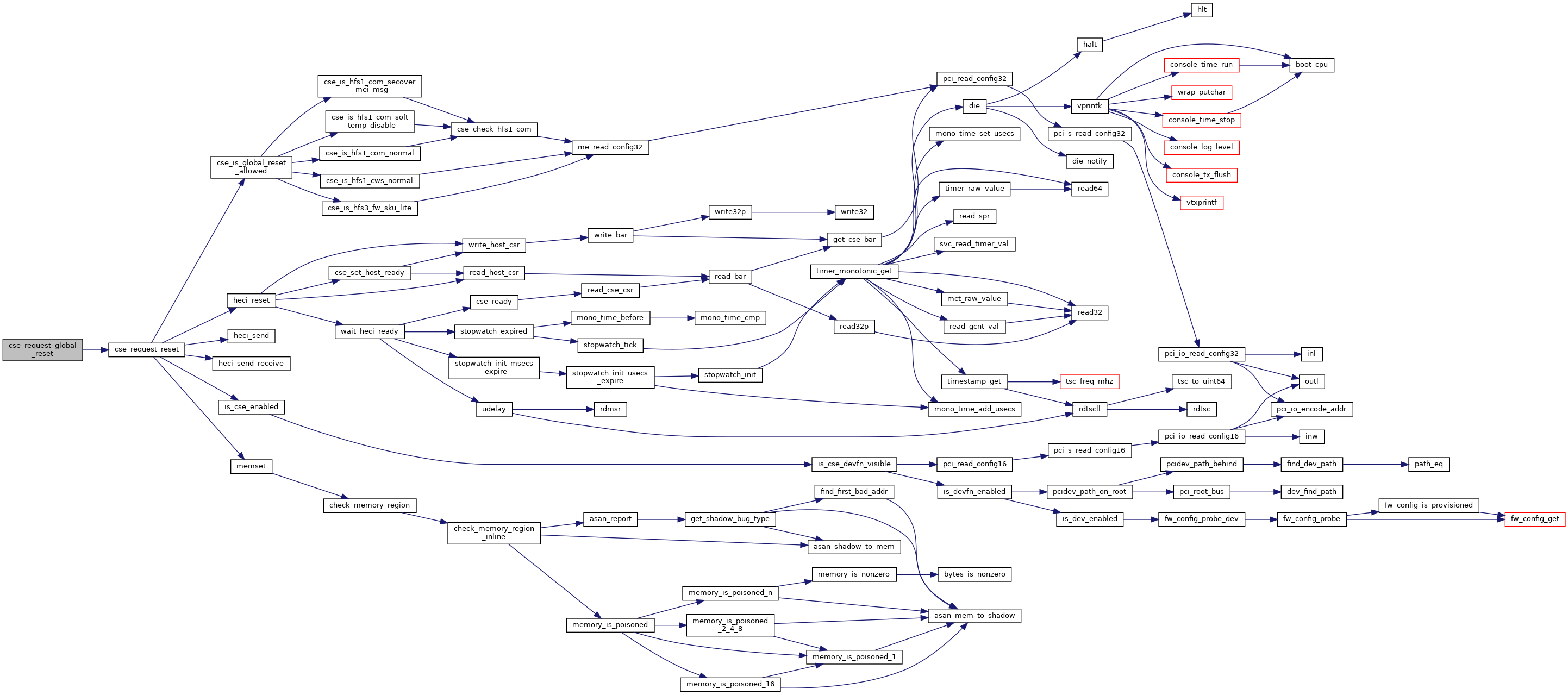

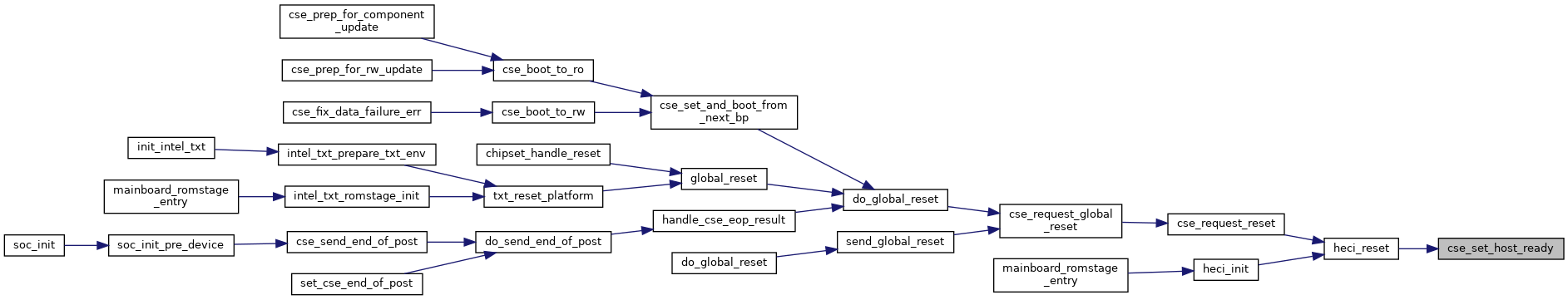

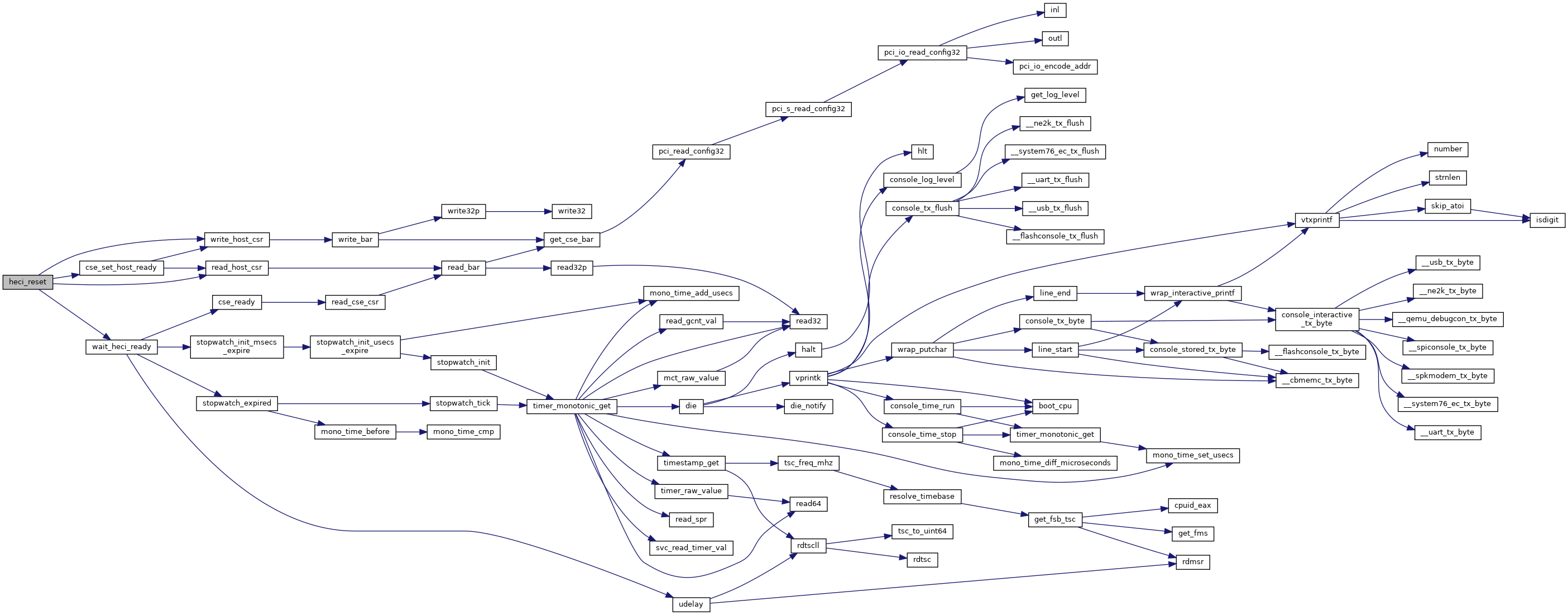

| int cse_request_global_reset | ( | void | ) |

Definition at line 722 of file cse.c.

References cse_request_reset(), and GLOBAL_RESET.

Referenced by do_global_reset(), and send_global_reset().

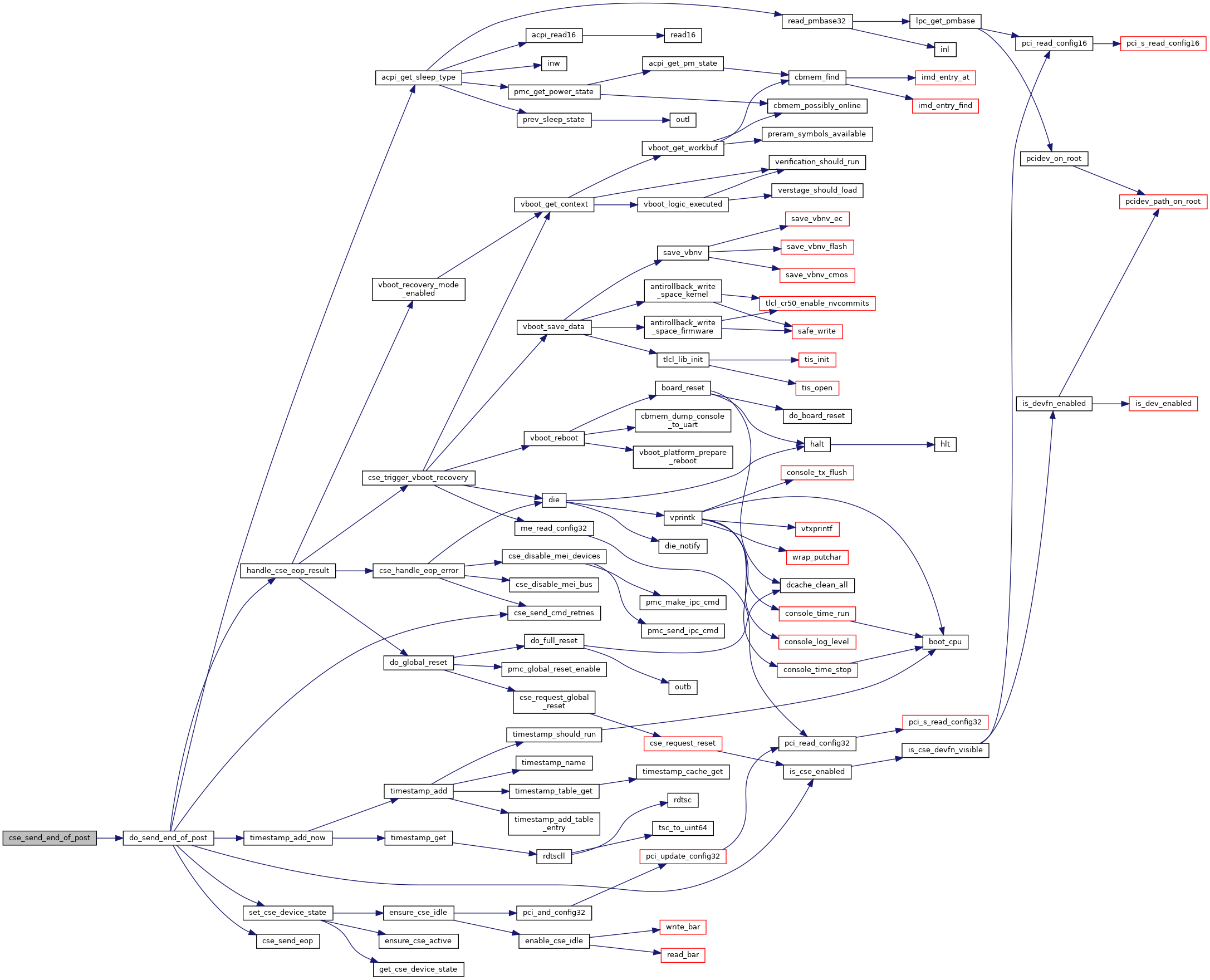

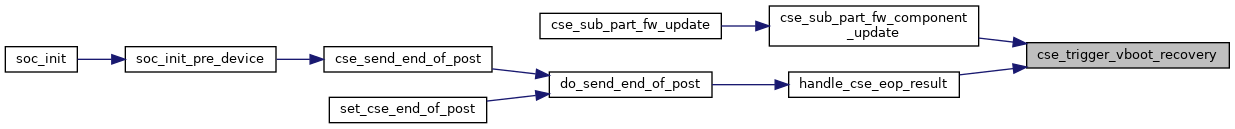

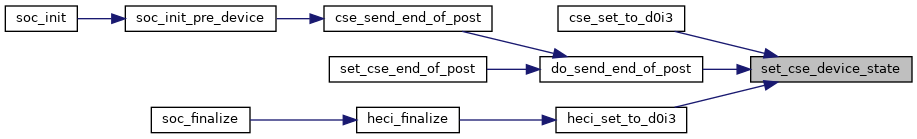

Definition at line 236 of file cse_eop.c.

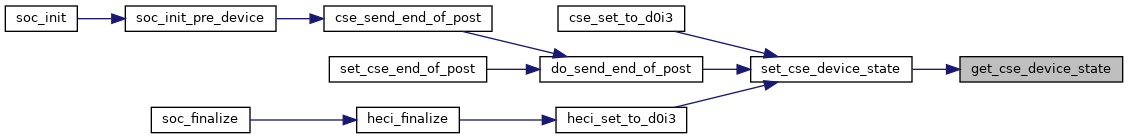

References do_send_end_of_post().

Referenced by soc_init_pre_device().

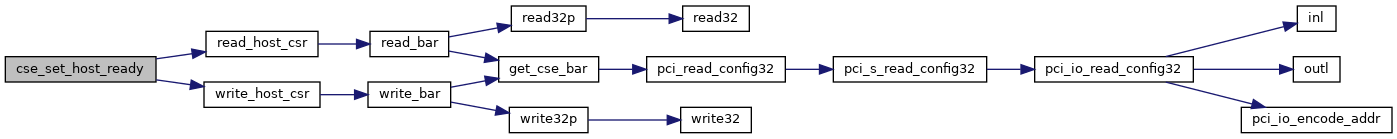

Definition at line 289 of file cse.c.

References CSR_IG, CSR_READY, CSR_RESET, read_host_csr(), and write_host_csr().

Referenced by heci_reset().

Definition at line 1003 of file cse.c.

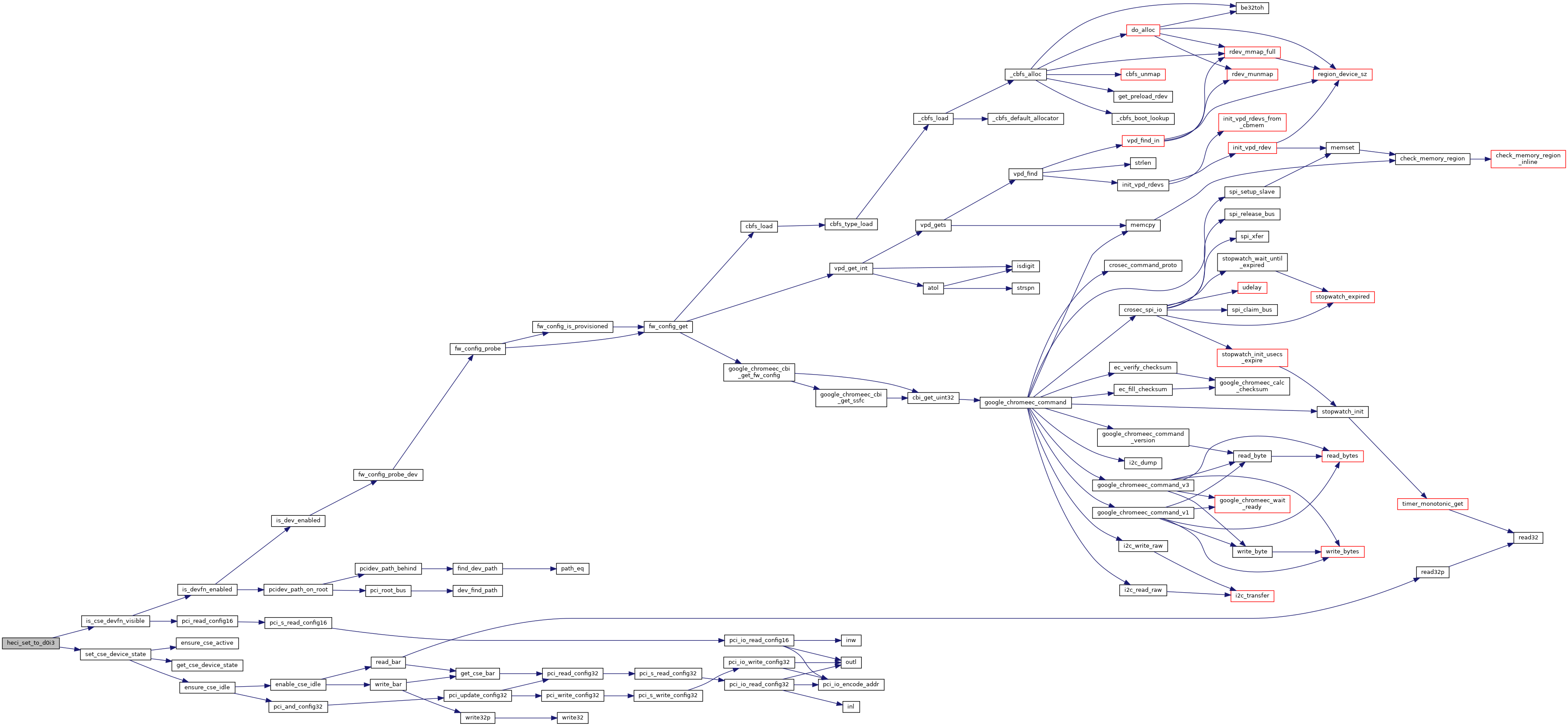

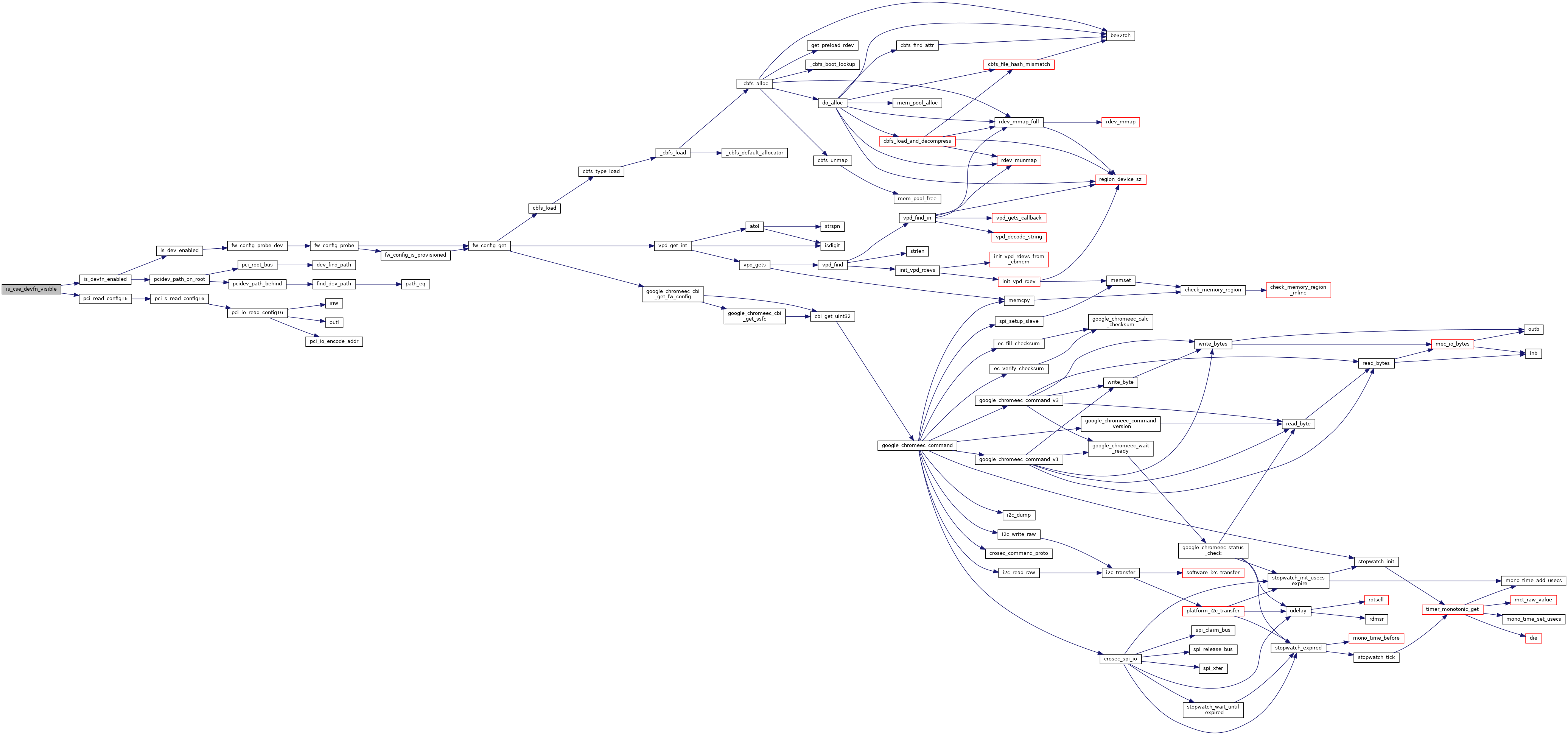

References DEV_IDLE, is_cse_devfn_visible(), PCH_DEVFN_CSE, and set_cse_device_state().

| void cse_trigger_vboot_recovery | ( | enum csme_failure_reason | reason | ) |

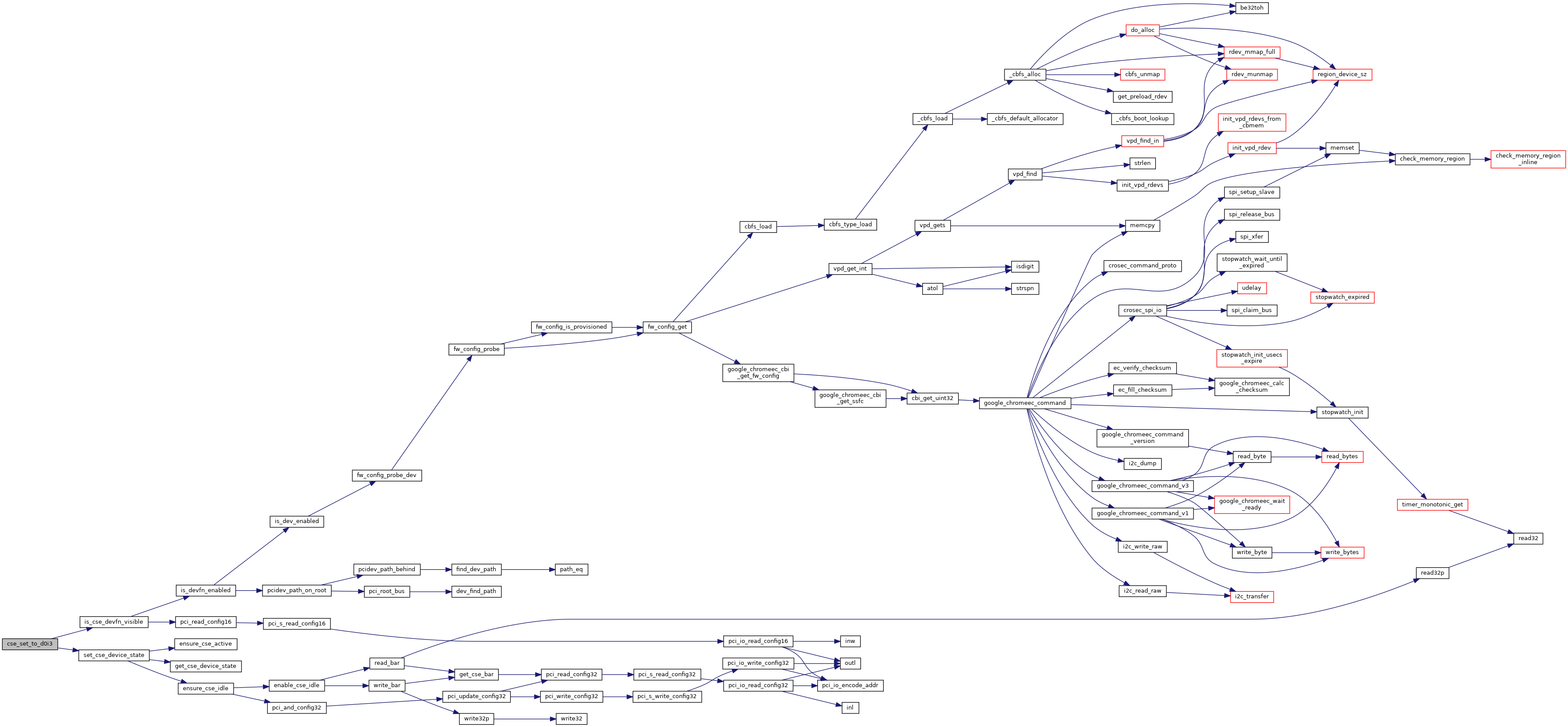

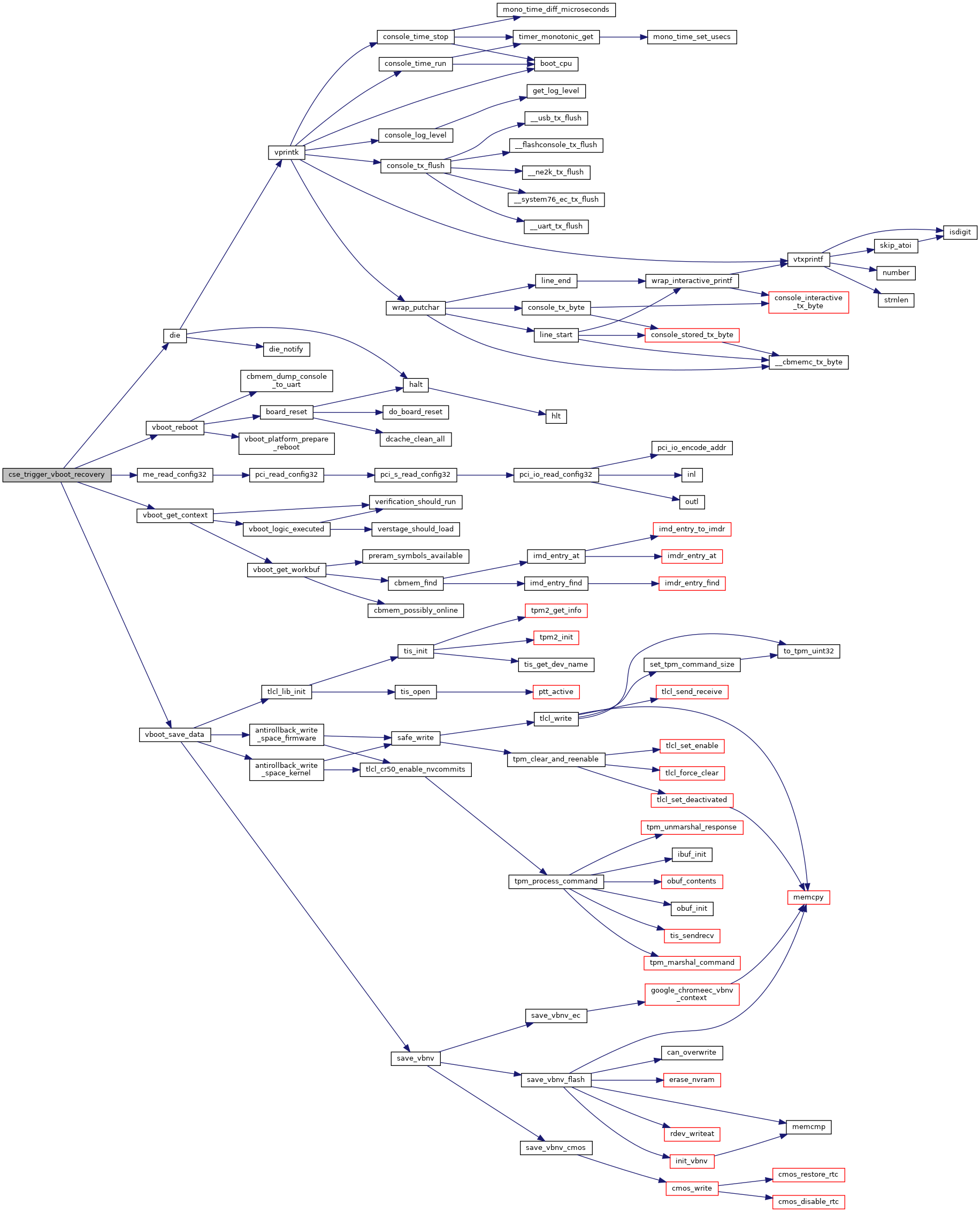

Definition at line 918 of file cse.c.

References BIOS_DEBUG, CONFIG, die(), me_read_config32(), NULL, PCI_ME_HFSTS1, PCI_ME_HFSTS2, PCI_ME_HFSTS3, printk, vboot_get_context(), vboot_reboot(), and vboot_save_data().

Referenced by cse_sub_part_fw_component_update(), and handle_cse_eop_result().

Definition at line 319 of file cse.c.

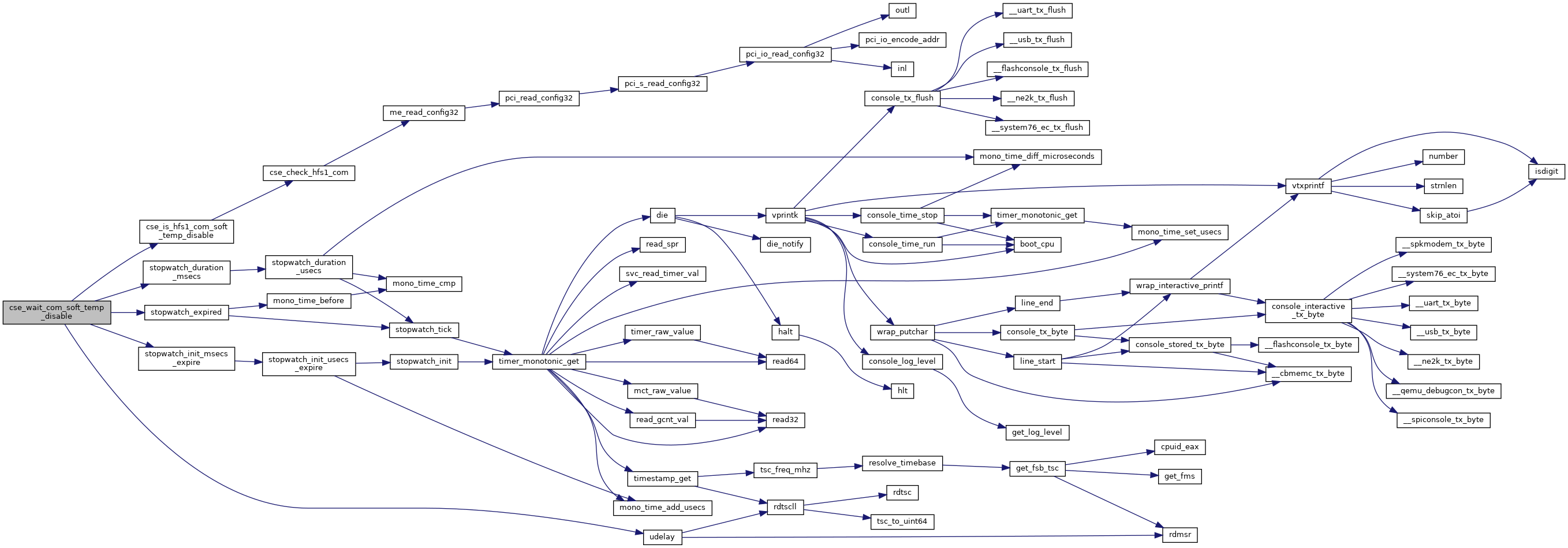

References BIOS_ERR, BIOS_SPEW, CSE_DELAY_BOOT_TO_RO_MS, cse_is_hfs1_com_soft_temp_disable(), HECI_DELAY_US, printk, stopwatch_duration_msecs(), stopwatch_expired(), stopwatch_init_msecs_expire(), and udelay().

Definition at line 299 of file cse.c.

References BIOS_DEBUG, BIOS_ERR, cse_is_hfs1_com_secover_mei_msg(), HECI_DELAY_READY_MS, HECI_DELAY_US, printk, stopwatch_duration_msecs(), stopwatch_expired(), stopwatch_init_msecs_expire(), and udelay().

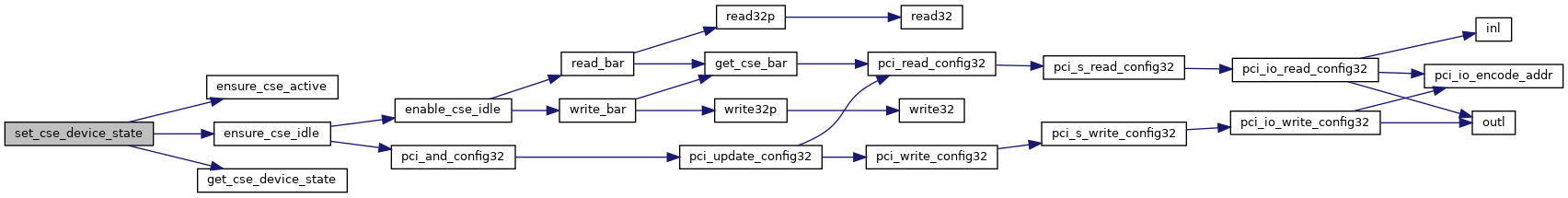

| enum cse_device_state get_cse_device_state | ( | unsigned int | devfn | ) |

Definition at line 954 of file cse.c.

Referenced by set_cse_device_state().

| enum cb_err get_me_fw_version | ( | struct me_fw_ver_resp * | resp | ) |

Definition at line 855 of file cse.c.

References BIOS_DEBUG, me_version::build, CB_SUCCESS, me_fw_ver_resp::code, CONFIG, me_version::hotfix, me_version::major, me_version::minor, and printk.

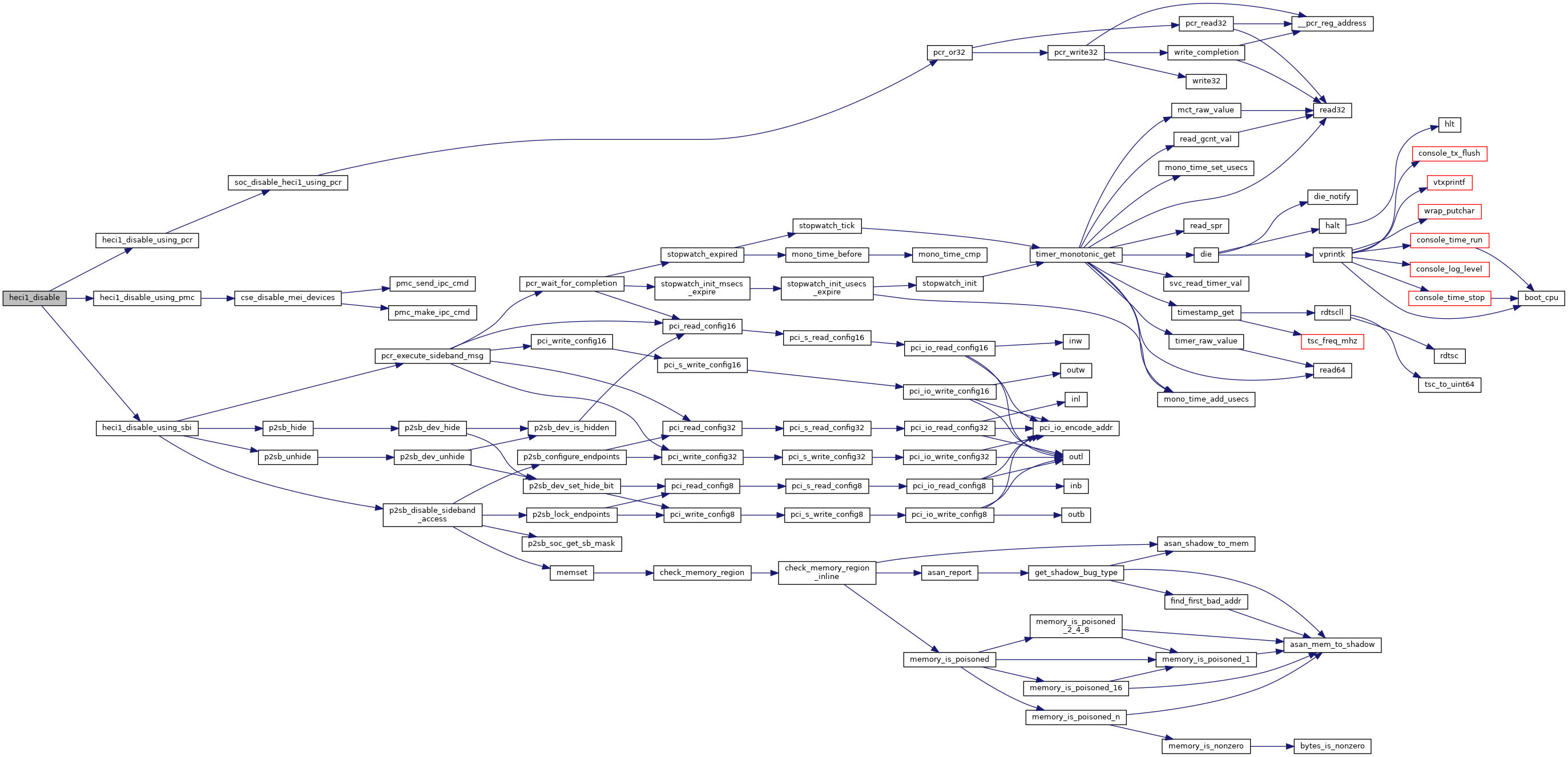

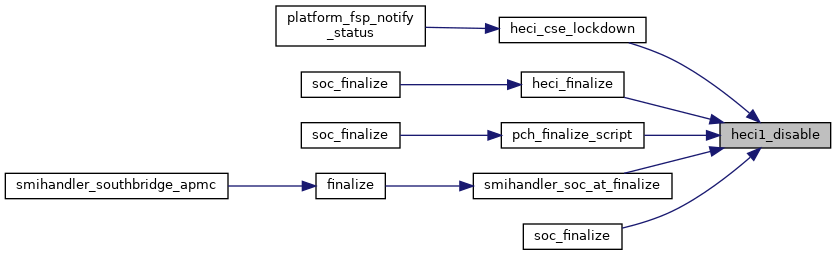

Definition at line 84 of file disable_heci.c.

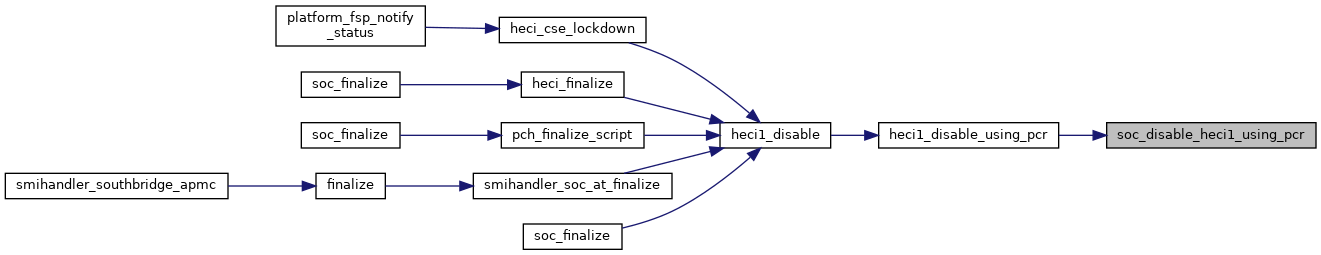

References BIOS_ERR, BIOS_INFO, CONFIG, ENV_SMM, heci1_disable_using_pcr(), heci1_disable_using_pmc(), heci1_disable_using_sbi(), and printk.

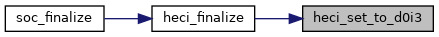

Referenced by heci_cse_lockdown(), heci_finalize(), pch_finalize_script(), smihandler_soc_at_finalize(), and soc_finalize().

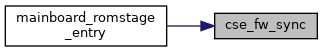

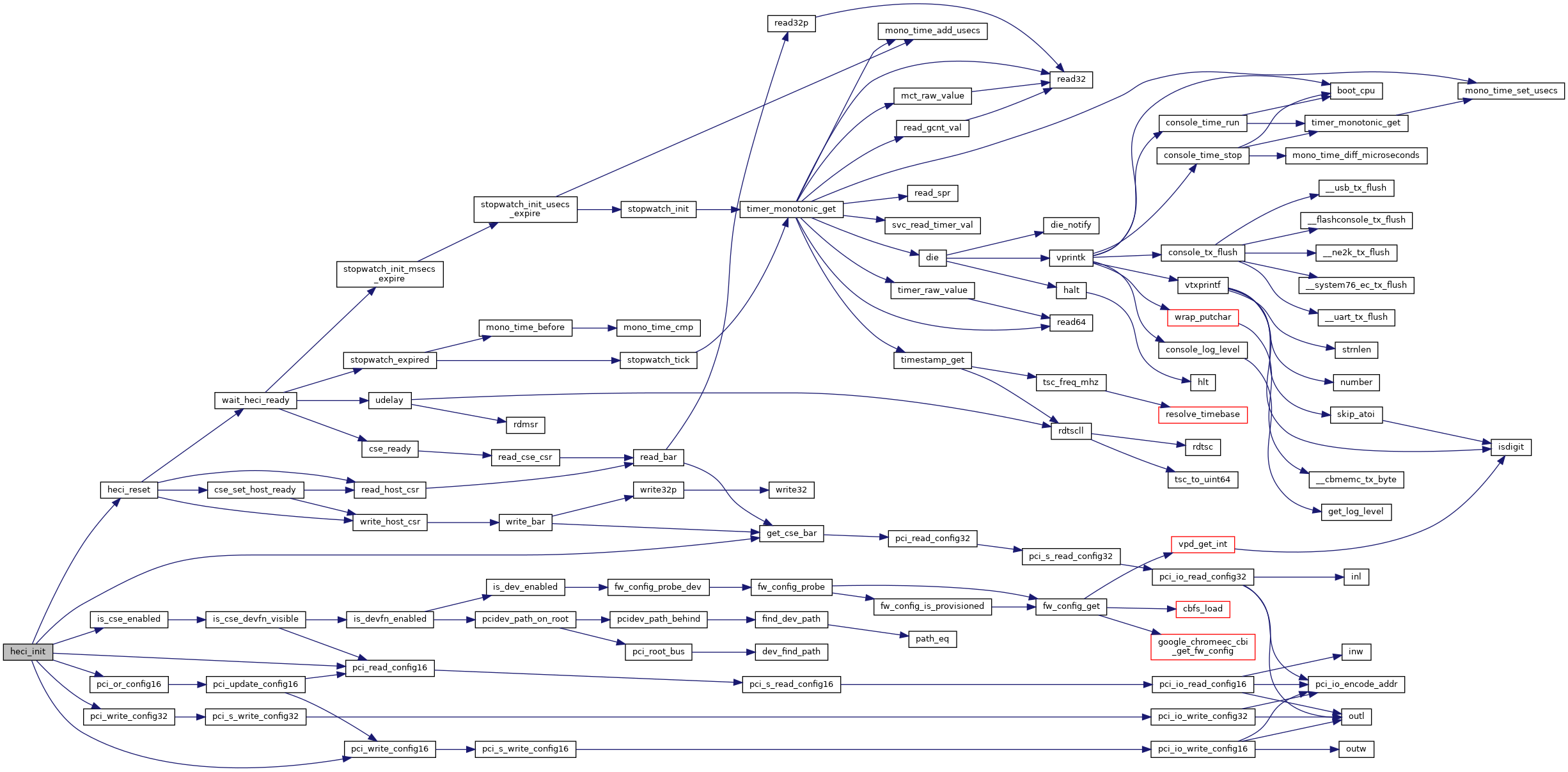

Definition at line 92 of file cse.c.

References get_cse_bar(), HECI1_BASE_ADDRESS, heci_reset(), is_cse_enabled(), PCH_DEV_CSE, PCI_BASE_ADDRESS_0, PCI_BASE_ADDRESS_1, PCI_COMMAND, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, pci_or_config16(), pci_read_config16(), pci_write_config16(), and pci_write_config32().

Referenced by mainboard_romstage_entry().

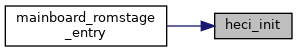

| int heci_reset | ( | void | ) |

Definition at line 599 of file cse.c.

References BIOS_CRIT, cse_set_host_ready(), CSR_IG, CSR_RESET, post_code, printk, read_host_csr(), wait_heci_ready(), and write_host_csr().

Referenced by cse_request_reset(), and heci_init().

| enum cse_tx_rx_status heci_send_receive | ( | const void * | snd_msg, |

| size_t | snd_sz, | ||

| void * | rcv_msg, | ||

| size_t * | rcv_sz, | ||

| uint8_t | cse_addr | ||

| ) |

Definition at line 363 of file cse.c.

Referenced by cse_data_clear_request(), cse_get_boot_performance_data(), cse_get_bp_info(), cse_hmrfpo_enable(), cse_hmrfpo_get_status(), cse_request_reset(), cse_set_next_boot_partition(), and load_cached_fpf().

Definition at line 1012 of file cse.c.

References DEV_IDLE, is_cse_devfn_visible(), PCH_DEV_SLOT_CSE, PCI_DEVFN, and set_cse_device_state().

Referenced by heci_finalize().

Definition at line 622 of file cse.c.

References BIOS_WARNING, is_devfn_enabled(), PCI_DEV, PCI_FUNC, pci_read_config16(), PCI_SLOT, PCI_VENDOR_ID, and printk.

Referenced by cse_set_to_d0i3(), heci_set_to_d0i3(), and is_cse_enabled().

Definition at line 640 of file cse.c.

References is_cse_devfn_visible(), and PCH_DEVFN_CSE.

Referenced by cse_get_telemetry_data(), cse_request_reset(), do_send_end_of_post(), dump_cse_state(), dump_me_status(), heci_init(), intel_me_status(), and send_global_reset().

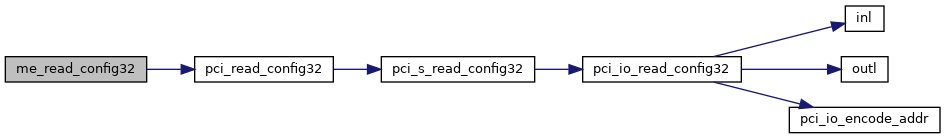

| uint32_t me_read_config32 | ( | int | offset | ) |

Definition at line 645 of file cse.c.

References offset, PCH_DEV_CSE, and pci_read_config32().

Referenced by cse_check_hfs1_com(), cse_is_hfs1_cws_normal(), cse_is_hfs1_spi_protected(), cse_is_hfs3_fw_sku_lite(), cse_trigger_vboot_recovery(), dump_me_status(), dump_status(), intel_me_status(), and send_global_reset().

| bool set_cse_device_state | ( | unsigned int | devfn, |

| enum cse_device_state | requested_state | ||

| ) |

Definition at line 987 of file cse.c.

References DEV_ACTIVE, ensure_cse_active(), ensure_cse_idle(), get_cse_device_state(), PCI_DEV, PCI_FUNC, and PCI_SLOT.

Referenced by cse_set_to_d0i3(), do_send_end_of_post(), and heci_set_to_d0i3().

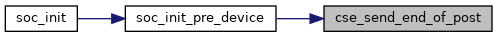

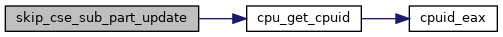

Definition at line 29 of file romstage.c.

References cpu_get_cpuid(), and CPUID_ALDERLAKE_K0.

Referenced by cse_sub_part_fw_update().

Definition at line 195 of file cse.c.

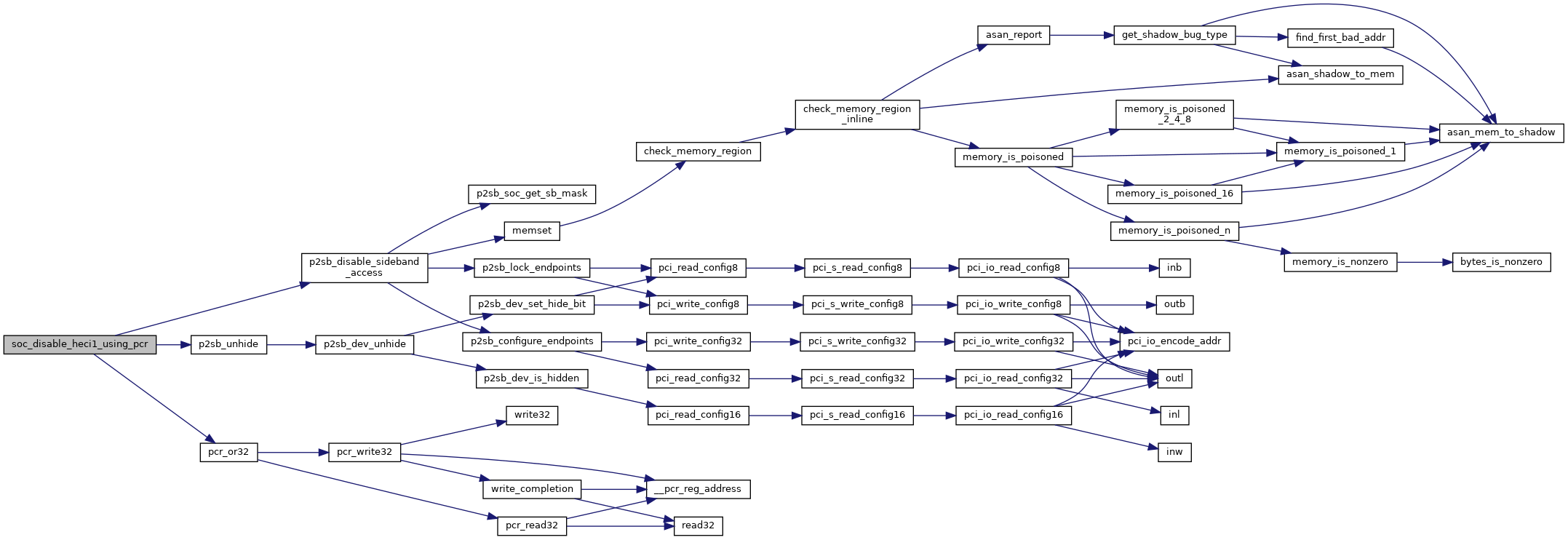

References p2sb_disable_sideband_access(), p2sb_unhide(), pcr_or32(), PCR_PSFX_T0_SHDW_PCIEN, PCR_PSFX_T0_SHDW_PCIEN_FUNDIS, PID_PSF1, PID_PSF3, PSF3_BASE_ADDRESS, and PSF_BASE_ADDRESS.

Referenced by heci1_disable_using_pcr().

| struct cse_boot_perf_rsp __packed |