|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

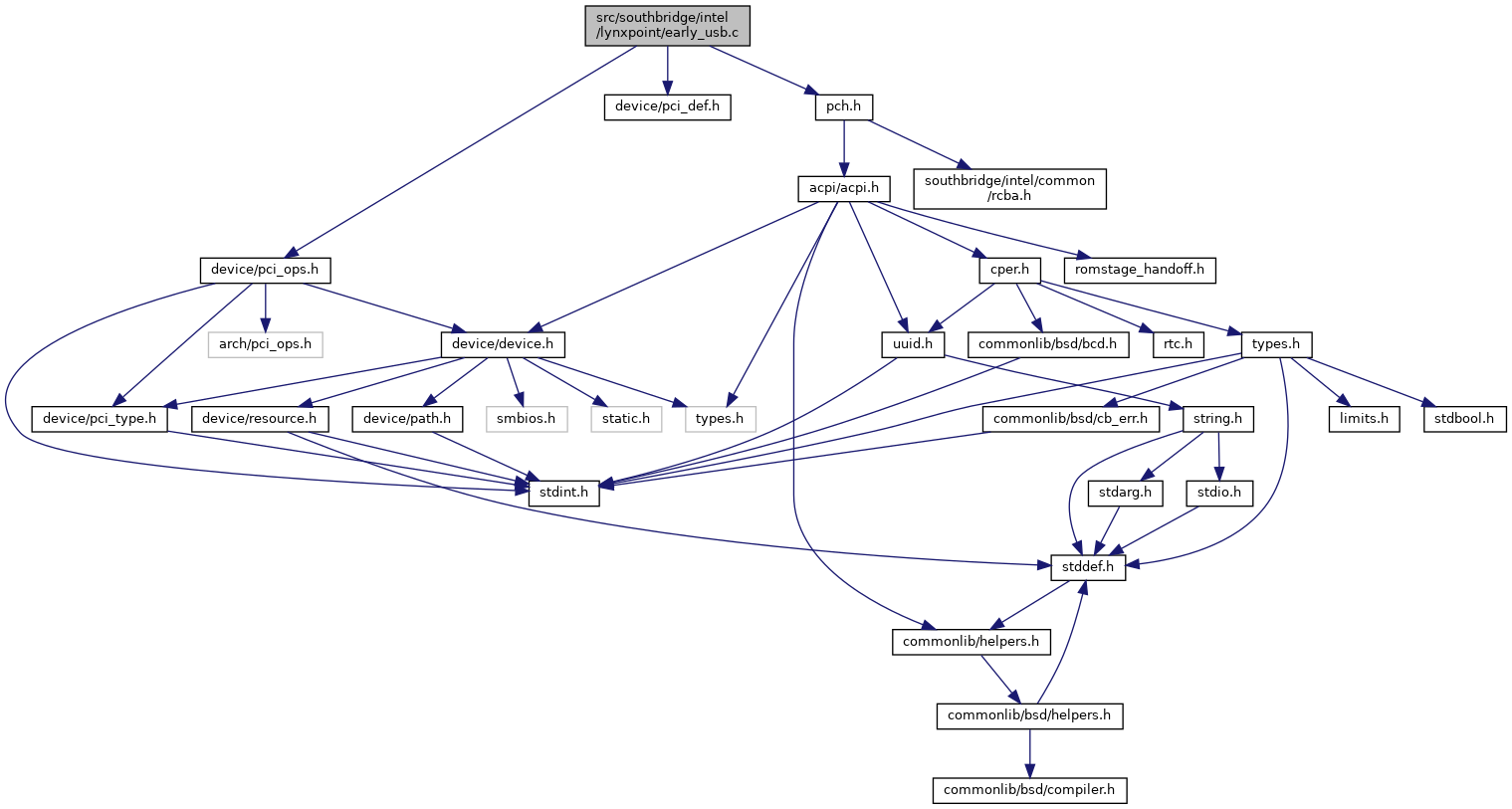

Go to the source code of this file.

Macros | |

| #define | PCH_EHCI1_TEMP_BAR0 CONFIG_EHCI_BAR |

| #define | PCH_EHCI2_TEMP_BAR0 (PCH_EHCI1_TEMP_BAR0 + 0x400) |

Functions | |

| static void | enable_usb_bar_on_device (pci_devfn_t dev, u32 bar) |

| void | enable_usb_bar (void) |

| #define PCH_EHCI1_TEMP_BAR0 CONFIG_EHCI_BAR |

Definition at line 11 of file early_usb.c.

| #define PCH_EHCI2_TEMP_BAR0 (PCH_EHCI1_TEMP_BAR0 + 0x400) |

Definition at line 12 of file early_usb.c.

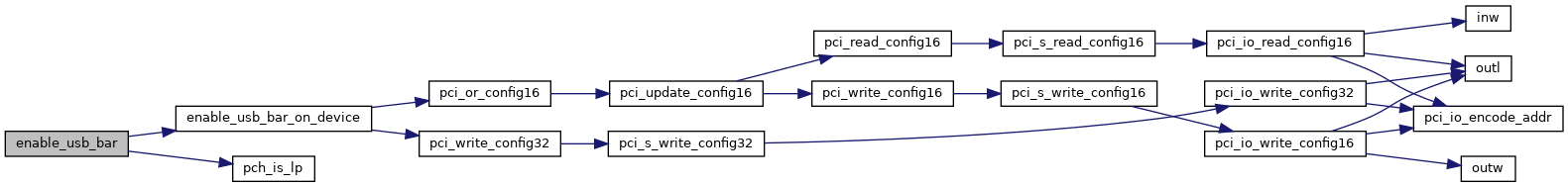

Definition at line 31 of file early_usb.c.

References enable_usb_bar_on_device(), PCH_EHCI1_DEV, PCH_EHCI1_TEMP_BAR0, PCH_EHCI2_DEV, PCH_EHCI2_TEMP_BAR0, and pch_is_lp().

|

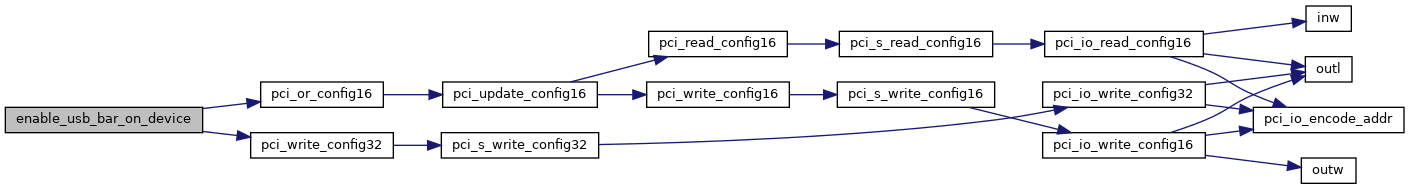

static |

Definition at line 25 of file early_usb.c.

References PCI_BASE_ADDRESS_0, PCI_COMMAND, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, pci_or_config16(), and pci_write_config32().

Referenced by enable_usb_bar().