|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

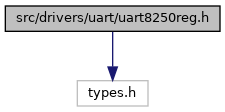

#include <types.h>

Go to the source code of this file.

Macros | |

| #define | UART8250_RBR 0x00 |

| #define | UART8250_TBR 0x00 |

| #define | UART8250_IER 0x01 |

| #define | UART8250_IER_MSI BIT(3) /* Enable Modem status interrupt */ |

| #define | UART8250_IER_RLSI BIT(2) /* Enable receiver line status interrupt */ |

| #define | UART8250_IER_THRI BIT(1) /* Enable Transmitter holding register int. */ |

| #define | UART8250_IER_RDI BIT(0) /* Enable receiver data interrupt */ |

| #define | UART8250_IIR 0x02 |

| #define | UART8250_IIR_NO_INT 0x01 /* No interrupts pending */ |

| #define | UART8250_IIR_ID 0x06 /* Mask for the interrupt ID */ |

| #define | UART8250_IIR_MSI 0x00 /* Modem status interrupt */ |

| #define | UART8250_IIR_THRI 0x02 /* Transmitter holding register empty */ |

| #define | UART8250_IIR_RDI 0x04 /* Receiver data interrupt */ |

| #define | UART8250_IIR_RLSI 0x06 /* Receiver line status interrupt */ |

| #define | UART8250_FCR 0x02 |

| #define | UART8250_FCR_FIFO_EN BIT(0) /* Fifo enable */ |

| #define | UART8250_FCR_CLEAR_RCVR BIT(1) /* Clear the RCVR FIFO */ |

| #define | UART8250_FCR_CLEAR_XMIT BIT(2) /* Clear the XMIT FIFO */ |

| #define | UART8250_FCR_DMA_SELECT BIT(3) /* For DMA applications */ |

| #define | UART8250_FCR_TRIGGER_MASK (3 << 6) /* Mask for the FIFO trigger range */ |

| #define | UART8250_FCR_TRIGGER_1 (0 << 6) /* Mask for trigger set at 1 */ |

| #define | UART8250_FCR_TRIGGER_4 (1 << 6) /* Mask for trigger set at 4 */ |

| #define | UART8250_FCR_TRIGGER_8 (2 << 6) /* Mask for trigger set at 8 */ |

| #define | UART8250_FCR_TRIGGER_14 (3 << 6) /* Mask for trigger set at 14 */ |

| #define | UART8250_LCR 0x03 |

| #define | UART8250_LCR_WLS_MSK 0x03 /* character length select mask */ |

| #define | UART8250_LCR_WLS_5 0x00 /* 5 bit character length */ |

| #define | UART8250_LCR_WLS_6 0x01 /* 6 bit character length */ |

| #define | UART8250_LCR_WLS_7 0x02 /* 7 bit character length */ |

| #define | UART8250_LCR_WLS_8 0x03 /* 8 bit character length */ |

| #define | UART8250_LCR_STB BIT(2) /* Number of stop Bits, off = 1, on = 1.5 or 2) */ |

| #define | UART8250_LCR_PEN BIT(3) /* Parity enable */ |

| #define | UART8250_LCR_EPS BIT(4) /* Even Parity Select */ |

| #define | UART8250_LCR_STKP BIT(5) /* Stick Parity */ |

| #define | UART8250_LCR_SBRK BIT(6) /* Set Break */ |

| #define | UART8250_LCR_DLAB BIT(7) /* Divisor latch access bit */ |

| #define | UART8250_MCR 0x04 |

| #define | UART8250_MCR_DTR BIT(0) /* DTR */ |

| #define | UART8250_MCR_RTS BIT(1) /* RTS */ |

| #define | UART8250_MCR_OUT1 BIT(2) /* Out 1 */ |

| #define | UART8250_MCR_OUT2 BIT(3) /* Out 2 */ |

| #define | UART8250_MCR_LOOP BIT(4) /* Enable loopback test mode */ |

| #define | UART8250_MCR_DMA_EN 0x04 |

| #define | UART8250_MCR_TX_DFR 0x08 |

| #define | UART8250_DLL 0x00 |

| #define | UART8250_DLM 0x01 |

| #define | UART8250_LSR 0x05 |

| #define | UART8250_LSR_DR BIT(0) /* Data ready */ |

| #define | UART8250_LSR_OE BIT(1) /* Overrun */ |

| #define | UART8250_LSR_PE BIT(2) /* Parity error */ |

| #define | UART8250_LSR_FE BIT(3) /* Framing error */ |

| #define | UART8250_LSR_BI BIT(4) /* Break */ |

| #define | UART8250_LSR_THRE BIT(5) /* Xmit holding register empty */ |

| #define | UART8250_LSR_TEMT BIT(6) /* Xmitter empty */ |

| #define | UART8250_LSR_ERR BIT(7) /* Error */ |

| #define | UART8250_MSR 0x06 |

| #define | UART8250_MSR_DCD BIT(7) /* Data Carrier Detect */ |

| #define | UART8250_MSR_RI BIT(6) /* Ring Indicator */ |

| #define | UART8250_MSR_DSR BIT(5) /* Data Set Ready */ |

| #define | UART8250_MSR_CTS BIT(4) /* Clear to Send */ |

| #define | UART8250_MSR_DDCD BIT(3) /* Delta DCD */ |

| #define | UART8250_MSR_TERI BIT(2) /* Trailing edge ring indicator */ |

| #define | UART8250_MSR_DDSR BIT(1) /* Delta DSR */ |

| #define | UART8250_MSR_DCTS BIT(0) /* Delta CTS */ |

| #define | UART8250_SCR 0x07 |

| #define | UART8250_SPR 0x07 |

| #define UART8250_DLL 0x00 |

Definition at line 62 of file uart8250reg.h.

| #define UART8250_DLM 0x01 |

Definition at line 63 of file uart8250reg.h.

| #define UART8250_FCR 0x02 |

Definition at line 28 of file uart8250reg.h.

Definition at line 30 of file uart8250reg.h.

Definition at line 31 of file uart8250reg.h.

| #define UART8250_FCR_DMA_SELECT BIT(3) /* For DMA applications */ |

Definition at line 32 of file uart8250reg.h.

| #define UART8250_FCR_FIFO_EN BIT(0) /* Fifo enable */ |

Definition at line 29 of file uart8250reg.h.

| #define UART8250_FCR_TRIGGER_1 (0 << 6) /* Mask for trigger set at 1 */ |

Definition at line 34 of file uart8250reg.h.

| #define UART8250_FCR_TRIGGER_14 (3 << 6) /* Mask for trigger set at 14 */ |

Definition at line 37 of file uart8250reg.h.

| #define UART8250_FCR_TRIGGER_4 (1 << 6) /* Mask for trigger set at 4 */ |

Definition at line 35 of file uart8250reg.h.

| #define UART8250_FCR_TRIGGER_8 (2 << 6) /* Mask for trigger set at 8 */ |

Definition at line 36 of file uart8250reg.h.

| #define UART8250_FCR_TRIGGER_MASK (3 << 6) /* Mask for the FIFO trigger range */ |

Definition at line 33 of file uart8250reg.h.

| #define UART8250_IER 0x01 |

Definition at line 13 of file uart8250reg.h.

| #define UART8250_IER_MSI BIT(3) /* Enable Modem status interrupt */ |

Definition at line 14 of file uart8250reg.h.

| #define UART8250_IER_RDI BIT(0) /* Enable receiver data interrupt */ |

Definition at line 17 of file uart8250reg.h.

| #define UART8250_IER_RLSI BIT(2) /* Enable receiver line status interrupt */ |

Definition at line 15 of file uart8250reg.h.

| #define UART8250_IER_THRI BIT(1) /* Enable Transmitter holding register int. */ |

Definition at line 16 of file uart8250reg.h.

| #define UART8250_IIR 0x02 |

Definition at line 19 of file uart8250reg.h.

| #define UART8250_IIR_ID 0x06 /* Mask for the interrupt ID */ |

Definition at line 21 of file uart8250reg.h.

| #define UART8250_IIR_MSI 0x00 /* Modem status interrupt */ |

Definition at line 23 of file uart8250reg.h.

| #define UART8250_IIR_NO_INT 0x01 /* No interrupts pending */ |

Definition at line 20 of file uart8250reg.h.

| #define UART8250_IIR_RDI 0x04 /* Receiver data interrupt */ |

Definition at line 25 of file uart8250reg.h.

| #define UART8250_IIR_RLSI 0x06 /* Receiver line status interrupt */ |

Definition at line 26 of file uart8250reg.h.

| #define UART8250_IIR_THRI 0x02 /* Transmitter holding register empty */ |

Definition at line 24 of file uart8250reg.h.

| #define UART8250_LCR 0x03 |

Definition at line 39 of file uart8250reg.h.

| #define UART8250_LCR_DLAB BIT(7) /* Divisor latch access bit */ |

Definition at line 50 of file uart8250reg.h.

| #define UART8250_LCR_EPS BIT(4) /* Even Parity Select */ |

Definition at line 47 of file uart8250reg.h.

| #define UART8250_LCR_PEN BIT(3) /* Parity enable */ |

Definition at line 46 of file uart8250reg.h.

| #define UART8250_LCR_SBRK BIT(6) /* Set Break */ |

Definition at line 49 of file uart8250reg.h.

| #define UART8250_LCR_STB BIT(2) /* Number of stop Bits, off = 1, on = 1.5 or 2) */ |

Definition at line 45 of file uart8250reg.h.

| #define UART8250_LCR_STKP BIT(5) /* Stick Parity */ |

Definition at line 48 of file uart8250reg.h.

| #define UART8250_LCR_WLS_5 0x00 /* 5 bit character length */ |

Definition at line 41 of file uart8250reg.h.

| #define UART8250_LCR_WLS_6 0x01 /* 6 bit character length */ |

Definition at line 42 of file uart8250reg.h.

| #define UART8250_LCR_WLS_7 0x02 /* 7 bit character length */ |

Definition at line 43 of file uart8250reg.h.

| #define UART8250_LCR_WLS_8 0x03 /* 8 bit character length */ |

Definition at line 44 of file uart8250reg.h.

Definition at line 40 of file uart8250reg.h.

| #define UART8250_LSR 0x05 |

Definition at line 66 of file uart8250reg.h.

| #define UART8250_LSR_BI BIT(4) /* Break */ |

Definition at line 71 of file uart8250reg.h.

| #define UART8250_LSR_DR BIT(0) /* Data ready */ |

Definition at line 67 of file uart8250reg.h.

| #define UART8250_LSR_ERR BIT(7) /* Error */ |

Definition at line 74 of file uart8250reg.h.

| #define UART8250_LSR_FE BIT(3) /* Framing error */ |

Definition at line 70 of file uart8250reg.h.

| #define UART8250_LSR_OE BIT(1) /* Overrun */ |

Definition at line 68 of file uart8250reg.h.

| #define UART8250_LSR_PE BIT(2) /* Parity error */ |

Definition at line 69 of file uart8250reg.h.

| #define UART8250_LSR_TEMT BIT(6) /* Xmitter empty */ |

Definition at line 73 of file uart8250reg.h.

| #define UART8250_LSR_THRE BIT(5) /* Xmit holding register empty */ |

Definition at line 72 of file uart8250reg.h.

| #define UART8250_MCR 0x04 |

Definition at line 52 of file uart8250reg.h.

| #define UART8250_MCR_DMA_EN 0x04 |

Definition at line 59 of file uart8250reg.h.

| #define UART8250_MCR_DTR BIT(0) /* DTR */ |

Definition at line 53 of file uart8250reg.h.

| #define UART8250_MCR_LOOP BIT(4) /* Enable loopback test mode */ |

Definition at line 57 of file uart8250reg.h.

| #define UART8250_MCR_OUT1 BIT(2) /* Out 1 */ |

Definition at line 55 of file uart8250reg.h.

| #define UART8250_MCR_OUT2 BIT(3) /* Out 2 */ |

Definition at line 56 of file uart8250reg.h.

| #define UART8250_MCR_RTS BIT(1) /* RTS */ |

Definition at line 54 of file uart8250reg.h.

| #define UART8250_MCR_TX_DFR 0x08 |

Definition at line 60 of file uart8250reg.h.

| #define UART8250_MSR 0x06 |

Definition at line 76 of file uart8250reg.h.

| #define UART8250_MSR_CTS BIT(4) /* Clear to Send */ |

Definition at line 80 of file uart8250reg.h.

| #define UART8250_MSR_DCD BIT(7) /* Data Carrier Detect */ |

Definition at line 77 of file uart8250reg.h.

Definition at line 84 of file uart8250reg.h.

| #define UART8250_MSR_DDCD BIT(3) /* Delta DCD */ |

Definition at line 81 of file uart8250reg.h.

| #define UART8250_MSR_DDSR BIT(1) /* Delta DSR */ |

Definition at line 83 of file uart8250reg.h.

| #define UART8250_MSR_DSR BIT(5) /* Data Set Ready */ |

Definition at line 79 of file uart8250reg.h.

| #define UART8250_MSR_RI BIT(6) /* Ring Indicator */ |

Definition at line 78 of file uart8250reg.h.

| #define UART8250_MSR_TERI BIT(2) /* Trailing edge ring indicator */ |

Definition at line 82 of file uart8250reg.h.

| #define UART8250_RBR 0x00 |

Definition at line 9 of file uart8250reg.h.

| #define UART8250_SCR 0x07 |

Definition at line 86 of file uart8250reg.h.

| #define UART8250_SPR 0x07 |

Definition at line 87 of file uart8250reg.h.

| #define UART8250_TBR 0x00 |

Definition at line 10 of file uart8250reg.h.