|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

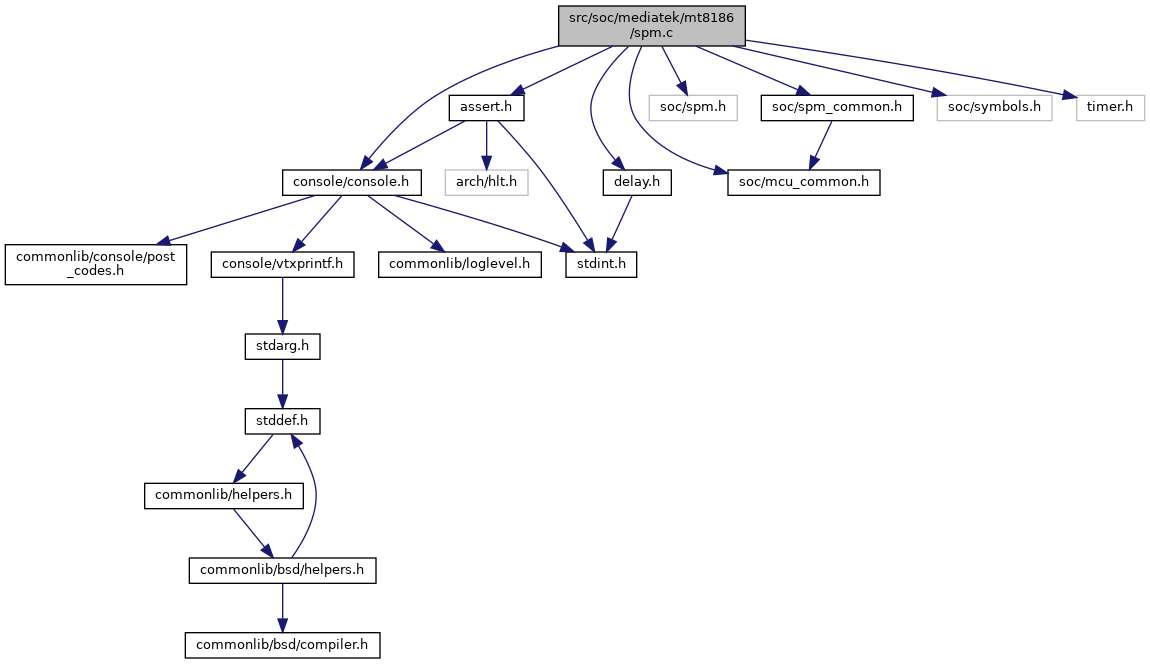

#include <assert.h>#include <console/console.h>#include <delay.h>#include <soc/mcu_common.h>#include <soc/spm.h>#include <soc/spm_common.h>#include <soc/symbols.h>#include <timer.h>

Go to the source code of this file.

Macros | |

| #define | SPM_SYSTEM_BASE_OFFSET 0x40000000 |

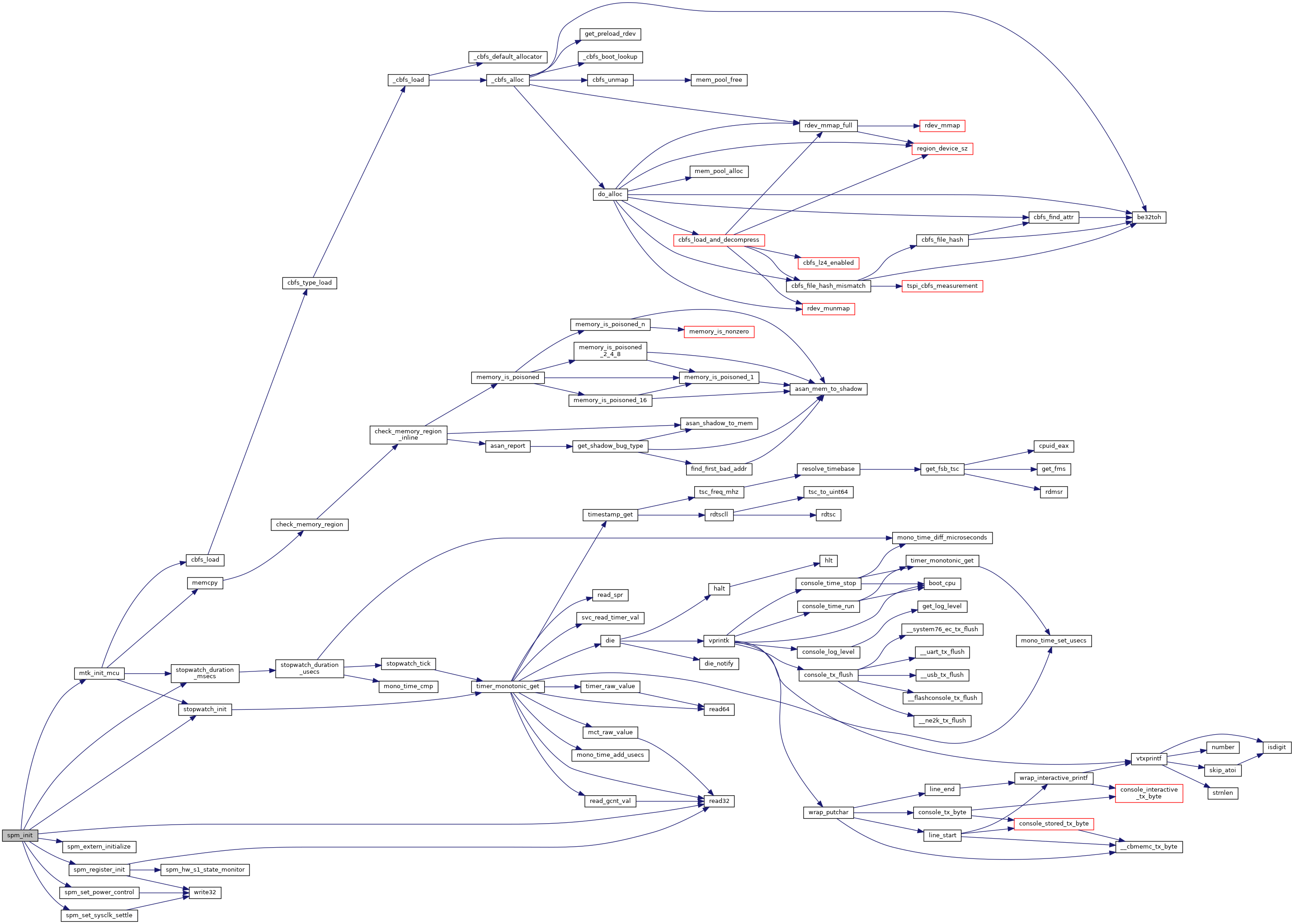

Functions | |

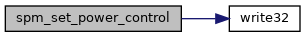

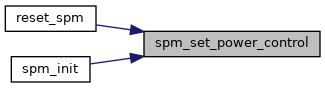

| static void | spm_set_power_control (const struct pwr_ctrl *pwrctrl) |

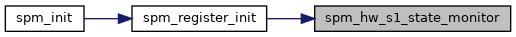

| static void | spm_hw_s1_state_monitor (int en) |

| static void | spm_register_init (void) |

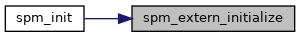

| static void | spm_extern_initialize (void) |

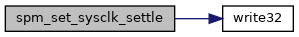

| static void | spm_set_sysclk_settle (void) |

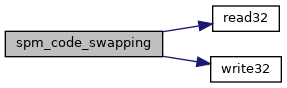

| static void | spm_code_swapping (void) |

| static void | spm_reset_and_init_pcm (void) |

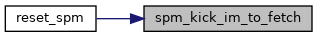

| static void | spm_kick_im_to_fetch (const struct dyna_load_pcm *pcm) |

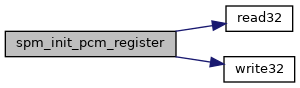

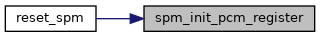

| static void | spm_init_pcm_register (void) |

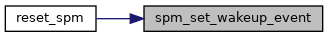

| static void | spm_set_wakeup_event (const struct pwr_ctrl *pwrctrl) |

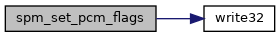

| static void | spm_set_pcm_flags (const struct pwr_ctrl *pwrctrl) |

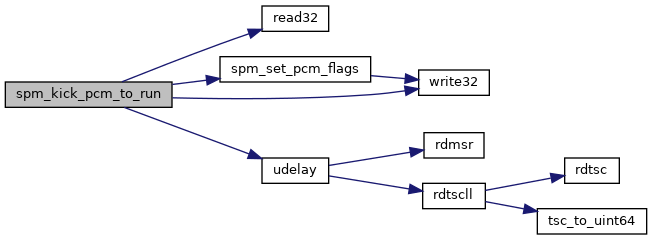

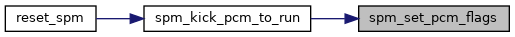

| static void | spm_kick_pcm_to_run (const struct pwr_ctrl *pwrctrl) |

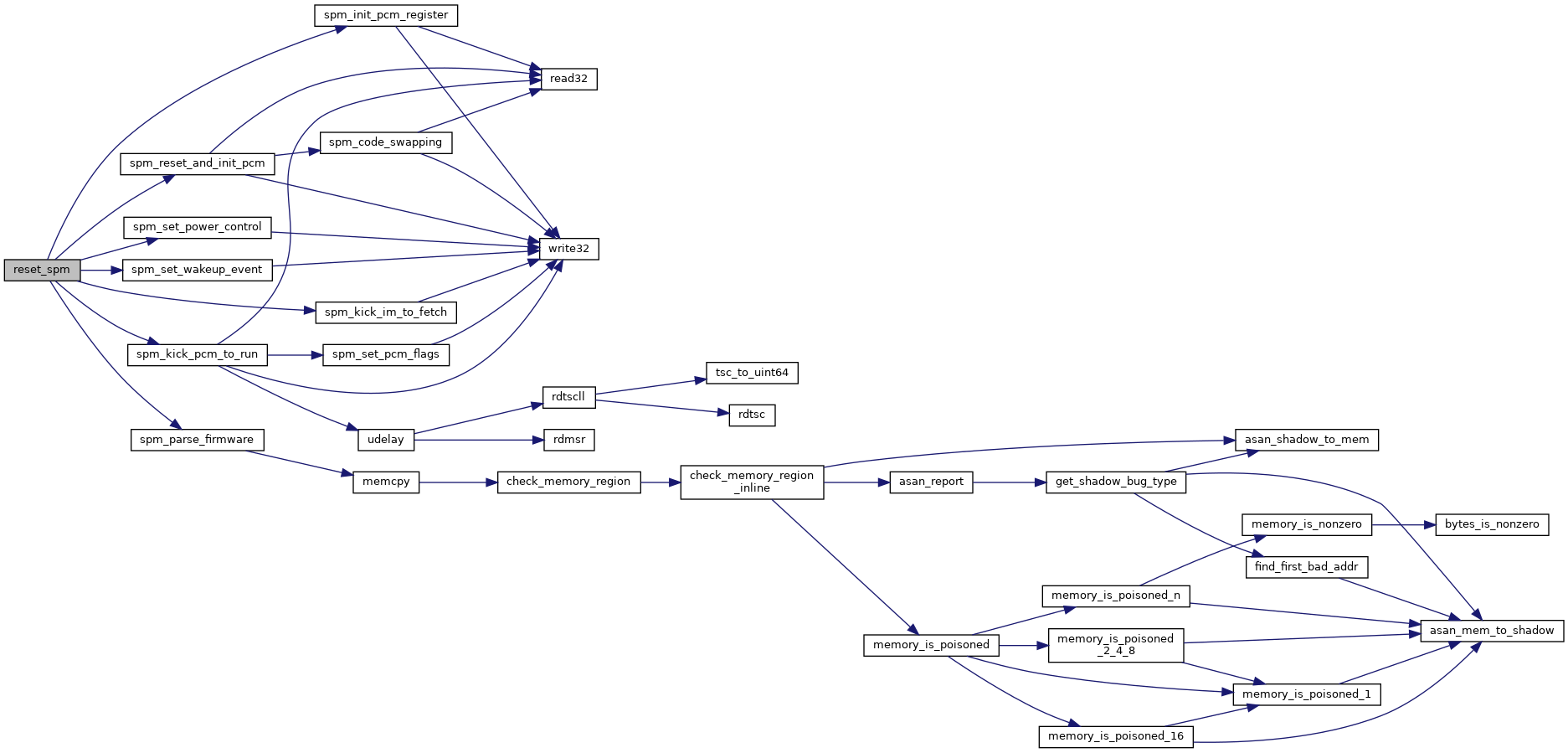

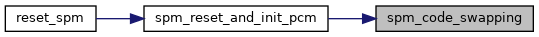

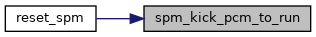

| static void | reset_spm (struct mtk_mcu *mcu) |

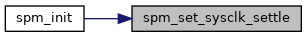

| int | spm_init (void) |

Variables | |

| static const struct pwr_ctrl | spm_init_ctrl |

| static struct mtk_mcu | spm |

Definition at line 643 of file spm.c.

References mtk_mcu::priv, spm_init_ctrl, spm_init_pcm_register(), spm_kick_im_to_fetch(), spm_kick_pcm_to_run(), spm_parse_firmware(), spm_reset_and_init_pcm(), spm_set_power_control(), and spm_set_wakeup_event().

Definition at line 465 of file spm.c.

References mask, mtk_spm, read32(), mtk_spm_regs::spm_cpu_wakeup_event, mtk_spm_regs::spm_wakeup_event_mask, SPM_WAKEUP_EVENT_MASK_BIT0, and write32().

Referenced by spm_reset_and_init_pcm().

Definition at line 453 of file spm.c.

References mtk_spm, SET32_BITFIELDS, and mtk_spm_regs::spm_dvfs_misc.

Referenced by spm_init().

|

static |

Definition at line 370 of file spm.c.

References mtk_spm, SET32_BITFIELDS, SPM_ACK_CHK_3_CON_CLR_ALL, and mtk_spm_regs::spm_ack_chk_con_3.

Referenced by spm_register_init().

| int spm_init | ( | void | ) |

Definition at line 661 of file spm.c.

References BIOS_ERR, BIOS_INFO, mtk_mcu::buffer_size, mtk_mcu::load_buffer, mtk_spm_regs::md32pcm_pc, mtk_init_mcu(), mtk_spm, printk, mtk_mcu::priv, read32(), REGION_SIZE, spm, spm_extern_initialize(), spm_init_ctrl, spm_register_init(), spm_set_power_control(), spm_set_sysclk_settle(), stopwatch_duration_msecs(), and stopwatch_init().

Definition at line 542 of file spm.c.

References mtk_spm, mtk_spm_regs::pcm_pwr_io_en, mtk_spm_regs::pcm_reg_data_ini, PCM_RF_SYNC_R0, PCM_RF_SYNC_R7, read32(), mtk_spm_regs::spm_power_on_val0, mtk_spm_regs::spm_power_on_val1, and write32().

Referenced by reset_spm().

|

static |

Definition at line 509 of file spm.c.

References assert, BIOS_DEBUG, dyna_load_pcm::buf, dyna_load_pcm::desc, pcm_desc::dmem_start, MD32PCM_DMA0_CON, MD32PCM_DMA0_CON_VAL, MD32PCM_DMA0_COUNT, MD32PCM_DMA0_DST, MD32PCM_DMA0_SRC, MD32PCM_DMA0_START, MD32PCM_DMA0_START_VAL, MD32PCM_DMA0_WPPT, MD32PCM_DMA0_WPTO, mtk_spm, PCM_CK_EN_LSB, mtk_spm_regs::pcm_con0, pcm_desc::pmem_start, pcm_desc::pmem_words, printk, setbits32, SPM_REGWR_CFG_KEY, SPM_SYSTEM_BASE_OFFSET, pcm_desc::total_words, and write32().

Referenced by reset_spm().

Definition at line 619 of file spm.c.

References MD32PCM_CFGREG_SW_RSTN, MD32PCM_CFGREG_SW_RSTN_RESET, MD32PCM_DMA0_RLCT, mtk_spm, PCM_CK_EN_LSB, mtk_spm_regs::pcm_con0, mtk_spm_regs::pcm_reg_data_ini, read32(), SET32_BITFIELDS, setbits32, mtk_spm_regs::spm_bus_protect2_mask_b, SPM_BUS_PROTECT2_MASK_B_DEF, mtk_spm_regs::spm_bus_protect_mask_b, SPM_BUS_PROTECT_MASK_B_DEF, SPM_INIT_DONE_US, SPM_REGWR_CFG_KEY, spm_set_pcm_flags(), udelay(), and write32().

Referenced by reset_spm().

Definition at line 386 of file spm.c.

References AP_PLL_CON3, AP_PLL_CON4, APMIX_CON3_DEF, APMIX_CON4_DEF, mtk_spm_regs::armpll_clk_sel, ARMPLL_CLK_SEL_DEF, BCLK_CG_EN_LSB, CLK_SCP_CFG_0, CLK_SCP_CFG_1, mtk_spm_regs::ddren_dbc_con, DDREN_DBC_EN_VAL, ISRC_ALL, ISRM_ALL, mtk_spm, PCM_CK_EN_LSB, mtk_spm_regs::pcm_con0, mtk_spm_regs::pcm_con1, mtk_spm_regs::pcm_pwr_io_en, mtk_spm_regs::pcm_reg_data_ini, PCM_RF_SYNC_R7, PCM_SW_INT_ALL, PCM_SW_RESET_LSB, POWER_ON_VAL1_DEF, mtk_spm_regs::poweron_config_set, read32(), REG_DDREN_DBC_EN_LSB, REG_MD32_APB_INTERNAL_EN_LSB, REG_SYSCLK1_SRC_MD2_SRCCLKENA, RG_AHBMIF_APBEN_LSB, SCP_CFG0_DEF, SCP_CFG1_DEF, SET32_BITFIELDS, SPM_ACK_CHK_3_HW_S1_CNT, SPM_ACK_CHK_3_SEL_HW_S1, mtk_spm_regs::spm_ack_chk_sel_3, mtk_spm_regs::spm_ack_chk_timer_3, mtk_spm_regs::spm_clk_con, SPM_DVFS_FORCE_ENABLE_LSB, mtk_spm_regs::spm_dvfs_level, SPM_DVFS_LEVEL_DEF, mtk_spm_regs::spm_dvfs_misc, SPM_DVFSRC_ENABLE_LSB, mtk_spm_regs::spm_dvs_dfs_level, SPM_DVS_DFS_LEVEL_DEF, spm_hw_s1_state_monitor(), mtk_spm_regs::spm_irq_mask, mtk_spm_regs::spm_irq_sta, mtk_spm_regs::spm_power_on_val1, SPM_REGWR_CFG_KEY, mtk_spm_regs::spm_resource_ack_con0, SPM_RESOURCE_ACK_CON0_DEF, mtk_spm_regs::spm_resource_ack_con1, SPM_RESOURCE_ACK_CON1_DEF, mtk_spm_regs::spm_resource_ack_con2, SPM_RESOURCE_ACK_CON2_DEF, mtk_spm_regs::spm_resource_ack_con3, SPM_RESOURCE_ACK_CON3_DEF, mtk_spm_regs::spm_swint_clr, mtk_spm_regs::spm_wakeup_event_mask, SPM_WAKEUP_EVENT_MASK_DEF, and write32().

Referenced by spm_init().

Definition at line 477 of file spm.c.

References clrsetbits32, MD32PCM_CFGREG_SW_RSTN, MD32PCM_CFGREG_SW_RSTN_RUN, mtk_spm, PCM_CK_EN_LSB, mtk_spm_regs::pcm_con0, mtk_spm_regs::pcm_con1, mtk_spm_regs::pcm_pwr_io_en, mtk_spm_regs::pcm_reg0_data, PCM_SW_RESET_LSB, read32(), REG_MD32_APB_INTERNAL_EN_LSB, RG_AHBMIF_APBEN_LSB, RG_PCM_TIMER_EN_LSB, RG_PCM_WDT_WAKE_LSB, spm_code_swapping(), mtk_spm_regs::spm_power_on_val0, SPM_REGWR_CFG_KEY, and write32().

Referenced by reset_spm().

Definition at line 599 of file spm.c.

References mtk_spm, pwr_ctrl::pcm_flags, pwr_ctrl::pcm_flags1, pwr_ctrl::pcm_flags1_cust_clr, pwr_ctrl::pcm_flags1_cust_set, pwr_ctrl::pcm_flags_cust_clr, pwr_ctrl::pcm_flags_cust_set, mtk_spm_regs::spm_sw_flag_0, mtk_spm_regs::spm_sw_flag_1, mtk_spm_regs::spm_sw_rsv_7, mtk_spm_regs::spm_sw_rsv_8, and write32().

Referenced by spm_kick_pcm_to_run().

Definition at line 190 of file spm.c.

References BIT, mtk_spm, mtk_spm_regs::nna_pwr_con, pwr_ctrl::reg_adsp2spm_wakeup_mask_b, pwr_ctrl::reg_afe_apsrc_req_mask_b, pwr_ctrl::reg_afe_ddren_req_mask_b, pwr_ctrl::reg_afe_infra_req_mask_b, pwr_ctrl::reg_afe_srcclkena_mask_b, pwr_ctrl::reg_afe_vrf18_req_mask_b, pwr_ctrl::reg_apu_apsrc_req_mask_b, pwr_ctrl::reg_apu_ddren_req_mask_b, pwr_ctrl::reg_apu_infra_req_mask_b, pwr_ctrl::reg_apu_srcclkena_mask_b, pwr_ctrl::reg_apu_vrf18_req_mask_b, pwr_ctrl::reg_audio_dsp_apsrc_req_mask_b, pwr_ctrl::reg_audio_dsp_ddren_req_mask_b, pwr_ctrl::reg_audio_dsp_infra_req_mask_b, pwr_ctrl::reg_audio_dsp_srcclkena_mask_b, pwr_ctrl::reg_audio_dsp_vrf18_req_mask_b, pwr_ctrl::reg_bak_psri_apsrc_req_mask_b, pwr_ctrl::reg_bak_psri_ddren_req_mask_b, pwr_ctrl::reg_bak_psri_infra_req_mask_b, pwr_ctrl::reg_bak_psri_srcclkena_mask_b, pwr_ctrl::reg_bak_psri_vrf18_req_mask_b, pwr_ctrl::reg_ccif_event_apsrc_req_mask_b, pwr_ctrl::reg_ccif_event_infra_req_mask_b, pwr_ctrl::reg_ccif_event_srcclkena_mask_b, pwr_ctrl::reg_cg_check_apsrc_req_mask_b, pwr_ctrl::reg_cg_check_ddren_req_mask_b, pwr_ctrl::reg_cg_check_srcclkena_mask_b, pwr_ctrl::reg_cg_check_vrf18_req_mask_b, pwr_ctrl::reg_conn_apsrc_req_mask_b, pwr_ctrl::reg_conn_apsrc_sel, pwr_ctrl::reg_conn_ddren_req_mask_b, pwr_ctrl::reg_conn_infra_req_mask_b, pwr_ctrl::reg_conn_srcclkena_mask_b, pwr_ctrl::reg_conn_srcclkenb2pwrap_mask_b, pwr_ctrl::reg_conn_srcclkenb_mask_b, pwr_ctrl::reg_conn_vfe28_mask_b, pwr_ctrl::reg_conn_vrf18_req_mask_b, pwr_ctrl::reg_csyspwrup_ack_mask, pwr_ctrl::reg_disp0_apsrc_req_mask_b, pwr_ctrl::reg_disp0_ddren_req_mask_b, pwr_ctrl::reg_disp1_apsrc_req_mask_b, pwr_ctrl::reg_disp1_ddren_req_mask_b, pwr_ctrl::reg_dpmaif_apsrc_req_mask_b, pwr_ctrl::reg_dpmaif_ddren_req_mask_b, pwr_ctrl::reg_dpmaif_infra_req_mask_b, pwr_ctrl::reg_dpmaif_srcclkena_mask_b, pwr_ctrl::reg_dpmaif_vrf18_req_mask_b, pwr_ctrl::reg_dramc_md32_apsrc_req_mask_b, pwr_ctrl::reg_dramc_md32_infra_req_mask_b, pwr_ctrl::reg_dramc_md32_vrf18_req_mask_b, pwr_ctrl::reg_dvfsrc_event_trigger_mask_b, pwr_ctrl::reg_ext_wakeup_event_mask, pwr_ctrl::reg_gce_apsrc_req_mask_b, pwr_ctrl::reg_gce_ddren_req_mask_b, pwr_ctrl::reg_gce_infra_req_mask_b, pwr_ctrl::reg_gce_vrf18_req_mask_b, pwr_ctrl::reg_infrasys_apsrc_req_mask_b, pwr_ctrl::reg_infrasys_ddren_req_mask_b, pwr_ctrl::reg_mcupm_apsrc_req_mask_b, pwr_ctrl::reg_mcupm_ddren_req_mask_b, pwr_ctrl::reg_mcupm_infra_req_mask_b, pwr_ctrl::reg_mcupm_srcclkena_mask_b, pwr_ctrl::reg_mcupm_vrf18_req_mask_b, pwr_ctrl::reg_mcusys_idle_mask, pwr_ctrl::reg_mcusys_merge_apsrc_req_mask_b, pwr_ctrl::reg_mcusys_merge_ddren_req_mask_b, pwr_ctrl::reg_md_0_apsrc_req_mask_b, pwr_ctrl::reg_md_0_ddren_req_mask_b, pwr_ctrl::reg_md_0_infra_req_mask_b, pwr_ctrl::reg_md_0_srcclkena_mask_b, pwr_ctrl::reg_md_0_vrf18_req_mask_b, pwr_ctrl::reg_md_1_apsrc_req_mask_b, pwr_ctrl::reg_md_1_ddren_req_mask_b, pwr_ctrl::reg_md_1_infra_req_mask_b, pwr_ctrl::reg_md_1_srcclkena_mask_b, pwr_ctrl::reg_md_1_vrf18_req_mask_b, pwr_ctrl::reg_md_apsrc_0_sel, pwr_ctrl::reg_md_apsrc_1_sel, pwr_ctrl::reg_mp0_cputop_idle_mask, pwr_ctrl::reg_mp1_cputop_idle_mask, pwr_ctrl::reg_msdc0_apsrc_req_mask_b, pwr_ctrl::reg_msdc0_ddren_req_mask_b, pwr_ctrl::reg_msdc0_infra_req_mask_b, pwr_ctrl::reg_msdc0_srcclkena_mask_b, pwr_ctrl::reg_msdc0_vrf18_req_mask_b, pwr_ctrl::reg_msdc1_apsrc_req_mask_b, pwr_ctrl::reg_msdc1_ddren_req_mask_b, pwr_ctrl::reg_msdc1_infra_req_mask_b, pwr_ctrl::reg_msdc1_srcclkena_mask_b, pwr_ctrl::reg_msdc1_vrf18_req_mask_b, pwr_ctrl::reg_msdc2_apsrc_req_mask_b, pwr_ctrl::reg_msdc2_ddren_req_mask_b, pwr_ctrl::reg_msdc2_infra_req_mask_b, pwr_ctrl::reg_msdc2_srcclkena_mask_b, pwr_ctrl::reg_msdc2_vrf18_req_mask_b, pwr_ctrl::reg_pcie_apsrc_req_mask_b, pwr_ctrl::reg_pcie_ddren_req_mask_b, pwr_ctrl::reg_pcie_infra_req_mask_b, pwr_ctrl::reg_pcie_srcclkena_mask_b, pwr_ctrl::reg_pcie_vrf18_req_mask_b, pwr_ctrl::reg_scp2spm_wakeup_mask_b, pwr_ctrl::reg_scp_apsrc_req_mask_b, pwr_ctrl::reg_scp_ddren_req_mask_b, pwr_ctrl::reg_scp_infra_req_mask_b, pwr_ctrl::reg_scp_srcclkena_mask_b, pwr_ctrl::reg_scp_vrf18_req_mask_b, pwr_ctrl::reg_spm_adsp_mailbox_req, pwr_ctrl::reg_spm_apsrc_req, pwr_ctrl::reg_spm_ddren_req, pwr_ctrl::reg_spm_dvfs_req, pwr_ctrl::reg_spm_f26m_req, pwr_ctrl::reg_spm_infra_req, pwr_ctrl::reg_spm_reserved_apsrc_req_mask_b, pwr_ctrl::reg_spm_reserved_ddren_req_mask_b, pwr_ctrl::reg_spm_reserved_infra_req_mask_b, pwr_ctrl::reg_spm_reserved_srcclkena_mask_b, pwr_ctrl::reg_spm_reserved_vrf18_req_mask_b, pwr_ctrl::reg_spm_scp_mailbox_req, pwr_ctrl::reg_spm_sspm_mailbox_req, pwr_ctrl::reg_spm_sw_mailbox_req, pwr_ctrl::reg_spm_vrf18_req, pwr_ctrl::reg_srcclkeni_infra_req_mask_b, pwr_ctrl::reg_srcclkeni_srcclkena_mask_b, pwr_ctrl::reg_sspm2spm_wakeup_mask_b, pwr_ctrl::reg_sspm_apsrc_req_mask_b, pwr_ctrl::reg_sspm_ddren_req_mask_b, pwr_ctrl::reg_sspm_infra_req_mask_b, pwr_ctrl::reg_sspm_srcclkena_mask_b, pwr_ctrl::reg_sspm_vrf18_req_mask_b, pwr_ctrl::reg_sw2spm_wakeup_mask_b, pwr_ctrl::reg_ufs_apsrc_req_mask_b, pwr_ctrl::reg_ufs_ddren_req_mask_b, pwr_ctrl::reg_ufs_infra_req_mask_b, pwr_ctrl::reg_ufs_srcclkena_mask_b, pwr_ctrl::reg_ufs_vrf18_req_mask_b, pwr_ctrl::reg_wakeup_event_mask, pwr_ctrl::reg_wfi_op, pwr_ctrl::reg_wfi_type, mtk_spm_regs::spm_ap_standby_con, mtk_spm_regs::spm_src2_mask, mtk_spm_regs::spm_src3_mask, mtk_spm_regs::spm_src4_mask, mtk_spm_regs::spm_src5_mask, mtk_spm_regs::spm_src6_mask, mtk_spm_regs::spm_src7_mask, mtk_spm_regs::spm_src_mask, mtk_spm_regs::spm_src_req, mtk_spm_regs::spm_wakeup_event_ext_mask, mtk_spm_regs::spm_wakeup_event_mask, and write32().

Referenced by reset_spm(), and spm_init().

Definition at line 460 of file spm.c.

References mtk_spm, mtk_spm_regs::spm_clk_settle, SPM_SYSCLK_SETTLE, and write32().

Referenced by spm_init().

Definition at line 557 of file spm.c.

References clrsetbits32, ISRM_RET_IRQ_AUX, mask, mtk_spm, mtk_spm_regs::pcm_con1, PCM_TIMER_MAX, mtk_spm_regs::pcm_timer_val, R12_CSYSPWREQ_B, pwr_ctrl::reg_csyspwrup_ack_mask, REG_SPM_EVENT_COUNTER_CLR_LSB, RG_PCM_TIMER_EN_LSB, SET32_BITFIELDS, setbits32, mtk_spm_regs::spm_irq_mask, SPM_REGWR_CFG_KEY, mtk_spm_regs::spm_wakeup_event_mask, mtk_spm_regs::sys_timer_con, SYS_TIMER_START_EN_LSB, pwr_ctrl::timer_val, pwr_ctrl::timer_val_cust, val, pwr_ctrl::wake_src, pwr_ctrl::wake_src_cust, and write32().

Referenced by reset_spm().

|

static |

|

static |

Definition at line 1 of file spm.c.

Referenced by reset_spm(), and spm_init().