|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

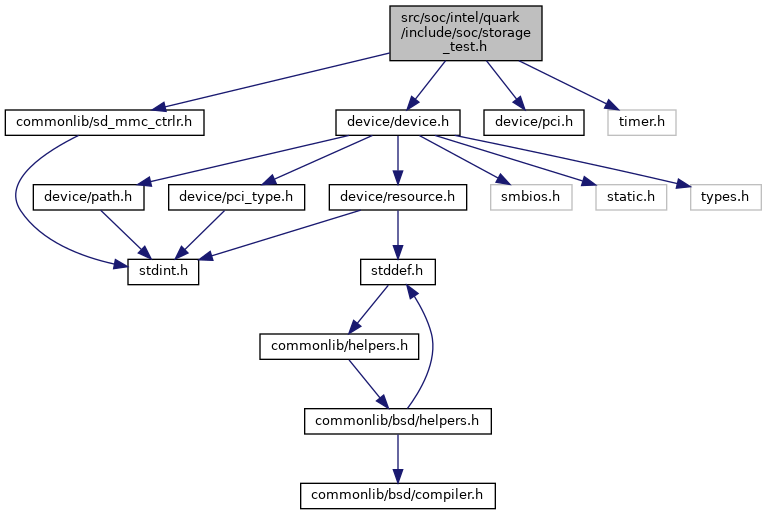

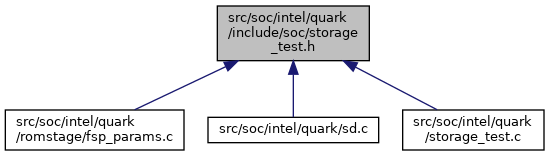

#include <commonlib/sd_mmc_ctrlr.h>#include <device/device.h>#include <device/pci.h>#include <timer.h>

Go to the source code of this file.

Data Structures | |

| struct | log_entry |

Macros | |

| #define | LOG_ENTRIES 256 |

Functions | |

| uint32_t | storage_test_init (struct device *dev, uint32_t *previous_bar, uint16_t *previous_command) |

| void | storage_test (uint32_t bar, int full_initialization) |

| void | storage_test_complete (struct device *dev, uint32_t previous_bar, uint16_t previous_command) |

| #define LOG_ENTRIES 256 |

Definition at line 35 of file storage_test.h.

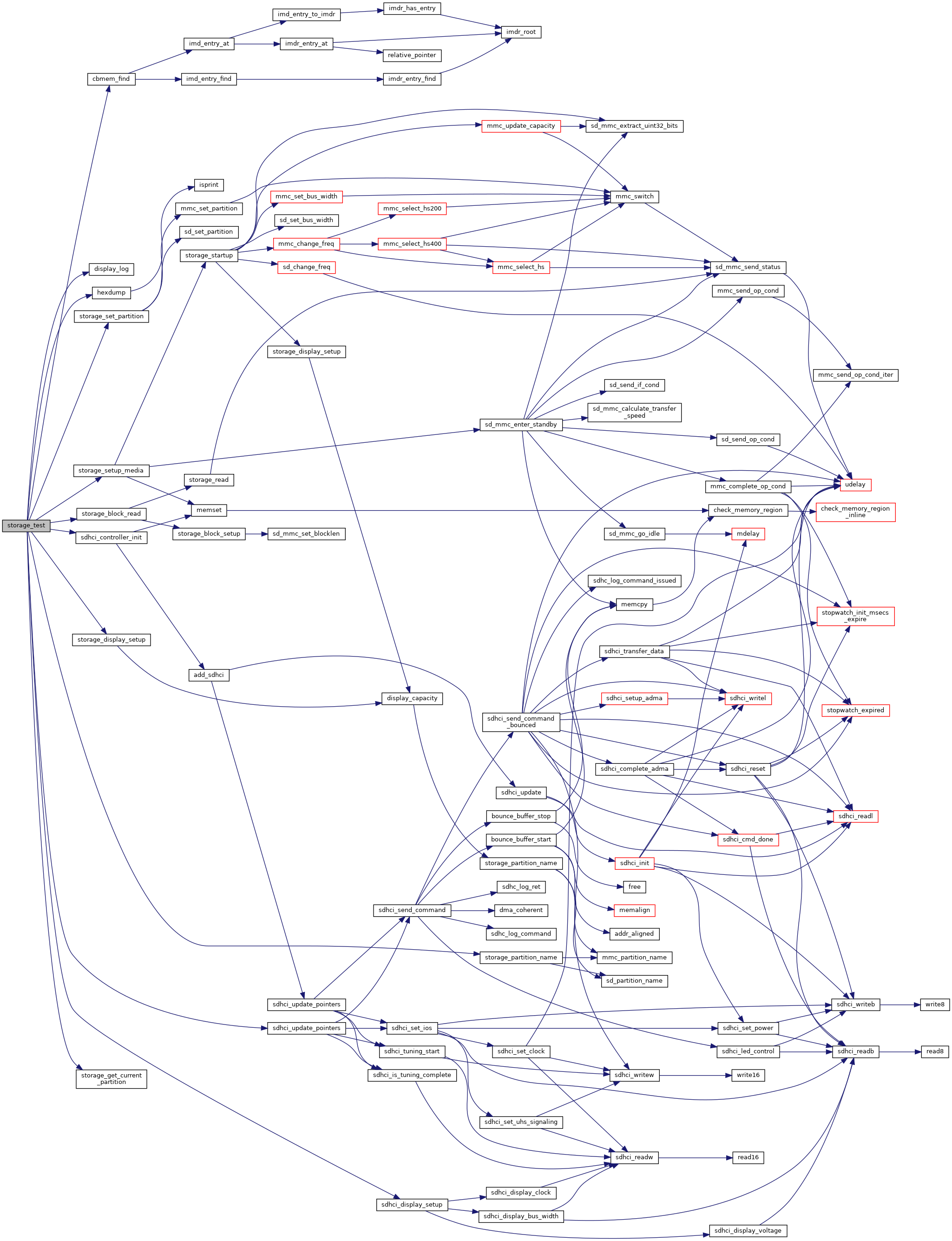

Definition at line 147 of file storage_test.c.

References ARRAY_SIZE, ASSERT, BIOS_ERR, buffer, storage_media::capacity, cbmem_find(), CBMEM_ID_STORAGE_DATA, CONFIG, storage_media::ctrlr, display_log(), drivers_storage, ENV_ROMSTAGE, hexdump(), sdhci_ctrlr::ioaddr, LOG_DEBUG, media, name, NULL, printk, sdhci_ctrlr::sd_mmc_ctrlr, sdhci_controller_init(), sdhci_display_setup(), sdhci_update_pointers(), storage_block_read(), STORAGE_DEBUG, storage_display_setup(), storage_get_current_partition(), storage_partition_name(), storage_set_partition(), and storage_setup_media().

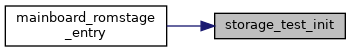

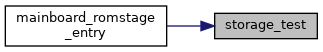

Referenced by mainboard_romstage_entry().

| void storage_test_complete | ( | struct device * | dev, |

| uint32_t | previous_bar, | ||

| uint16_t | previous_command | ||

| ) |

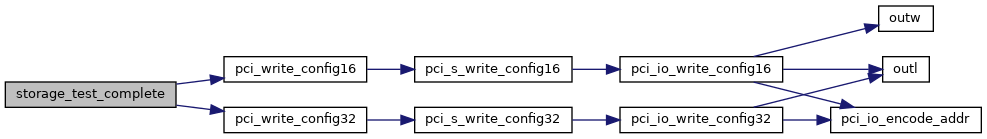

Definition at line 65 of file storage_test.c.

References PCI_BASE_ADDRESS_0, PCI_COMMAND, pci_write_config16(), and pci_write_config32().

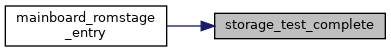

Referenced by mainboard_romstage_entry().

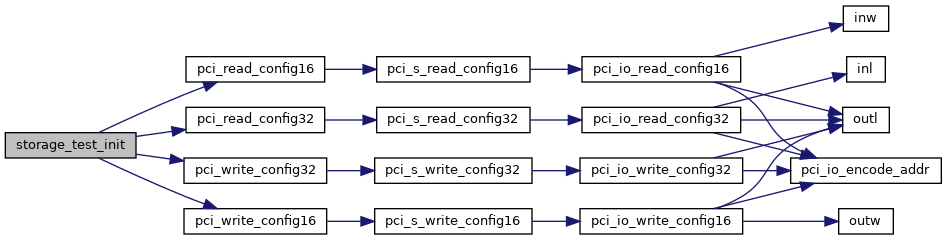

| uint32_t storage_test_init | ( | struct device * | dev, |

| uint32_t * | previous_bar, | ||

| uint16_t * | previous_command | ||

| ) |

Definition at line 32 of file storage_test.c.

References LOG_DEBUG, PCI_BASE_ADDRESS_0, PCI_BASE_ADDRESS_MEM_ATTR_MASK, PCI_COMMAND, PCI_COMMAND_MEMORY, PCI_DEVICE_ID, pci_read_config16(), pci_read_config32(), PCI_VENDOR_ID, pci_write_config16(), pci_write_config32(), printk, and SD_BASE_ADDRESS.

Referenced by mainboard_romstage_entry().