|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

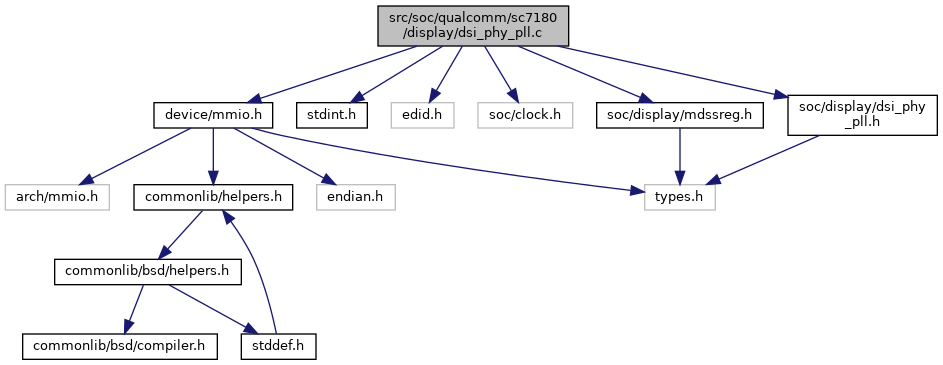

#include <device/mmio.h>#include <stdint.h>#include <edid.h>#include <soc/clock.h>#include <soc/display/mdssreg.h>#include <soc/display/dsi_phy_pll.h>

Go to the source code of this file.

Data Structures | |

| struct | dsi_pll_regs |

Macros | |

| #define | VCO_DELAY_USEC 1 |

| #define | SSC_CENTER BIT(0) |

| #define | SSC_EN BIT(1) |

Functions | |

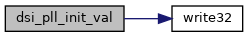

| static void | dsi_pll_init_val (void) |

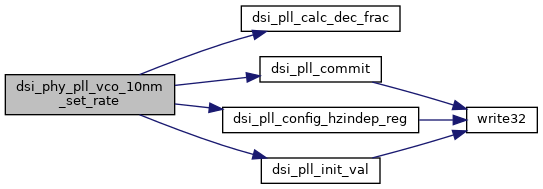

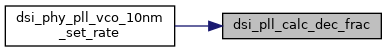

| static void | dsi_pll_calc_dec_frac (struct dsi_pll_regs *regs, unsigned long rate) |

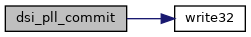

| static void | dsi_pll_commit (struct dsi_pll_regs *reg) |

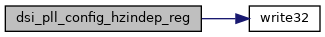

| static void | dsi_pll_config_hzindep_reg (struct dsi_pll_regs *reg) |

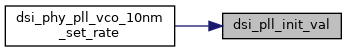

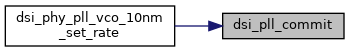

| void | dsi_phy_pll_vco_10nm_set_rate (unsigned long rate) |

| #define SSC_CENTER BIT(0) |

Definition at line 13 of file dsi_phy_pll.c.

| #define SSC_EN BIT(1) |

Definition at line 14 of file dsi_phy_pll.c.

| #define VCO_DELAY_USEC 1 |

Definition at line 10 of file dsi_phy_pll.c.

Definition at line 137 of file dsi_phy_pll.c.

References dsi_pll_calc_dec_frac(), dsi_pll_commit(), dsi_pll_config_hzindep_reg(), and dsi_pll_init_val().

|

static |

Definition at line 66 of file dsi_phy_pll.c.

References MHz, and SRC_XO_HZ.

Referenced by dsi_phy_pll_vco_10nm_set_rate().

|

static |

Definition at line 102 of file dsi_phy_pll.c.

References dsi_pll_regs::decimal_div_start, dsi_pll_regs::frac_div_start_high, dsi_pll_regs::frac_div_start_low, dsi_pll_regs::frac_div_start_mid, phy_pll_qlink, dsi_pll_regs::pll_clock_inverters, dsi_phy_pll_qlink_regs::pll_clock_inverters, dsi_phy_pll_qlink_regs::pll_cmode, dsi_phy_pll_qlink_regs::pll_core_input_override, dsi_phy_pll_qlink_regs::pll_decimal_div_start_1, dsi_phy_pll_qlink_regs::pll_frac_div_start_high1, dsi_phy_pll_qlink_regs::pll_frac_div_start_low1, dsi_phy_pll_qlink_regs::pll_frac_div_start_mid1, dsi_phy_pll_qlink_regs::pll_lock_delay, dsi_phy_pll_qlink_regs::pll_lockdet_rate, and write32().

Referenced by dsi_phy_pll_vco_10nm_set_rate().

|

static |

Definition at line 115 of file dsi_phy_pll.c.

References phy_pll_qlink, dsi_phy_pll_qlink_regs::pll_analog_ctrls_one, dsi_phy_pll_qlink_regs::pll_analog_ctrls_three, dsi_phy_pll_qlink_regs::pll_analog_ctrls_two, dsi_phy_pll_qlink_regs::pll_band_sel_cal_settings_three, dsi_phy_pll_qlink_regs::pll_band_set_rate, dsi_phy_pll_qlink_regs::pll_cal_settings, dsi_phy_pll_qlink_regs::pll_core_override, dsi_phy_pll_qlink_regs::pll_digital_timers_two, dsi_phy_pll_qlink_regs::pll_dsm_divider, dsi_phy_pll_qlink_regs::pll_feedback_divider, dsi_phy_pll_qlink_regs::pll_fl_int_gain_pfilt_band, dsi_phy_pll_qlink_regs::pll_freq_detect_settings_one, dsi_phy_pll_qlink_regs::pll_gain_ifilt_band, dsi_phy_pll_qlink_regs::pll_ifilt, dsi_phy_pll_qlink_regs::pll_lock_override, dsi_phy_pll_qlink_regs::pll_outdiv, dsi_phy_pll_qlink_regs::pll_pfilt, dsi_pll_regs::pll_prop_gain_rate, dsi_phy_pll_qlink_regs::pll_prop_gain_rate, and write32().

Referenced by dsi_phy_pll_vco_10nm_set_rate().

Definition at line 25 of file dsi_phy_pll.c.

References phy_pll_qlink, dsi_phy_pll_qlink_regs::pll_alog_obsv_bus_ctrl_1, dsi_phy_pll_qlink_regs::pll_analog_ctrls_four, dsi_phy_pll_qlink_regs::pll_band_sel_cal_settings, dsi_phy_pll_qlink_regs::pll_band_sel_cal_settings_four, dsi_phy_pll_qlink_regs::pll_band_sel_cal_settings_two, dsi_phy_pll_qlink_regs::pll_band_sel_cal_timer_high, dsi_phy_pll_qlink_regs::pll_band_sel_cal_timer_low, dsi_phy_pll_qlink_regs::pll_band_sel_icode_high, dsi_phy_pll_qlink_regs::pll_band_sel_icode_low, dsi_phy_pll_qlink_regs::pll_band_sel_ifilt, dsi_phy_pll_qlink_regs::pll_band_sel_max, dsi_phy_pll_qlink_regs::pll_band_sel_min, dsi_phy_pll_qlink_regs::pll_band_sel_pfilt, dsi_phy_pll_qlink_regs::pll_bias_ctrl_1, dsi_phy_pll_qlink_regs::pll_bias_ctrl_2, dsi_phy_pll_qlink_regs::pll_core_input_override, dsi_phy_pll_qlink_regs::pll_dec_frac_muxes, dsi_phy_pll_qlink_regs::pll_digital_timers, dsi_phy_pll_qlink_regs::pll_fastlock_ctrl, dsi_phy_pll_qlink_regs::pll_freq_tune_accum_init_mux, dsi_phy_pll_qlink_regs::pll_freq_update_ctrl_overrides, dsi_phy_pll_qlink_regs::pll_icode_high, dsi_phy_pll_qlink_regs::pll_icode_low, dsi_phy_pll_qlink_regs::pll_int_loop_ctrls, dsi_phy_pll_qlink_regs::pll_int_loop_settings, dsi_phy_pll_qlink_regs::pll_int_loop_settings_two, dsi_phy_pll_qlink_regs::pll_lock_min_delay, dsi_phy_pll_qlink_regs::pll_lockdet, dsi_phy_pll_qlink_regs::pll_mash_ctrl, dsi_phy_pll_qlink_regs::pll_pass_out_override_one, dsi_phy_pll_qlink_regs::pll_pass_out_override_two, dsi_phy_pll_qlink_regs::pll_pll_fastlock_en_band, dsi_phy_pll_qlink_regs::pll_pll_gain, dsi_phy_pll_qlink_regs::pll_rate_change, dsi_phy_pll_qlink_regs::pll_spare_and_jpc_overrides, dsi_phy_pll_qlink_regs::pll_ssc_ctrl, dsi_phy_pll_qlink_regs::pll_ssc_mux_ctrl, and write32().

Referenced by dsi_phy_pll_vco_10nm_set_rate().