|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

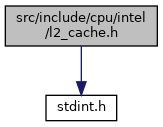

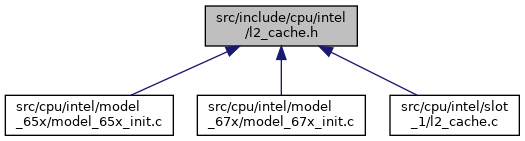

#include <stdint.h>

Go to the source code of this file.

Macros | |

| #define | EBL_CR_POWERON 0x2A |

| #define | BBL_CR_D0 0x88 |

| #define | BBL_CR_D1 0x89 |

| #define | BBL_CR_D2 0x8A |

| #define | BBL_CR_D3 0x8B |

| #define | BBL_CR_ADDR 0x116 |

| #define | BBL_CR_DECC 0x118 |

| #define | BBL_CR_CTL 0x119 |

| #define | BBL_CR_TRIG 0x11A |

| #define | BBL_CR_BUSY 0x11B |

| #define | BBL_CR_CTL3 0x11E |

| #define | BBLCR3_L2_CONFIGURED (1<<0) |

| #define | BBLCR3_L2_LATENCY 0x1e |

| #define | BBLCR3_L2_ECC_CHECK_ENABLE (1<<5) |

| #define | BBLCR3_L2_ADDR_PARITY_ENABLE (1<<6) |

| #define | BBLCR3_L2_CRTN_PARITY_ENABLE (1<<7) |

| #define | BBLCR3_L2_ENABLED (1<<8) |

| #define | BBLCR3_L2_SIZE (0x1f << 13) |

| #define | BBLCR3_L2_SIZE_256K (0x01 << 13) |

| #define | BBLCR3_L2_SIZE_512K (0x02 << 13) |

| #define | BBLCR3_L2_SIZE_1M (0x04 << 13) |

| #define | BBLCR3_L2_SIZE_2M (0x08 << 13) |

| #define | BBLCR3_L2_SIZE_4M (0x10 << 13) |

| #define | BBLCR3_L2_PHYSICAL_RANGE (0x7 << 20); |

| #define | BBLCR3_L2_SUPPLIED_ECC 0x40000 |

| #define | BBLCR3_L2_HARDWARE_DISABLE (1<<23) |

| #define | BBLCR3_L2_NOT_PRESENT (1<<23) |

| #define | L2CMD_RLU 0x0c /* 01100 Data read w/ LRU update */ |

| #define | L2CMD_TRR 0x0e /* 01110 Tag read with data read */ |

| #define | L2CMD_TI 0x0f /* 01111 Tag inquiry */ |

| #define | L2CMD_CR 0x02 /* 00010 L2 control register read */ |

| #define | L2CMD_CW 0x03 /* 00011 L2 control register write */ |

| #define | L2CMD_TWR 0x08 /* 010-- Tag read w/ data read */ |

| #define | L2CMD_TWW 0x1c /* 111-- Tag write w/ data write */ |

| #define | L2CMD_TW 0x10 /* 100-- Tag write */ |

| #define | L2CMD_MESI_M 3 |

| #define | L2CMD_MESI_E 2 |

| #define | L2CMD_MESI_S 1 |

| #define | L2CMD_MESI_I 0 |

Functions | |

| int | calculate_l2_latency (void) |

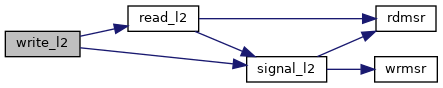

| int | signal_l2 (u32 address_low, u32 data_high, u32 data_low, int way, u8 command) |

| int | read_l2 (u32 address) |

| int | write_l2 (u32 address, u32 data) |

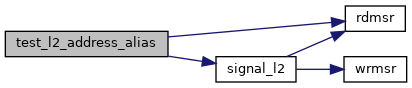

| int | test_l2_address_alias (u32 address1, u32 address2, u32 data_high, u32 data_low) |

| int | calculate_l2_cache_size (void) |

| int | calculate_l2_physical_address_range (void) |

| int | set_l2_ecc (void) |

| int | p6_configure_l2_cache (void) |

| #define BBL_CR_ADDR 0x116 |

Definition at line 25 of file l2_cache.h.

| #define BBL_CR_BUSY 0x11B |

Definition at line 29 of file l2_cache.h.

| #define BBL_CR_CTL 0x119 |

Definition at line 27 of file l2_cache.h.

| #define BBL_CR_CTL3 0x11E |

Definition at line 30 of file l2_cache.h.

| #define BBL_CR_D0 0x88 |

Definition at line 20 of file l2_cache.h.

| #define BBL_CR_D1 0x89 |

Definition at line 21 of file l2_cache.h.

| #define BBL_CR_D2 0x8A |

Definition at line 22 of file l2_cache.h.

| #define BBL_CR_D3 0x8B |

Definition at line 23 of file l2_cache.h.

| #define BBL_CR_DECC 0x118 |

Definition at line 26 of file l2_cache.h.

| #define BBL_CR_TRIG 0x11A |

Definition at line 28 of file l2_cache.h.

| #define BBLCR3_L2_ADDR_PARITY_ENABLE (1<<6) |

Definition at line 36 of file l2_cache.h.

| #define BBLCR3_L2_CONFIGURED (1<<0) |

Definition at line 32 of file l2_cache.h.

| #define BBLCR3_L2_CRTN_PARITY_ENABLE (1<<7) |

Definition at line 37 of file l2_cache.h.

| #define BBLCR3_L2_ECC_CHECK_ENABLE (1<<5) |

Definition at line 35 of file l2_cache.h.

| #define BBLCR3_L2_ENABLED (1<<8) |

Definition at line 38 of file l2_cache.h.

| #define BBLCR3_L2_HARDWARE_DISABLE (1<<23) |

Definition at line 53 of file l2_cache.h.

| #define BBLCR3_L2_LATENCY 0x1e |

Definition at line 34 of file l2_cache.h.

| #define BBLCR3_L2_NOT_PRESENT (1<<23) |

Definition at line 55 of file l2_cache.h.

| #define BBLCR3_L2_PHYSICAL_RANGE (0x7 << 20); |

Definition at line 47 of file l2_cache.h.

| #define BBLCR3_L2_SIZE (0x1f << 13) |

Definition at line 40 of file l2_cache.h.

| #define BBLCR3_L2_SIZE_1M (0x04 << 13) |

Definition at line 43 of file l2_cache.h.

| #define BBLCR3_L2_SIZE_256K (0x01 << 13) |

Definition at line 41 of file l2_cache.h.

| #define BBLCR3_L2_SIZE_2M (0x08 << 13) |

Definition at line 44 of file l2_cache.h.

| #define BBLCR3_L2_SIZE_4M (0x10 << 13) |

Definition at line 45 of file l2_cache.h.

| #define BBLCR3_L2_SIZE_512K (0x02 << 13) |

Definition at line 42 of file l2_cache.h.

| #define BBLCR3_L2_SUPPLIED_ECC 0x40000 |

Definition at line 51 of file l2_cache.h.

| #define EBL_CR_POWERON 0x2A |

Definition at line 18 of file l2_cache.h.

| #define L2CMD_CR 0x02 /* 00010 L2 control register read */ |

Definition at line 61 of file l2_cache.h.

| #define L2CMD_CW 0x03 /* 00011 L2 control register write */ |

Definition at line 62 of file l2_cache.h.

| #define L2CMD_MESI_E 2 |

Definition at line 68 of file l2_cache.h.

| #define L2CMD_MESI_I 0 |

Definition at line 70 of file l2_cache.h.

| #define L2CMD_MESI_M 3 |

Definition at line 67 of file l2_cache.h.

| #define L2CMD_MESI_S 1 |

Definition at line 69 of file l2_cache.h.

| #define L2CMD_RLU 0x0c /* 01100 Data read w/ LRU update */ |

Definition at line 58 of file l2_cache.h.

| #define L2CMD_TI 0x0f /* 01111 Tag inquiry */ |

Definition at line 60 of file l2_cache.h.

| #define L2CMD_TRR 0x0e /* 01110 Tag read with data read */ |

Definition at line 59 of file l2_cache.h.

| #define L2CMD_TW 0x10 /* 100-- Tag write */ |

Definition at line 65 of file l2_cache.h.

| #define L2CMD_TWR 0x08 /* 010-- Tag read w/ data read */ |

Definition at line 63 of file l2_cache.h.

| #define L2CMD_TWW 0x1c /* 111-- Tag write w/ data write */ |

Definition at line 64 of file l2_cache.h.

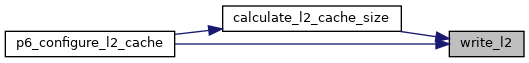

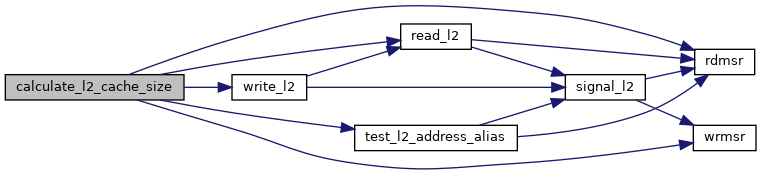

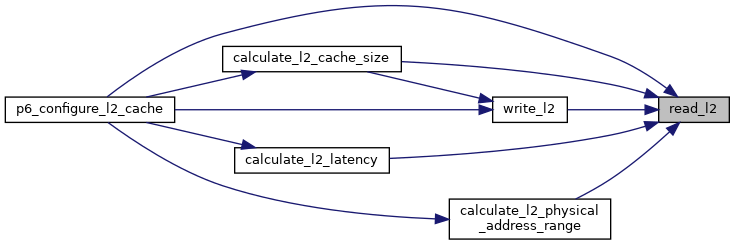

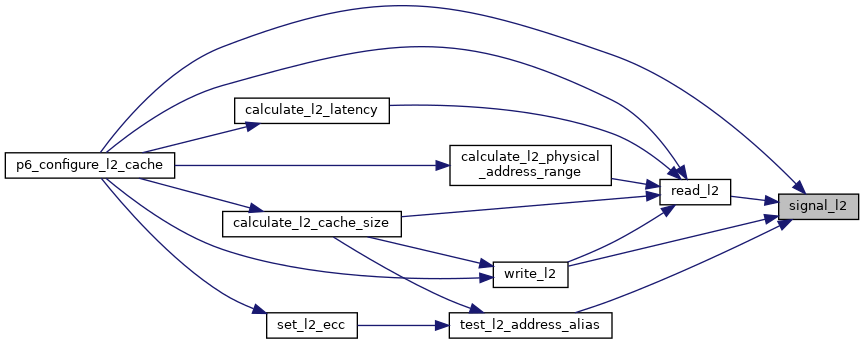

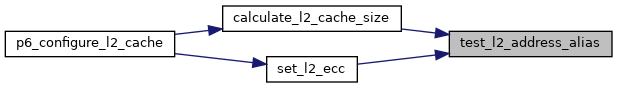

| int calculate_l2_cache_size | ( | void | ) |

Definition at line 332 of file l2_cache.c.

References address, BBL_CR_CTL3, BBLCR3_L2_SIZE, BBLCR3_L2_SIZE_256K, BBLCR3_L2_SIZE_4M, BIOS_DEBUG, c, msr_struct::lo, printk, rdmsr(), read_l2(), test_l2_address_alias(), write_l2(), and wrmsr().

Referenced by p6_configure_l2_cache().

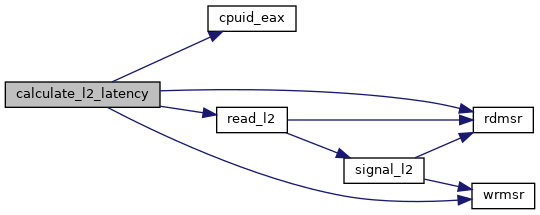

| int calculate_l2_latency | ( | void | ) |

Definition at line 108 of file l2_cache.c.

References BBL_CR_CTL3, BIOS_DEBUG, cpuid_eax(), EBL_CR_POWERON, msr_struct::hi, IA32_PLATFORM_ID, latency_entry::key, latency_650, latency_670, msr_struct::lo, printk, rdmsr(), read_l2(), latency_entry::value, and wrmsr().

Referenced by p6_configure_l2_cache().

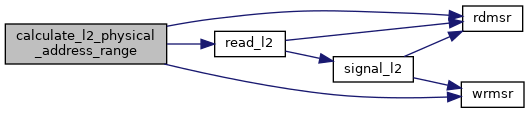

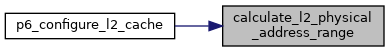

| int calculate_l2_physical_address_range | ( | void | ) |

Definition at line 487 of file l2_cache.c.

References BBL_CR_CTL3, BBLCR3_L2_PHYSICAL_RANGE, BIOS_DEBUG, msr_struct::lo, printk, rdmsr(), read_l2(), and wrmsr().

Referenced by p6_configure_l2_cache().

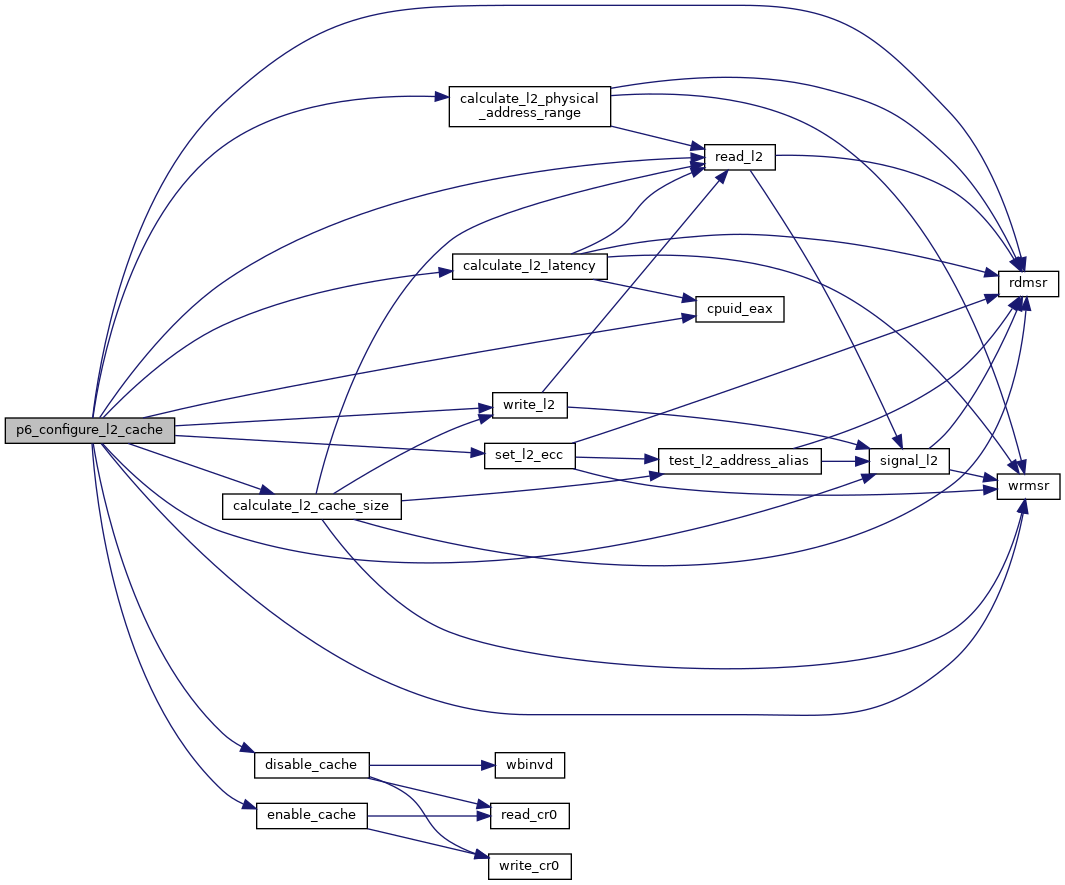

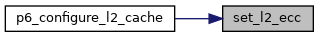

| int p6_configure_l2_cache | ( | void | ) |

Definition at line 565 of file l2_cache.c.

References BBL_CR_CTL3, BBLCR3_L2_ADDR_PARITY_ENABLE, BBLCR3_L2_CONFIGURED, BBLCR3_L2_CRTN_PARITY_ENABLE, BBLCR3_L2_ENABLED, BBLCR3_L2_LATENCY, BBLCR3_L2_NOT_PRESENT, BBLCR3_L2_SIZE, BIOS_DEBUG, BIOS_ERR, BIOS_INFO, calculate_l2_cache_size(), calculate_l2_latency(), calculate_l2_physical_address_range(), cpuid_eax(), disable_cache(), EBL_CR_POWERON, enable_cache(), L2CMD_MESI_I, L2CMD_TWW, msr_struct::lo, printk, rdmsr(), read_l2(), set_l2_ecc(), signal_l2(), write_l2(), and wrmsr().

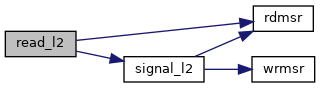

| int read_l2 | ( | u32 | address | ) |

Definition at line 236 of file l2_cache.c.

References address, BBL_CR_ADDR, L2CMD_CR, msr_struct::lo, rdmsr(), and signal_l2().

Referenced by calculate_l2_cache_size(), calculate_l2_latency(), calculate_l2_physical_address_range(), p6_configure_l2_cache(), and write_l2().

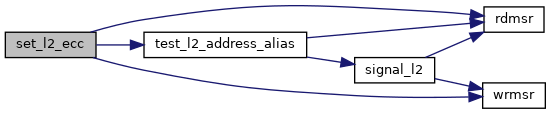

| int set_l2_ecc | ( | void | ) |

Definition at line 519 of file l2_cache.c.

References BBL_CR_CTL, BBL_CR_CTL3, BBL_CR_DECC, BBLCR3_L2_ECC_CHECK_ENABLE, BBLCR3_L2_SUPPLIED_ECC, BIOS_DEBUG, msr_struct::hi, msr_struct::lo, printk, rdmsr(), test_l2_address_alias(), and wrmsr().

Referenced by p6_configure_l2_cache().

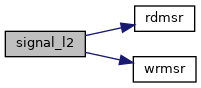

Definition at line 196 of file l2_cache.c.

References address, BBL_CR_ADDR, BBL_CR_BUSY, BBL_CR_CTL, BBL_CR_D0, BBL_CR_D3, BBL_CR_TRIG, msr_struct::hi, msr_struct::lo, rdmsr(), and wrmsr().

Referenced by p6_configure_l2_cache(), read_l2(), test_l2_address_alias(), and write_l2().

Definition at line 301 of file l2_cache.c.

References BBL_CR_D0, BBL_CR_D3, msr_struct::hi, L2CMD_TRR, L2CMD_TWW, msr_struct::lo, rdmsr(), and signal_l2().

Referenced by calculate_l2_cache_size(), and set_l2_ecc().

Definition at line 251 of file l2_cache.c.

References address, read_l2(), and signal_l2().

Referenced by calculate_l2_cache_size(), and p6_configure_l2_cache().