|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

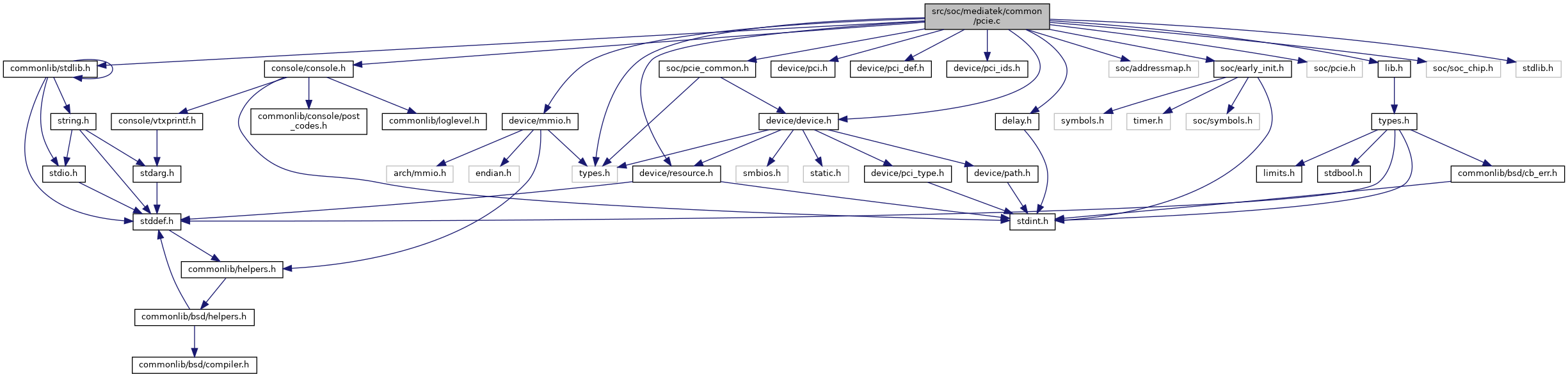

#include <commonlib/stdlib.h>#include <console/console.h>#include <device/device.h>#include <device/mmio.h>#include <device/pci.h>#include <device/pci_def.h>#include <device/pci_ids.h>#include <device/resource.h>#include <delay.h>#include <lib.h>#include <soc/addressmap.h>#include <soc/early_init.h>#include <soc/pcie.h>#include <soc/pcie_common.h>#include <soc/soc_chip.h>#include <stdlib.h>#include <types.h>

Go to the source code of this file.

Functions | |

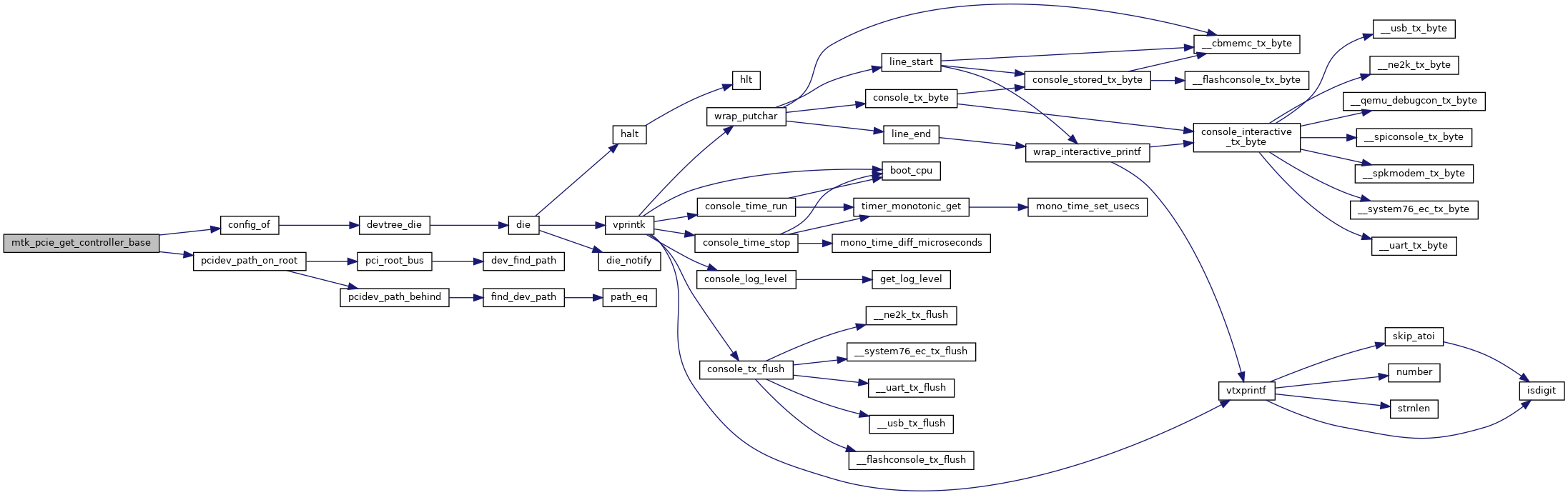

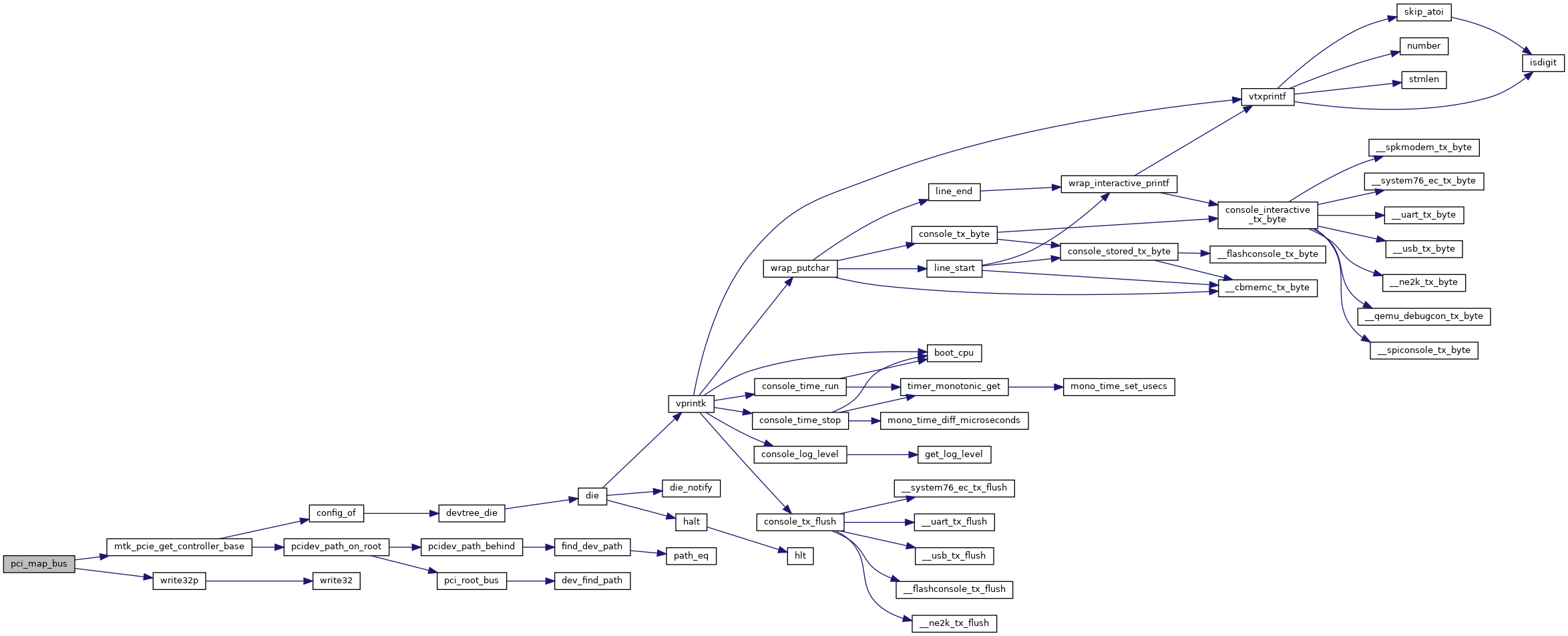

| static uintptr_t | mtk_pcie_get_controller_base (pci_devfn_t devfn) |

| volatile union pci_bank * | pci_map_bus (pci_devfn_t dev) |

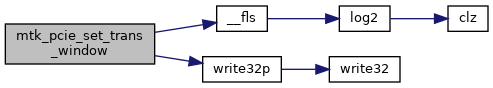

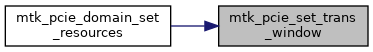

| static int | mtk_pcie_set_trans_window (struct device *dev, uintptr_t table, const struct mtk_pcie_mmio_res *mmio_res) |

| static void | mtk_pcie_domain_new_res (struct device *dev, unsigned int index, const struct mtk_pcie_mmio_res *mmio_res) |

| void | mtk_pcie_domain_read_resources (struct device *dev) |

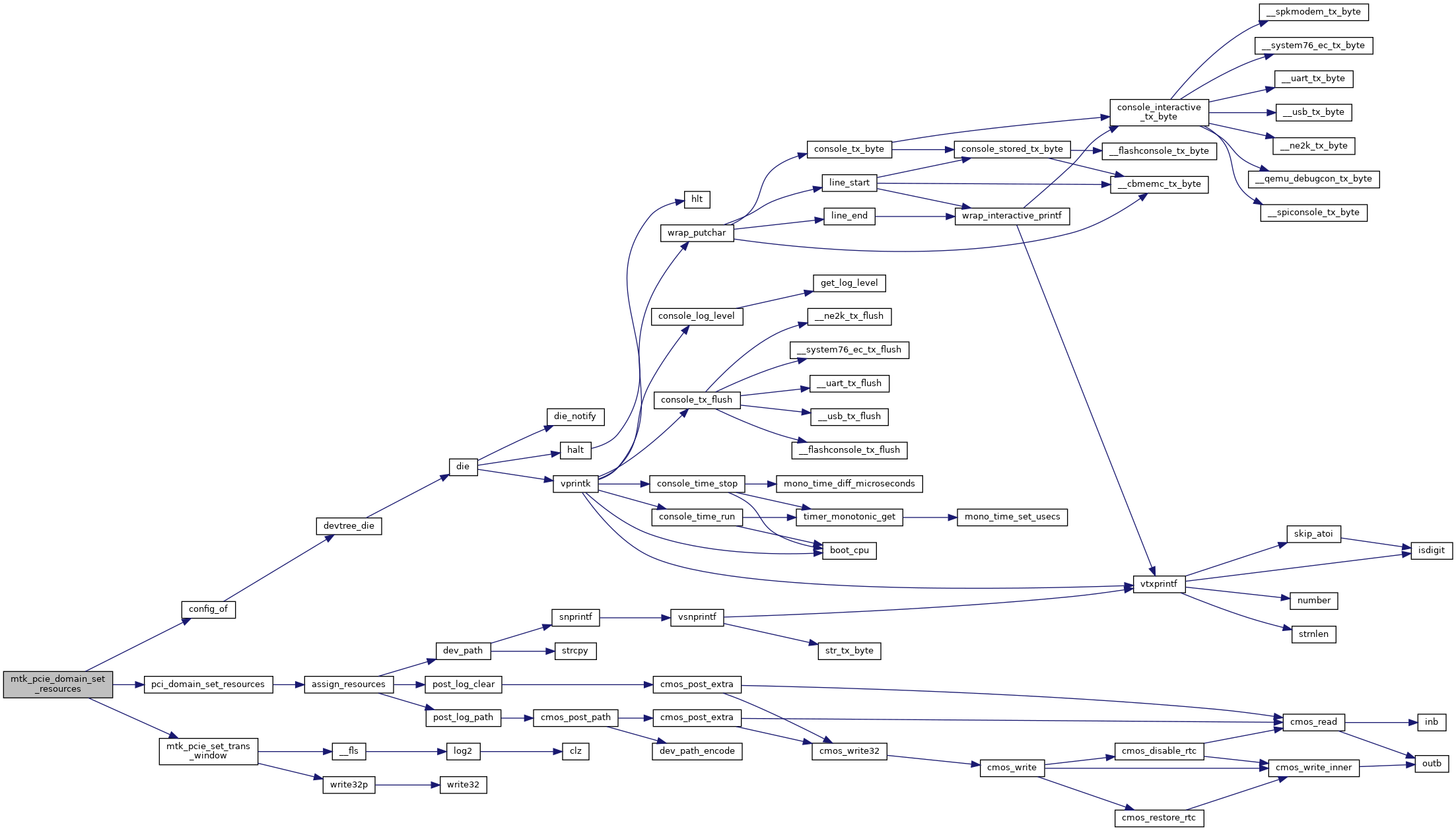

| void | mtk_pcie_domain_set_resources (struct device *dev) |

| void | mtk_pcie_domain_enable (struct device *dev) |

Variables | |

| static const char *const | ltssm_str [] |

| #define PCIE_ATR_SIZE | ( | size | ) | (((((size) - 1) << 1) & GENMASK(6, 1)) | PCIE_ATR_EN) |

| #define PCIE_ATR_TLP_TYPE_IO PCIE_ATR_TLP_TYPE(2) |

| #define PCIE_ATR_TLP_TYPE_MEM PCIE_ATR_TLP_TYPE(0) |

| #define PCIE_ATR_TYPE_IO PCIE_ATR_ID(1) |

| #define PCIE_ATR_TYPE_MEM PCIE_ATR_ID(0) |

| #define PCIE_CFG_HEADER | ( | bus, | |

| devfn | |||

| ) | (PCIE_CFG_BUS(bus) | PCIE_CFG_DEVFN(devfn)) |

| #define PCIE_INTX_ENABLE GENMASK(PCIE_INTX_SHIFT + PCI_NUM_INTX - 1, PCIE_INTX_SHIFT) |

Definition at line 213 of file pcie.c.

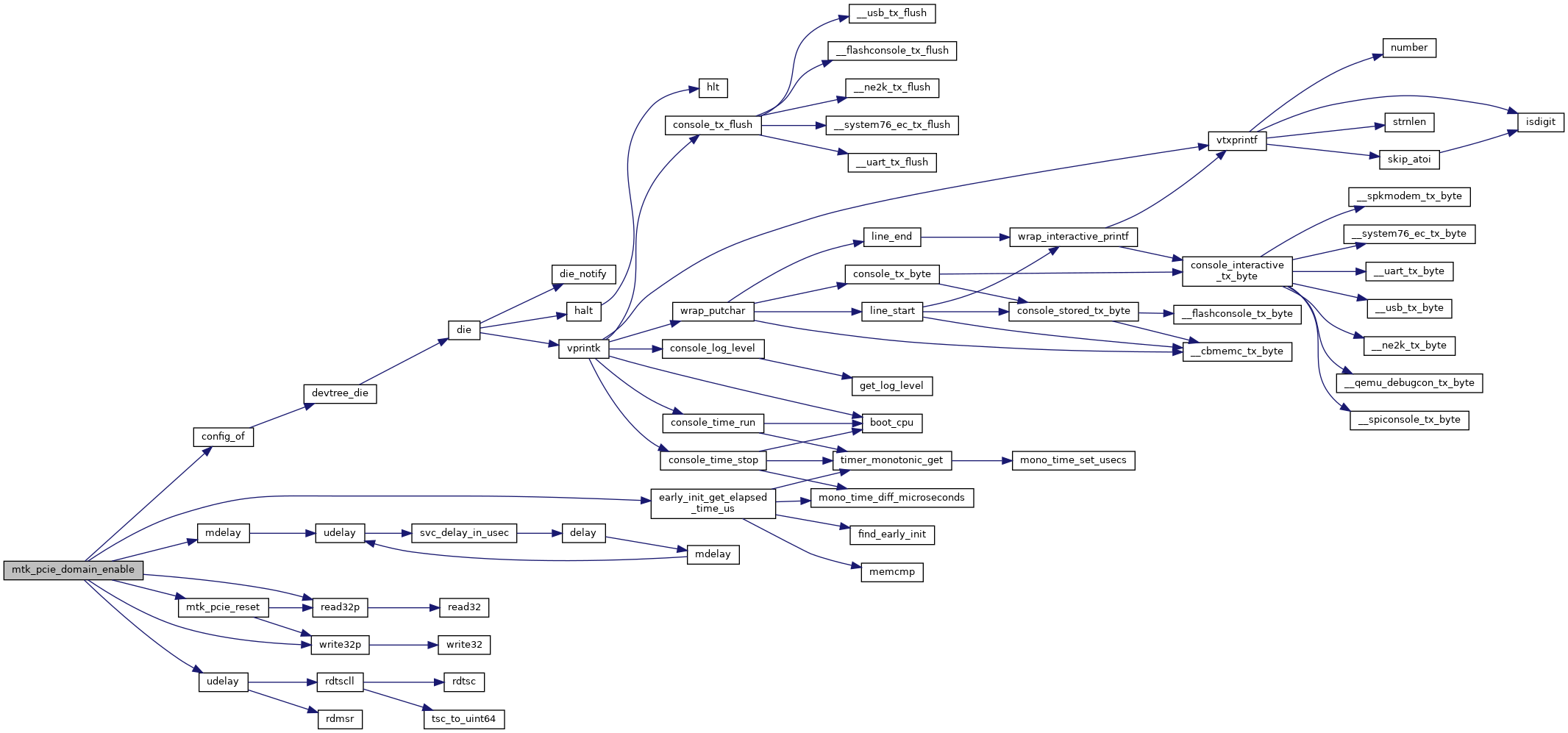

References ARRAY_SIZE, mtk_pcie_config::base, BIOS_DEBUG, BIOS_ERR, BIOS_INFO, BIOS_WARNING, config, config_of(), early_init_get_elapsed_time_us(), EARLY_INIT_PCIE, GENMASK, ltssm_str, mdelay(), mtk_pcie_reset(), PCI_CLASS, PCI_CLASS_BRIDGE_PCI, PCIE_CTRL_LINKUP, PCIE_INT_ENABLE_REG, PCIE_INTX_ENABLE, PCIE_LINK_STATUS_REG, PCIE_LTSSM_STATE, PCIE_LTSSM_STATUS_REG, PCIE_PCI_IDS_1, PCIE_RC_MODE, PCIE_RST_CTRL_REG, PCIE_SETTING_REG, printk, read32p(), retry, udelay(), val, and write32p().

|

static |

Definition at line 166 of file pcie.c.

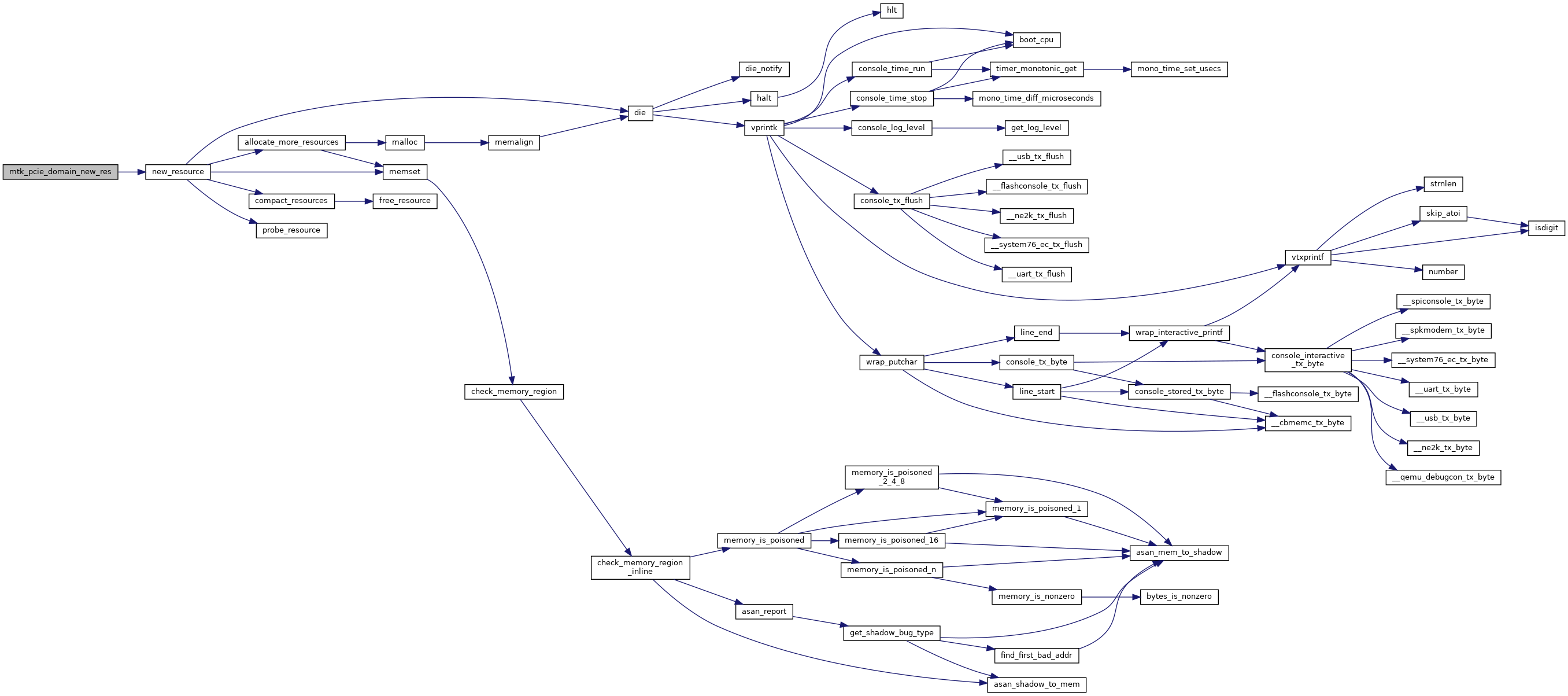

References resource::base, resource::flags, resource::index, IORESOURCE_ASSIGNED, IORESOURCE_SUBTRACTIVE, resource::limit, mmio_res, new_resource(), and resource::size.

Referenced by mtk_pcie_domain_read_resources().

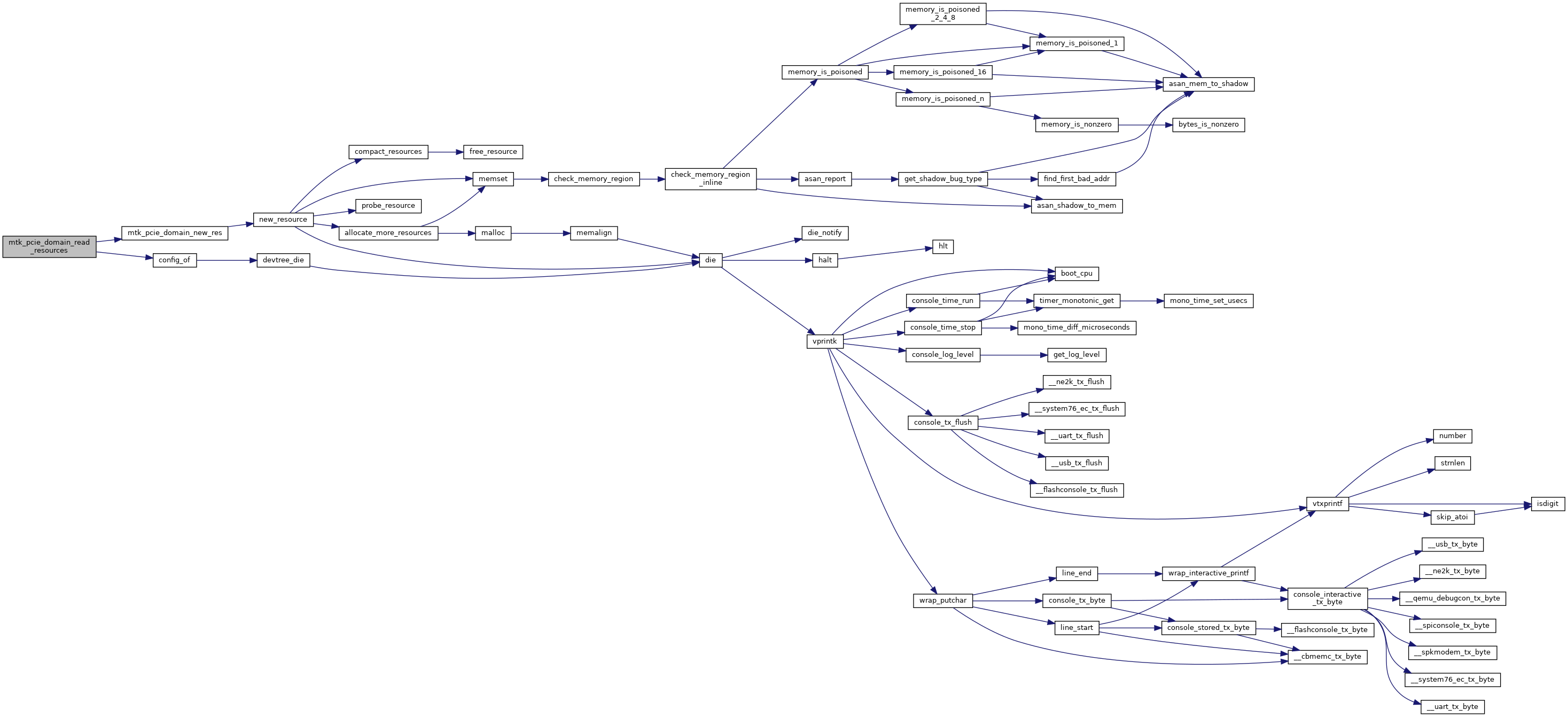

Definition at line 181 of file pcie.c.

References config, config_of(), IOINDEX_SUBTRACTIVE, mtk_pcie_config::mmio_res_io, mtk_pcie_config::mmio_res_mem, and mtk_pcie_domain_new_res().

Definition at line 193 of file pcie.c.

References mtk_pcie_config::base, BIOS_ERR, config, config_of(), mtk_pcie_config::mmio_res_io, mtk_pcie_config::mmio_res_mem, mtk_pcie_set_trans_window(), pci_domain_set_resources(), PCIE_ATR_TLB_SET_OFFSET, PCIE_TRANS_TABLE_BASE_REG, and printk.

|

static |

Definition at line 100 of file pcie.c.

References base, config, config_of(), and pcidev_path_on_root().

Referenced by pci_map_bus().

|

static |

Definition at line 130 of file pcie.c.

References __fls(), BIOS_ERR, BIOS_INFO, IORESOURCE_IO, IORESOURCE_MEM, mmio_res, PCIE_ATR_SIZE, PCIE_ATR_SRC_ADDR_MSB_OFFSET, PCIE_ATR_TLP_TYPE_IO, PCIE_ATR_TLP_TYPE_MEM, PCIE_ATR_TRSL_ADDR_LSB_OFFSET, PCIE_ATR_TRSL_ADDR_MSB_OFFSET, PCIE_ATR_TRSL_PARAM_OFFSET, PCIE_ATR_TYPE_IO, PCIE_ATR_TYPE_MEM, printk, resource::size, and write32p().

Referenced by mtk_pcie_domain_set_resources().

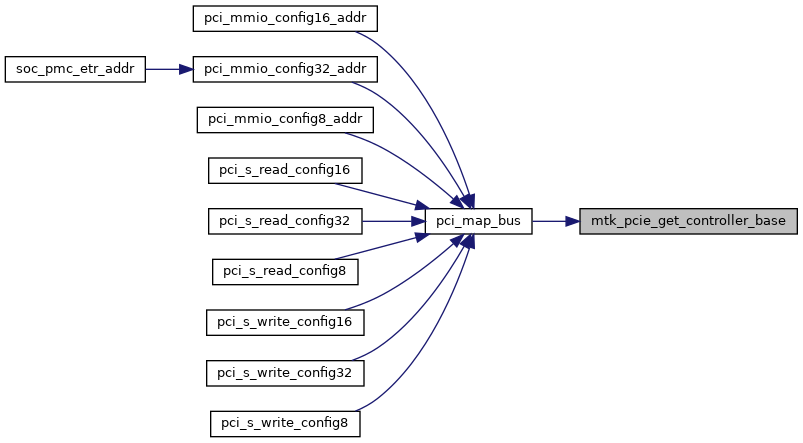

| volatile union pci_bank* pci_map_bus | ( | pci_devfn_t | dev | ) |

Definition at line 115 of file pcie.c.

References base, mtk_pcie_get_controller_base(), PCI_DEV2DEVFN, PCI_DEV2SEGBUS, PCIE_CFG_HEADER, PCIE_CFG_OFFSET_ADDR, PCIE_CFGNUM_REG, val, and write32p().

Referenced by pci_mmio_config16_addr(), pci_mmio_config32_addr(), pci_mmio_config8_addr(), pci_s_read_config16(), pci_s_read_config32(), pci_s_read_config8(), pci_s_write_config16(), pci_s_write_config32(), and pci_s_write_config8().

|

static |

Definition at line 70 of file pcie.c.

Referenced by mtk_pcie_domain_enable().