|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

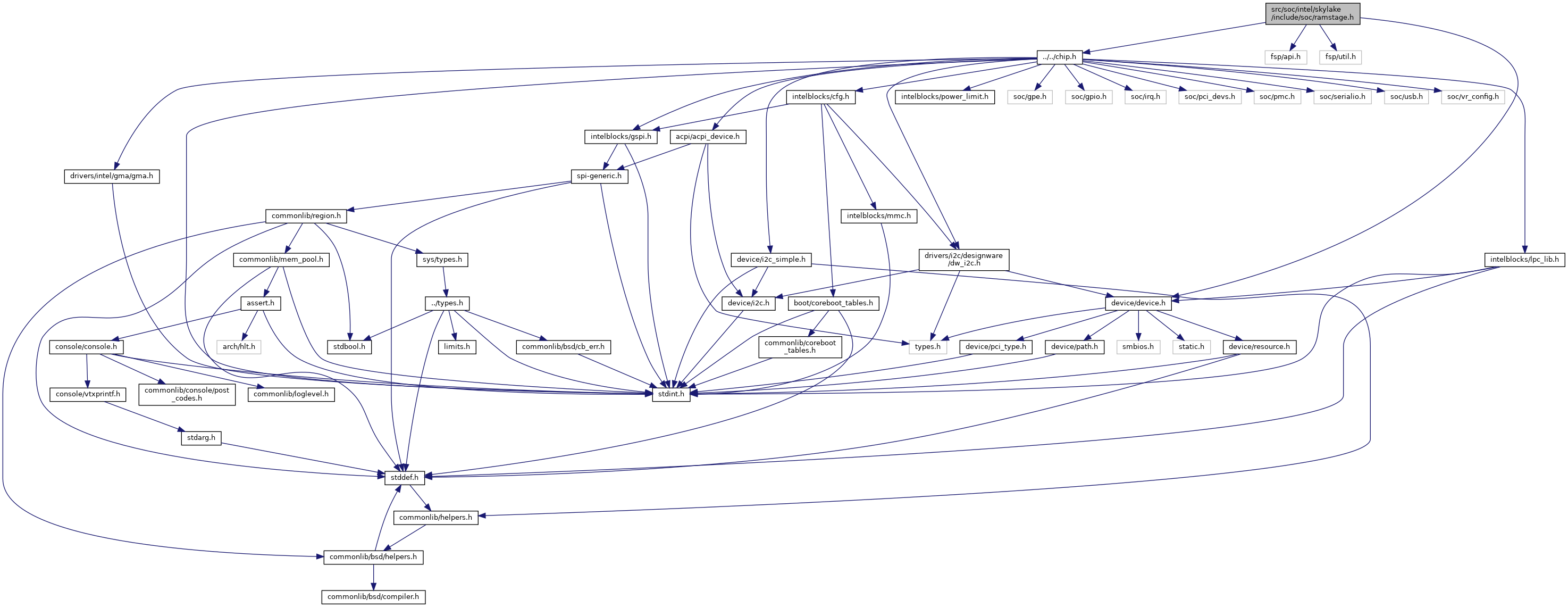

Go to the source code of this file.

Macros | |

| #define | FSP_SIL_UPD FSP_S_CONFIG |

| #define | FSP_MEM_UPD FSP_M_CONFIG |

Functions | |

| void | mainboard_silicon_init_params (FSP_S_CONFIG *params) |

| void | soc_init_pre_device (void *chip_info) |

| void | soc_irq_settings (FSP_SIL_UPD *params) |

| #define FSP_MEM_UPD FSP_M_CONFIG |

Definition at line 13 of file ramstage.h.

| #define FSP_SIL_UPD FSP_S_CONFIG |

Definition at line 12 of file ramstage.h.

| void mainboard_silicon_init_params | ( | FSP_S_CONFIG * | params | ) |

Definition at line 8 of file ramstage.c.

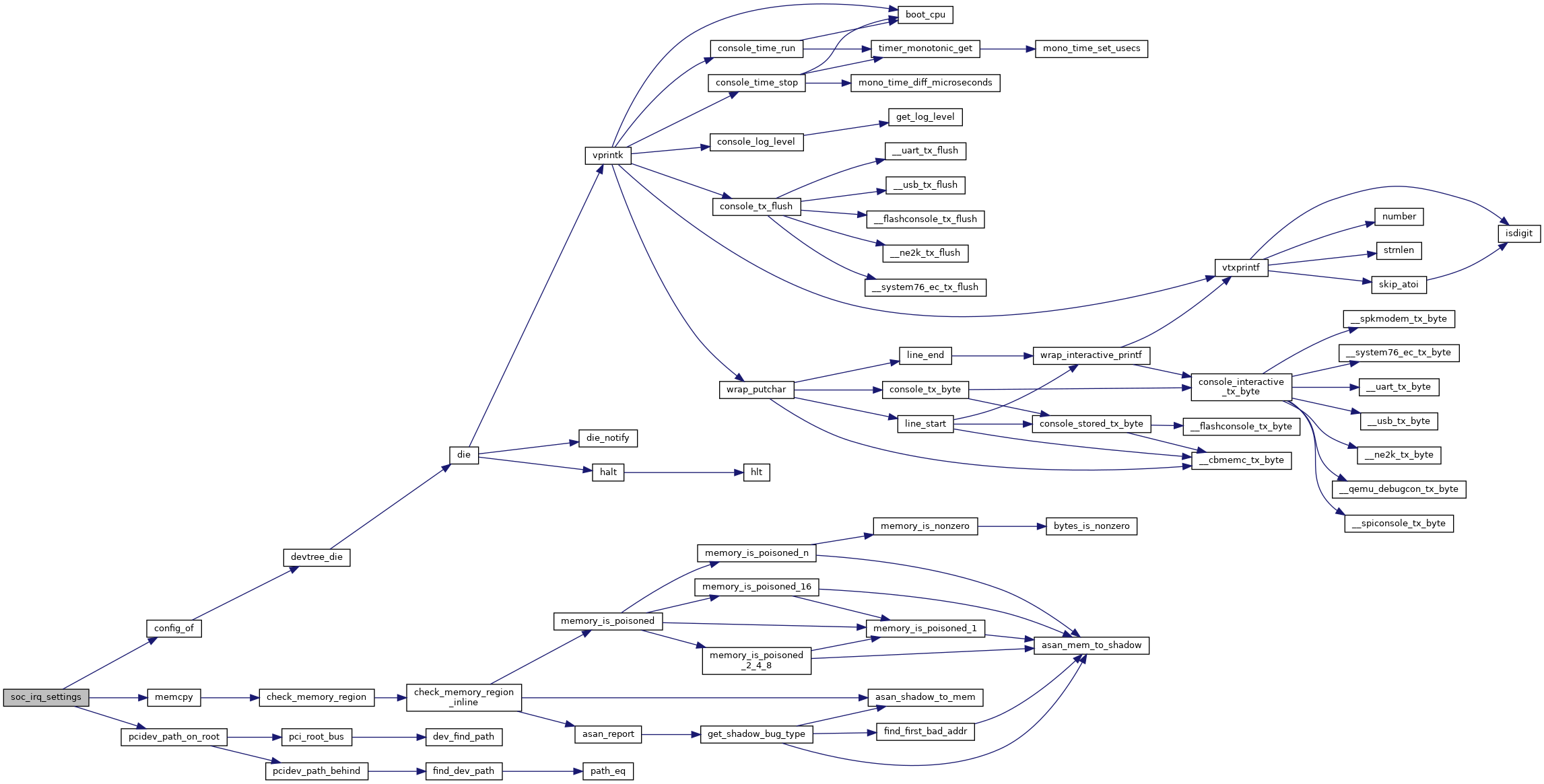

| void soc_irq_settings | ( | FSP_SIL_UPD * | params | ) |

Definition at line 166 of file irq.c.

References ARRAY_SIZE, config, config_of(), devintconfig, GPIO_IRQ14, memcpy(), params, PCH_DEVFN_LPC, PCH_IRQ10, PCH_IRQ11, PCH_MAX_IRQ_CONFIG, PCH_PARC, PCH_PBRC, PCH_PCRC, PCH_PDRC, PCH_PERC, PCH_PFRC, PCH_PGRC, PCH_PHRC, pcidev_path_on_root(), SCI_IRQ9, and TCO_IRQ9.

Referenced by platform_fsp_silicon_init_params_cb().