|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

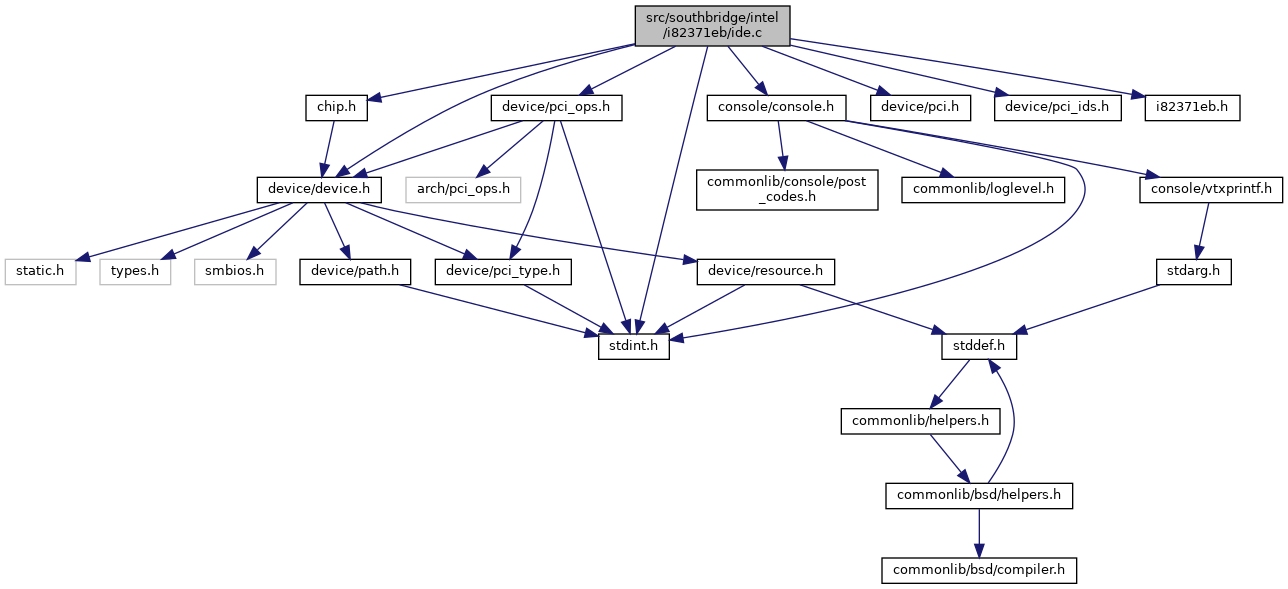

#include <stdint.h>#include <console/console.h>#include <device/device.h>#include <device/pci.h>#include <device/pci_ops.h>#include <device/pci_ids.h>#include "chip.h"#include "i82371eb.h"

Go to the source code of this file.

Functions | |

| static void | ide_init_enable (struct device *dev) |

| Initialize the IDE controller. More... | |

| static void | ide_init_udma33 (struct device *dev) |

| Initialize the Ultra DMA/33 support of the IDE controller. More... | |

| static void | ide_init_i82371fb_sb (struct device *dev) |

| IDE init for the Intel 82371FB/SB IDE controller. More... | |

| static void | ide_init_i82371ab_eb_mb (struct device *dev) |

| IDE init for the Intel 82371AB/EB/MB IDE controller. More... | |

Variables | |

| static const struct device_operations | ide_ops_fb_sb |

| static const struct device_operations | ide_ops_ab_eb_mb |

| static const struct pci_driver ide_driver_fb | __pci_driver |

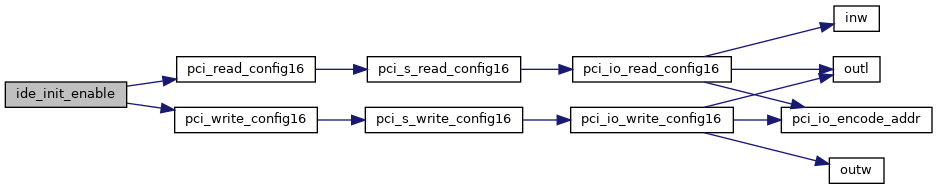

Initialize the IDE controller.

Depending on the configuration variables 'ide0_enable' and 'ide1_enable' enable or disable the primary and secondary IDE interface, respectively.

Depending on the configuration variable 'ide_legacy_enable' enable or disable access to the legacy IDE ports and the PCI Bus Master IDE I/O registers (this is required for e.g. FILO).

| dev | The device to use. |

Definition at line 26 of file ide.c.

References BIOS_DEBUG, device::chip_info, southbridge_intel_i82371eb_config::ide0_enable, southbridge_intel_i82371eb_config::ide1_enable, IDE_DECODE_ENABLE, southbridge_intel_i82371eb_config::ide_legacy_enable, IDETIM_PRI, IDETIM_SEC, ONOFF, PCI_COMMAND, PCI_COMMAND_IO, PCI_COMMAND_MASTER, pci_read_config16(), pci_write_config16(), and printk.

Referenced by ide_init_i82371fb_sb().

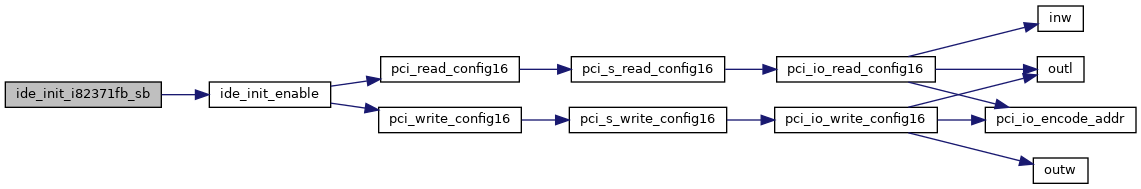

IDE init for the Intel 82371FB/SB IDE controller.

These devices do not support UDMA/33, so don't attempt to enable it.

| dev | The device to use. |

Definition at line 114 of file ide.c.

References ide_init_enable().

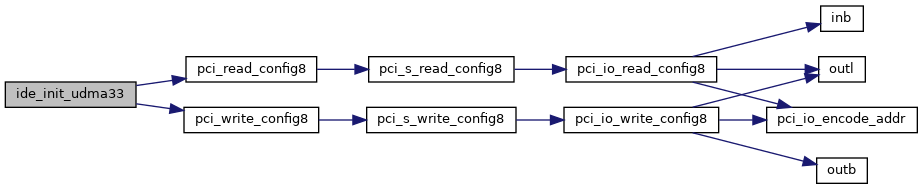

Initialize the Ultra DMA/33 support of the IDE controller.

Depending on the configuration variables 'ide0_drive0_udma33_enable', 'ide0_drive1_udma33_enable', 'ide1_drive0_udma33_enable', and 'ide1_drive1_udma33_enable' enable or disable Ultra DMA/33 support for the respective IDE controller and drive.

Only do that if the respective controller is actually enabled, of course.

| dev | The device to use. |

Definition at line 71 of file ide.c.

References BIOS_DEBUG, device::chip_info, southbridge_intel_i82371eb_config::ide0_drive0_udma33_enable, southbridge_intel_i82371eb_config::ide0_drive1_udma33_enable, southbridge_intel_i82371eb_config::ide0_enable, southbridge_intel_i82371eb_config::ide1_drive0_udma33_enable, southbridge_intel_i82371eb_config::ide1_drive1_udma33_enable, southbridge_intel_i82371eb_config::ide1_enable, ONOFF, pci_read_config8(), pci_write_config8(), printk, PSDE0, PSDE1, SSDE0, SSDE1, and UDMACTL.

|

static |

|

static |

|

static |