|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

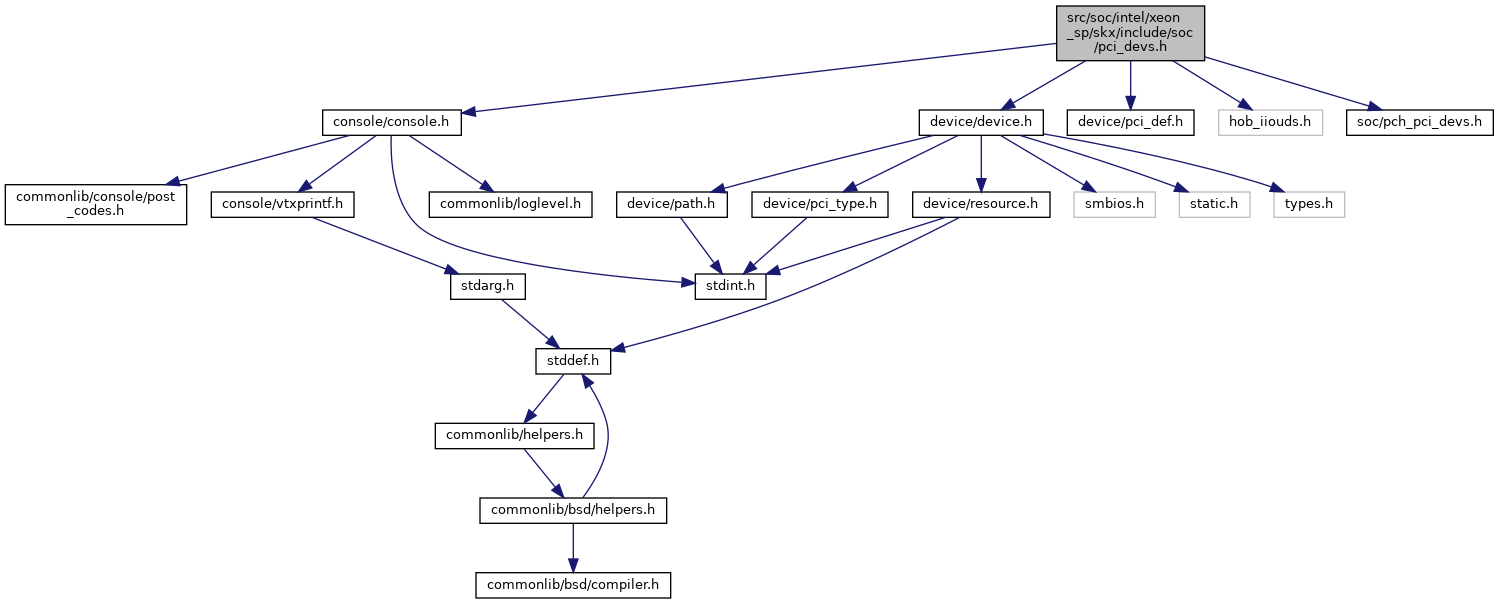

#include <console/console.h>#include <device/device.h>#include <device/pci_def.h>#include <hob_iiouds.h>#include <soc/pch_pci_devs.h>

Go to the source code of this file.

| #define _PCU_DEV | ( | bus, | |

| func | |||

| ) | pcidev_path_on_bus(bus, PCI_DEVFN(PCU_DEV, func)) |

Definition at line 31 of file pci_devs.h.

| #define _UBOX_DEV | ( | func | ) | pcidev_path_on_root_debug(PCI_DEVFN(UBOX_DEV, func), __func__) |

Definition at line 77 of file pci_devs.h.

| #define APIC_DEV_NUM 0x05 |

Definition at line 155 of file pci_devs.h.

| #define APIC_FUNC_NUM 0x00 |

Definition at line 156 of file pci_devs.h.

| #define BIOS_CMD_READ_PCU_MISC_CFG 0x5 |

Definition at line 59 of file pci_devs.h.

| #define BIOS_CMD_WRITE_PCU_MISC_CFG 0x6 |

Definition at line 60 of file pci_devs.h.

| #define BIOS_ERR_INVALID_CMD 0x01 |

Definition at line 61 of file pci_devs.h.

| #define BIOS_MB_CMD_MASK 0xff |

Definition at line 58 of file pci_devs.h.

| #define BIOS_MB_RUN_BUSY_MASK BIT(31) |

Definition at line 57 of file pci_devs.h.

| #define CBDMA_DEV_NUM 0x04 |

Definition at line 148 of file pci_devs.h.

| #define CHA_UTIL_ALL_DEV 29 |

Definition at line 133 of file pci_devs.h.

| #define CHA_UTIL_ALL_FUNC 1 |

Definition at line 134 of file pci_devs.h.

| #define CHA_UTIL_ALL_MMCFG_CSR 0xc0 |

Definition at line 135 of file pci_devs.h.

| #define DMI3_DEVID 0x2020 |

Definition at line 159 of file pci_devs.h.

| #define DMIRCBAR 0x50 |

Definition at line 160 of file pci_devs.h.

| #define dump_csr | ( | fmt, | |

| dev, | |||

| reg | |||

| ) |

Definition at line 12 of file pci_devs.h.

| #define dump_csr64 | ( | fmt, | |

| dev, | |||

| reg | |||

| ) |

Definition at line 18 of file pci_devs.h.

| #define ERRINJCON 0x1d8 |

Definition at line 161 of file pci_devs.h.

| #define IIO_CBDMA_MMIO_ALIGNMENT 14 |

Definition at line 150 of file pci_devs.h.

| #define IIO_CBDMA_MMIO_SIZE 0x10000 |

Definition at line 149 of file pci_devs.h.

| #define IIO_DFX_LCK_CTL 0x504 |

Definition at line 165 of file pci_devs.h.

| #define IIO_DFX_TSWCTL0 0x30c |

Definition at line 164 of file pci_devs.h.

| #define KTI_IN_PKGCSTATE_L1_MASK 0x7 /* 2:0 bits */ |

Definition at line 126 of file pci_devs.h.

| #define MAX_NON_TURBO_LIM_RATIO_MASK (0xff << MAX_NON_TURBO_LIM_RATIO_SHIFT) |

Definition at line 50 of file pci_devs.h.

| #define MAX_NON_TURBO_LIM_RATIO_SHIFT 8 /* 8:15 */ |

Definition at line 49 of file pci_devs.h.

| #define MMAP_VTD_CFG_REG_DEVID 0x2024 |

Definition at line 137 of file pci_devs.h.

| #define MMAP_VTD_STACK_CFG_REG_DEVID 0x2034 |

Definition at line 138 of file pci_devs.h.

| #define P_STATE_LIMITS_LOCK (1 << P_STATE_LIMITS_LOCK_SHIFT) |

Definition at line 45 of file pci_devs.h.

| #define P_STATE_LIMITS_LOCK_SHIFT 31 |

Definition at line 44 of file pci_devs.h.

| #define PAM_LOCK BIT(0) |

Definition at line 27 of file pci_devs.h.

| #define PCIE_IN_PKGCSTATE_L1_MASK 0xFFFFFF /* 23:0 bits */ |

Definition at line 124 of file pci_devs.h.

| #define PCODE_INIT_DONE1_MASK BIT(9) |

Definition at line 68 of file pci_devs.h.

| #define PCODE_INIT_DONE2_MASK BIT(10) |

Definition at line 69 of file pci_devs.h.

| #define PCODE_INIT_DONE3_MASK BIT(11) |

Definition at line 70 of file pci_devs.h.

| #define PCODE_INIT_DONE4_MASK BIT(12) |

Definition at line 71 of file pci_devs.h.

| #define PCU_CR0_CURRENT_CONFIG 0xf8 |

Definition at line 48 of file pci_devs.h.

| #define PCU_CR0_FUN 0 |

Definition at line 40 of file pci_devs.h.

| #define PCU_CR0_P_STATE_LIMITS 0xd8 |

Definition at line 43 of file pci_devs.h.

| #define PCU_CR0_PACKAGE_RAPL_LIMIT 0xe8 |

Definition at line 47 of file pci_devs.h.

| #define PCU_CR0_PLATFORM_INFO 0xa8 |

Definition at line 42 of file pci_devs.h.

| #define PCU_CR0_PMAX 0xf0 |

Definition at line 51 of file pci_devs.h.

| #define PCU_CR0_TEMPERATURE_TARGET 0xe4 |

Definition at line 46 of file pci_devs.h.

| #define PCU_CR1_BIOS_MB_DATA_REG 0x8c |

Definition at line 54 of file pci_devs.h.

| #define PCU_CR1_BIOS_MB_INTERFACE_REG 0x90 |

Definition at line 56 of file pci_devs.h.

| #define PCU_CR1_BIOS_RESET_CPL_REG 0x94 |

Definition at line 63 of file pci_devs.h.

| #define PCU_CR1_C2C3TT_REG 0xdc |

Definition at line 115 of file pci_devs.h.

| #define PCU_CR1_DESIRED_CORES_CFG2_REG 0xa0 |

Definition at line 73 of file pci_devs.h.

| #define PCU_CR1_DESIRED_CORES_CFG2_REG_LOCK_MASK BIT(31) |

Definition at line 74 of file pci_devs.h.

| #define PCU_CR1_FUN 1 |

Definition at line 38 of file pci_devs.h.

| #define PCU_CR1_MC_BIOS_REQ 0x98 |

Definition at line 120 of file pci_devs.h.

| #define PCU_CR1_PCIE_ILTR_OVRD 0xfc |

Definition at line 116 of file pci_devs.h.

| #define PCU_CR1_SAPMCTL 0xb0 |

Definition at line 117 of file pci_devs.h.

| #define PCU_CR2_DYNAMIC_PERF_POWER_CTL 0xdc |

Definition at line 127 of file pci_devs.h.

| #define PCU_CR2_FUN 2 |

Definition at line 122 of file pci_devs.h.

| #define PCU_CR2_PKG_CST_ENTRY_CRITERIA_MASK 0x8c |

Definition at line 123 of file pci_devs.h.

| #define PCU_CR2_PKG_CST_ENTRY_CRITERIA_MASK2 0x90 |

Definition at line 125 of file pci_devs.h.

| #define PCU_CR2_PROCHOT_RESPONSE_RATIO_REG 0xb0 |

Definition at line 130 of file pci_devs.h.

| #define PCU_DEV 30 |

Definition at line 37 of file pci_devs.h.

| #define PCU_DEV_CR0 | ( | bus | ) | _PCU_DEV(bus, PCU_CR0_FUN) |

Definition at line 41 of file pci_devs.h.

| #define PCU_IIO_STACK 1 |

Definition at line 36 of file pci_devs.h.

| #define PMAX_LOCK BIT(31) |

Definition at line 52 of file pci_devs.h.

| #define PROCHOT_RATIO 0xa /* bits 0:7 */ |

Definition at line 131 of file pci_devs.h.

| #define RST_CPL1_MASK BIT(1) |

Definition at line 64 of file pci_devs.h.

| #define RST_CPL2_MASK BIT(2) |

Definition at line 65 of file pci_devs.h.

| #define RST_CPL3_MASK BIT(3) |

Definition at line 66 of file pci_devs.h.

| #define RST_CPL4_MASK BIT(4) |

Definition at line 67 of file pci_devs.h.

| #define SAD_ALL_DEV 29 |

Definition at line 24 of file pci_devs.h.

| #define SAD_ALL_FUNC 0 |

Definition at line 25 of file pci_devs.h.

| #define SAD_ALL_PAM0123_CSR 0x40 |

Definition at line 26 of file pci_devs.h.

| #define SAD_ALL_PAM456_CSR 0x44 |

Definition at line 28 of file pci_devs.h.

| #define SAPMCTL_LOCK_MASK (1 << SAPMCTL_LOCK_SHIFT) |

Definition at line 119 of file pci_devs.h.

| #define SAPMCTL_LOCK_SHIFT 31 |

Definition at line 118 of file pci_devs.h.

| #define SMM_CODE_CHK_EN BIT(2) |

Definition at line 89 of file pci_devs.h.

| #define SMM_FEATURE_CONTROL 0x7c |

Definition at line 88 of file pci_devs.h.

| #define SMM_FEATURE_CONTROL_LOCK BIT(0) |

Definition at line 90 of file pci_devs.h.

| #define UBOX_DECS_BUS 0 |

Definition at line 92 of file pci_devs.h.

| #define UBOX_DECS_CPUBUSNO1_CSR 0xd0 |

Definition at line 96 of file pci_devs.h.

| #define UBOX_DECS_CPUBUSNO_CSR 0xcc |

Definition at line 95 of file pci_devs.h.

| #define UBOX_DECS_DEV 8 |

Definition at line 93 of file pci_devs.h.

| #define UBOX_DECS_FUNC 2 |

Definition at line 94 of file pci_devs.h.

| #define UBOX_DEV 8 |

Definition at line 82 of file pci_devs.h.

| #define UBOX_DEV_PMON _UBOX_DEV(UBOX_PMON_FUNC) |

Definition at line 87 of file pci_devs.h.

| #define UBOX_PMON_BUS 0 |

Definition at line 84 of file pci_devs.h.

| #define UBOX_PMON_DEV 8 |

Definition at line 85 of file pci_devs.h.

| #define UBOX_PMON_FUNC 1 |

Definition at line 86 of file pci_devs.h.

| #define UNCORE_PLIMIT_OVERRIDE_BIT 20 |

Definition at line 128 of file pci_devs.h.

| #define UNOCRE_PLIMIT_OVERRIDE_SHIFT (1 << UNCORE_PLIMIT_OVERRIDE_BIT) |

Definition at line 129 of file pci_devs.h.

| #define VMD_DEV_NUM 0x05 |

Definition at line 152 of file pci_devs.h.

| #define VMD_FUNC_NUM 0x05 |

Definition at line 153 of file pci_devs.h.

| #define VTD_CAP 0x08 |

Definition at line 109 of file pci_devs.h.

| #define VTD_CAP_HIGH 0x0C |

Definition at line 111 of file pci_devs.h.

| #define VTD_CAP_LOW 0x08 |

Definition at line 110 of file pci_devs.h.

| #define VTD_DEV | ( | bus | ) | pcidev_path_on_bus((bus), PCI_DEVFN(VTD_DEV_NUM, VTD_FUNC_NUM)) |

Definition at line 143 of file pci_devs.h.

| #define VTD_DEV_NUM 0x5 |

Definition at line 139 of file pci_devs.h.

| #define VTD_EXT_CAP_HIGH 0x14 |

Definition at line 112 of file pci_devs.h.

| #define VTD_EXT_CAP_LOW 0x10 |

Definition at line 101 of file pci_devs.h.

| #define VTD_FUNC_NUM 0x0 |

Definition at line 140 of file pci_devs.h.

| #define VTD_LTDPR 0x290 |

Definition at line 113 of file pci_devs.h.

| #define VTD_ME_BASE_CSR 0xf0 |

Definition at line 106 of file pci_devs.h.

| #define VTD_ME_LIMIT_CSR 0xf8 |

Definition at line 107 of file pci_devs.h.

| #define VTD_MMCFG_BASE_CSR 0x90 |

Definition at line 102 of file pci_devs.h.

| #define VTD_MMCFG_LIMIT_CSR 0x98 |

Definition at line 103 of file pci_devs.h.

| #define VTD_MMIOL_CSR 0xdc |

Definition at line 105 of file pci_devs.h.

| #define VTD_TOHM_CSR 0xd4 |

Definition at line 104 of file pci_devs.h.

| #define VTD_TOLM_CSR 0xd0 |

Definition at line 98 of file pci_devs.h.

| #define VTD_TSEG_BASE_CSR 0xa8 |

Definition at line 99 of file pci_devs.h.

| #define VTD_TSEG_LIMIT_CSR 0xac |

Definition at line 100 of file pci_devs.h.

| #define VTD_VERSION 0x00 |

Definition at line 108 of file pci_devs.h.