|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

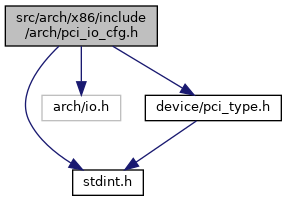

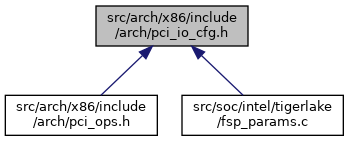

Go to the source code of this file.

|

static |

Definition at line 11 of file pci_io_cfg.h.

Referenced by pci_io_read_config16(), pci_io_read_config32(), pci_io_read_config8(), pci_io_write_config16(), pci_io_write_config32(), and pci_io_write_config8().

|

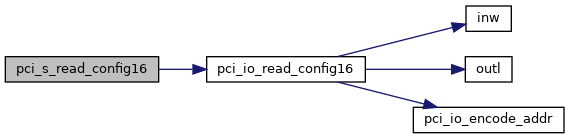

static |

Definition at line 33 of file pci_io_cfg.h.

References addr, inw(), outl(), and pci_io_encode_addr().

Referenced by pci_s_read_config16().

|

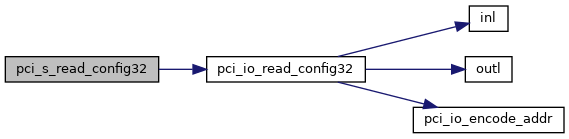

static |

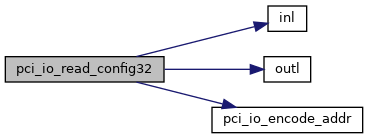

Definition at line 41 of file pci_io_cfg.h.

References addr, inl(), outl(), and pci_io_encode_addr().

Referenced by get_stack_busno(), pci_s_read_config32(), sanity_check_pci_mmconf(), uart_platform_base(), and unlock_pam_regions().

|

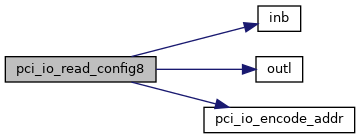

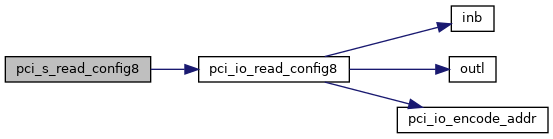

static |

Definition at line 25 of file pci_io_cfg.h.

References addr, inb(), outl(), and pci_io_encode_addr().

Referenced by pci_s_read_config8().

|

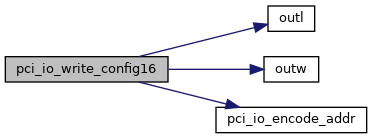

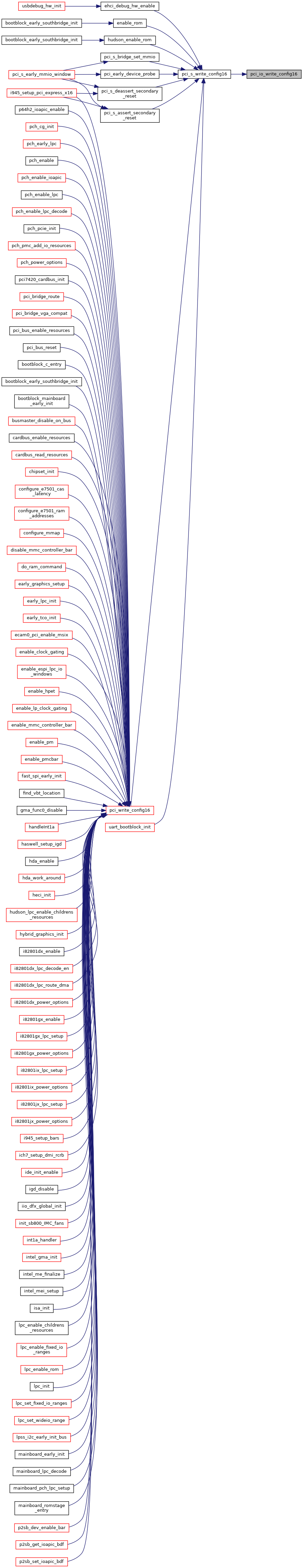

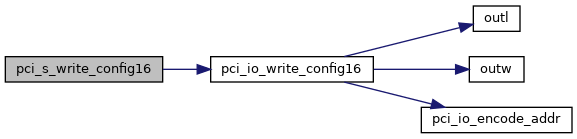

static |

Definition at line 57 of file pci_io_cfg.h.

References addr, outl(), outw(), pci_io_encode_addr(), and value.

Referenced by pci_s_write_config16().

|

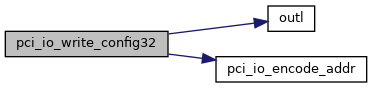

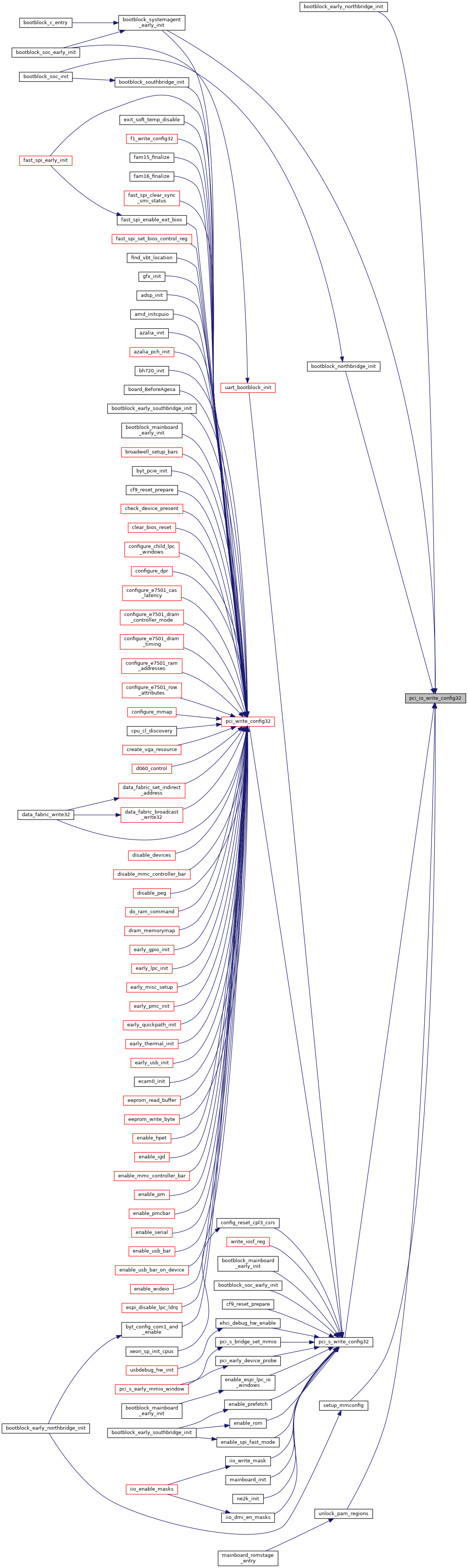

static |

Definition at line 65 of file pci_io_cfg.h.

References addr, outl(), pci_io_encode_addr(), and value.

Referenced by bootblock_early_northbridge_init(), bootblock_northbridge_init(), bootblock_systemagent_early_init(), pci_s_write_config32(), setup_mmconfig(), and unlock_pam_regions().

|

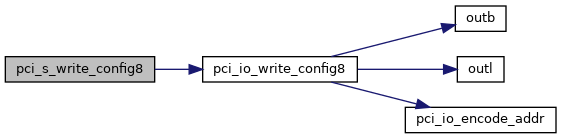

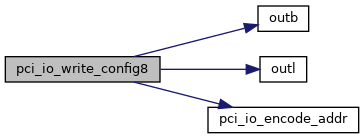

static |

Definition at line 49 of file pci_io_cfg.h.

References addr, outb(), outl(), pci_io_encode_addr(), and value.

Referenced by pci_s_write_config8().

|

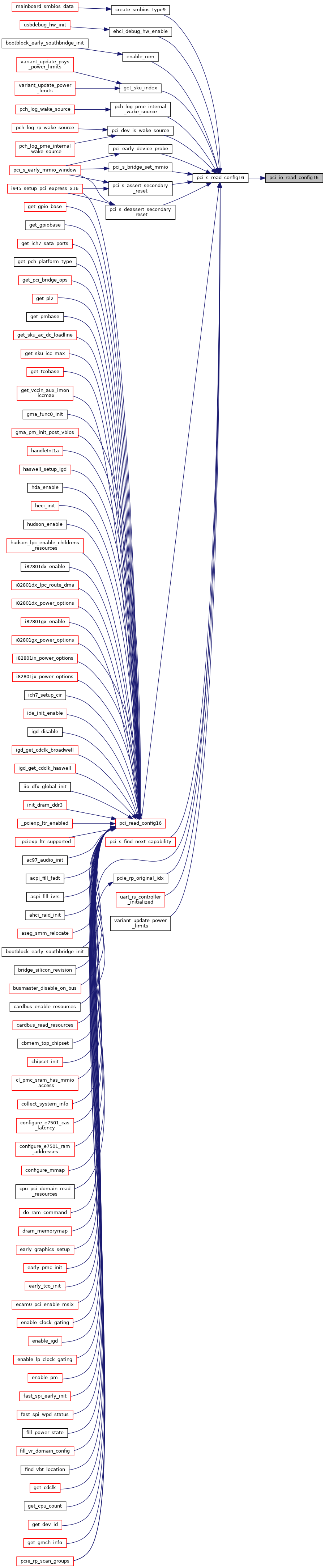

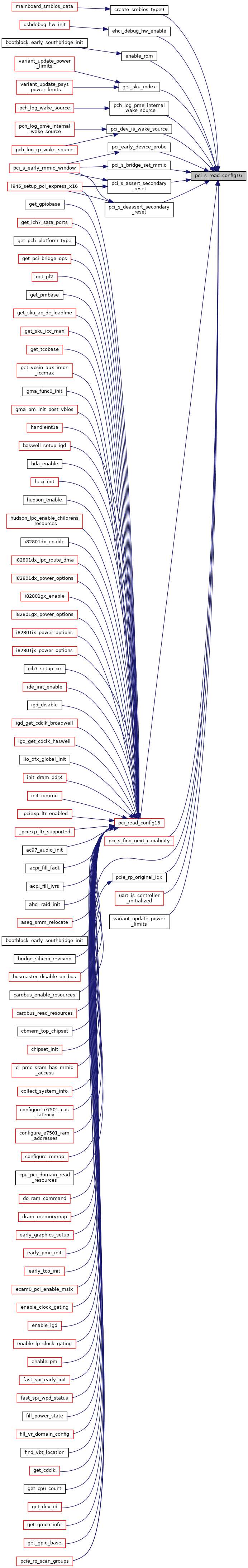

static |

Definition at line 86 of file pci_io_cfg.h.

References pci_io_read_config16().

Referenced by create_smbios_type9(), ehci_debug_hw_enable(), enable_rom(), get_sku_index(), pch_log_pme_internal_wake_source(), pci_dev_is_wake_source(), pci_early_device_probe(), pci_read_config16(), pci_s_assert_secondary_reset(), pci_s_bridge_set_mmio(), pci_s_deassert_secondary_reset(), pci_s_find_next_capability(), pcie_rp_original_idx(), pcie_rp_scan_groups(), uart_is_controller_initialized(), and variant_update_power_limits().

|

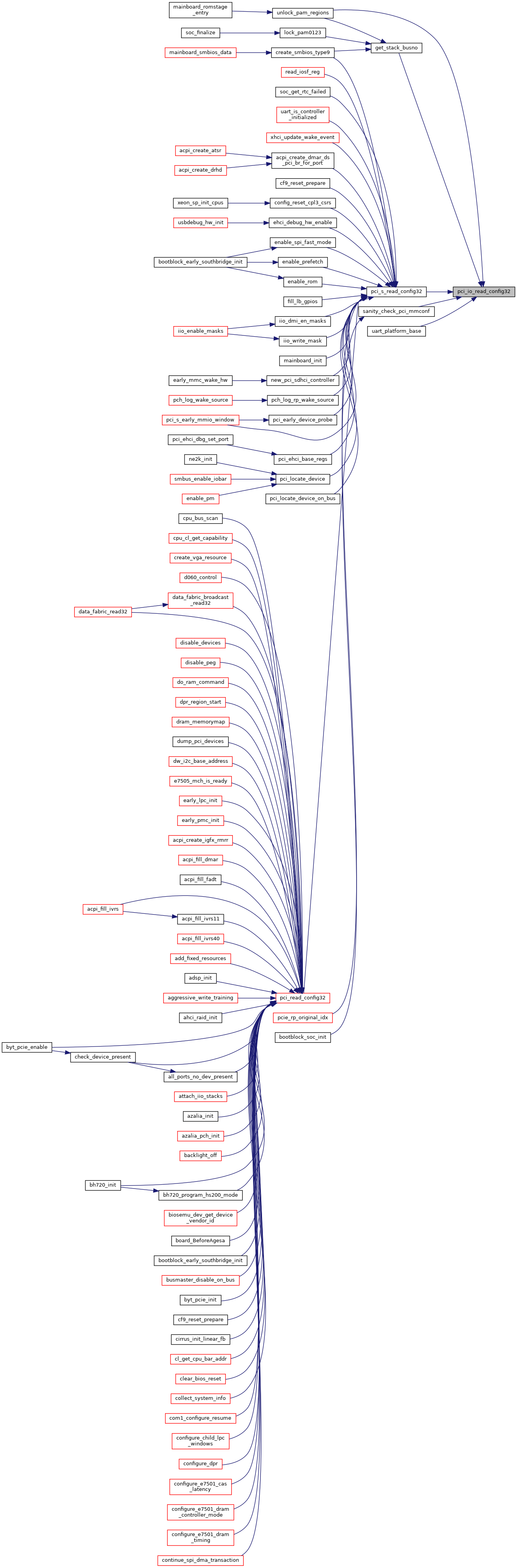

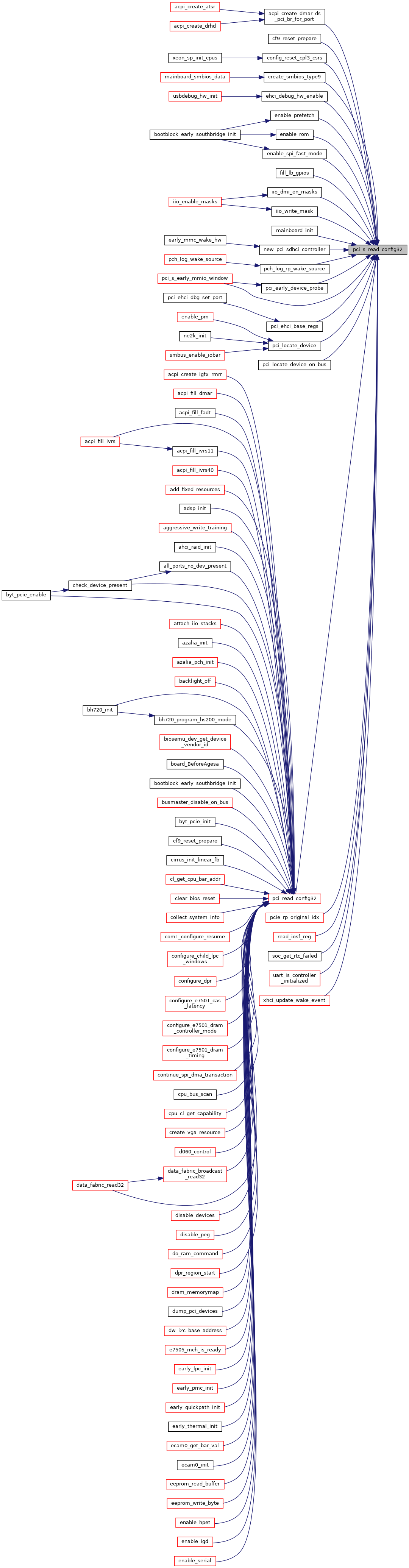

static |

Definition at line 92 of file pci_io_cfg.h.

References pci_io_read_config32().

Referenced by acpi_create_dmar_ds_pci_br_for_port(), cf9_reset_prepare(), config_reset_cpl3_csrs(), create_smbios_type9(), ehci_debug_hw_enable(), enable_prefetch(), enable_rom(), enable_spi_fast_mode(), fill_lb_gpios(), iio_dmi_en_masks(), iio_write_mask(), mainboard_init(), new_pci_sdhci_controller(), pch_log_rp_wake_source(), pci_early_device_probe(), pci_ehci_base_regs(), pci_locate_device(), pci_locate_device_on_bus(), pci_read_config32(), pci_s_early_mmio_window(), pcie_rp_original_idx(), read_iosf_reg(), soc_get_rtc_failed(), uart_is_controller_initialized(), and xhci_update_wake_event().

|

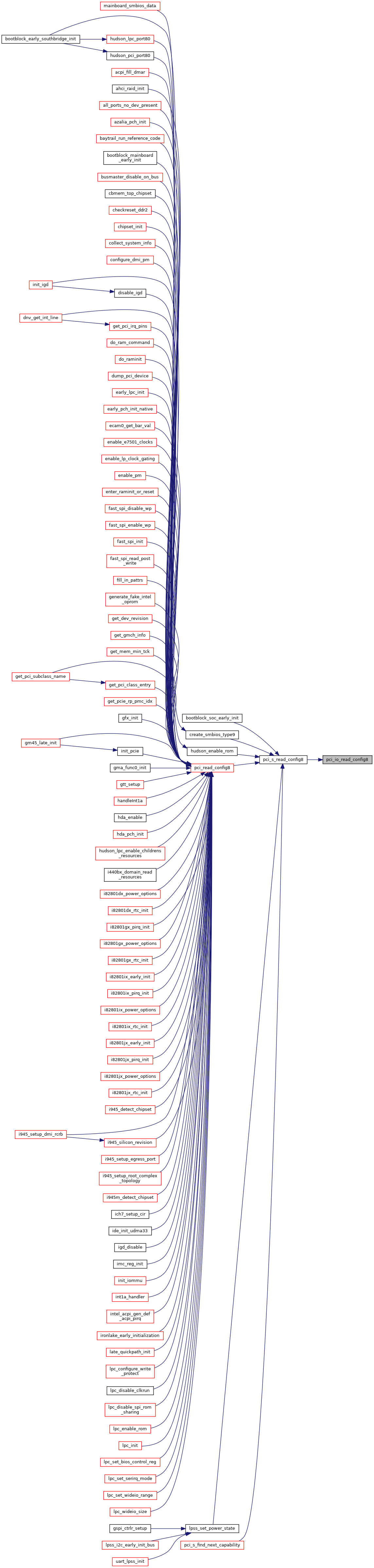

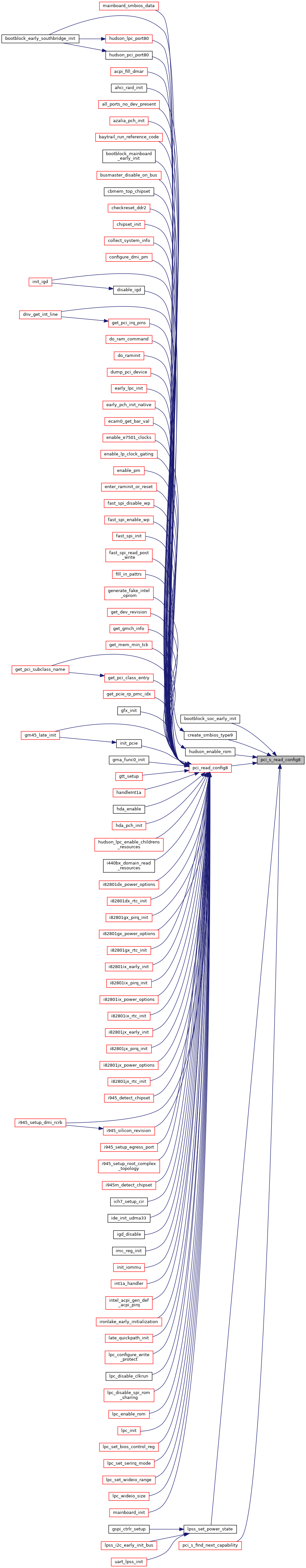

static |

Definition at line 80 of file pci_io_cfg.h.

References pci_io_read_config8().

Referenced by bootblock_soc_early_init(), create_smbios_type9(), hudson_enable_rom(), lpss_set_power_state(), pci_read_config8(), and pci_s_find_next_capability().

|

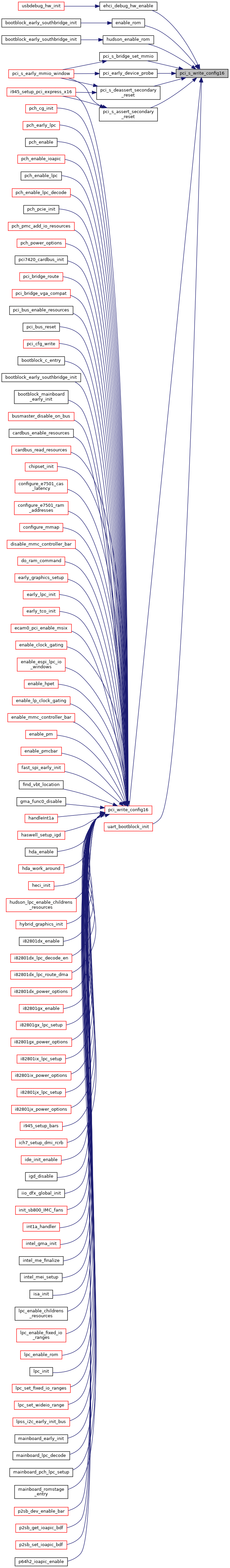

static |

Definition at line 104 of file pci_io_cfg.h.

References pci_io_write_config16(), and value.

Referenced by ehci_debug_hw_enable(), enable_rom(), hudson_enable_rom(), pci_early_device_probe(), pci_s_assert_secondary_reset(), pci_s_bridge_set_mmio(), pci_s_deassert_secondary_reset(), pci_write_config16(), and uart_bootblock_init().

|

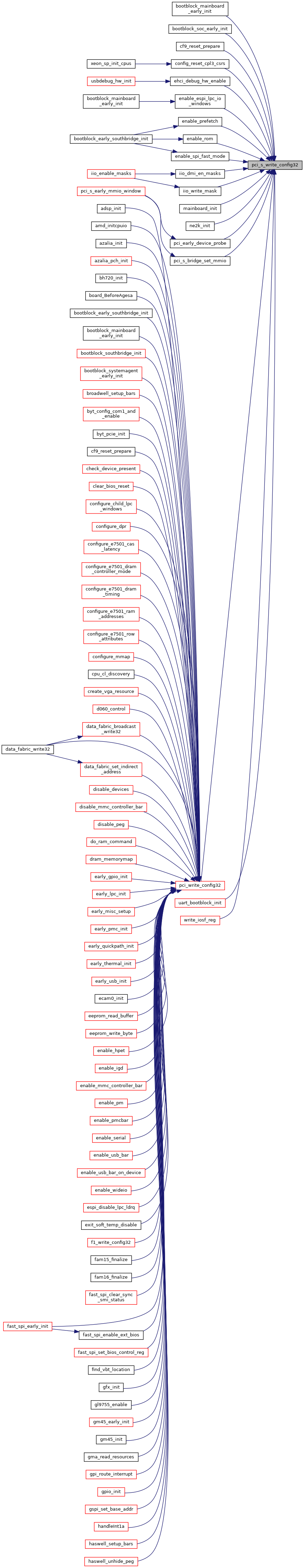

static |

Definition at line 110 of file pci_io_cfg.h.

References pci_io_write_config32(), and value.

Referenced by bootblock_mainboard_early_init(), bootblock_soc_early_init(), cf9_reset_prepare(), config_reset_cpl3_csrs(), ehci_debug_hw_enable(), enable_espi_lpc_io_windows(), enable_prefetch(), enable_rom(), enable_spi_fast_mode(), iio_dmi_en_masks(), iio_write_mask(), mainboard_init(), ne2k_init(), pci_early_device_probe(), pci_s_bridge_set_mmio(), pci_write_config32(), uart_bootblock_init(), and write_iosf_reg().

|

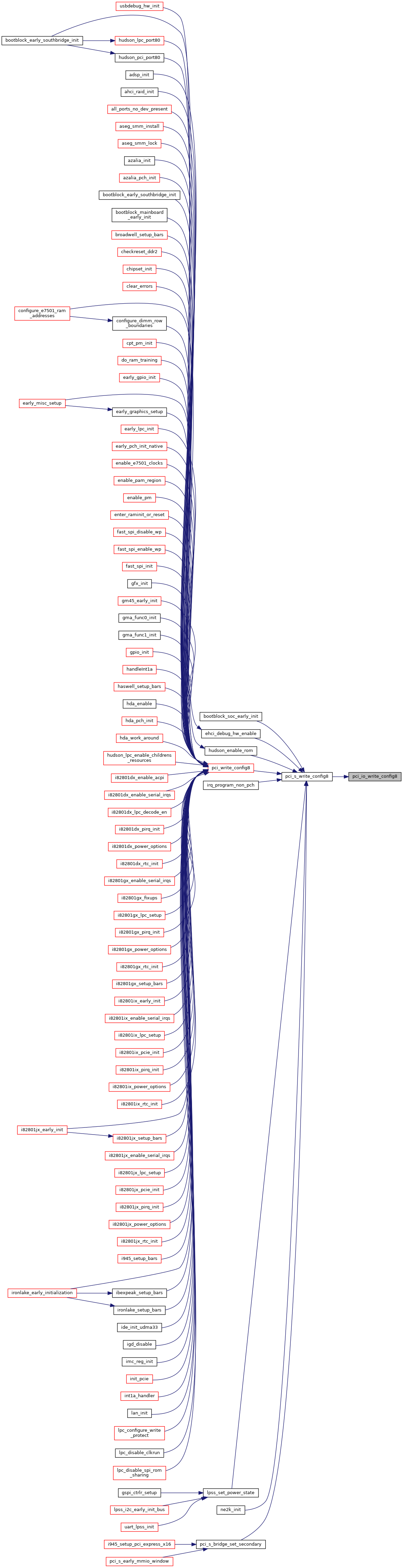

static |

Definition at line 98 of file pci_io_cfg.h.

References pci_io_write_config8(), and value.

Referenced by bootblock_soc_early_init(), ehci_debug_hw_enable(), hudson_enable_rom(), irq_program_non_pch(), lpss_set_power_state(), ne2k_init(), pci_s_bridge_set_secondary(), and pci_write_config8().