|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

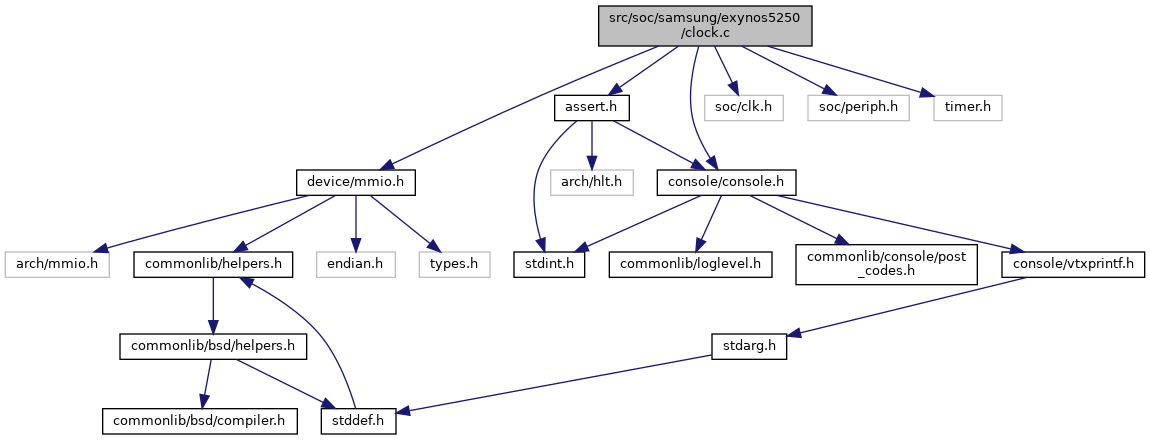

#include <device/mmio.h>#include <assert.h>#include <console/console.h>#include <soc/clk.h>#include <soc/periph.h>#include <timer.h>

Go to the source code of this file.

Macros | |

| #define | CONF_SYS_CLK_FREQ 24000000 |

Functions | |

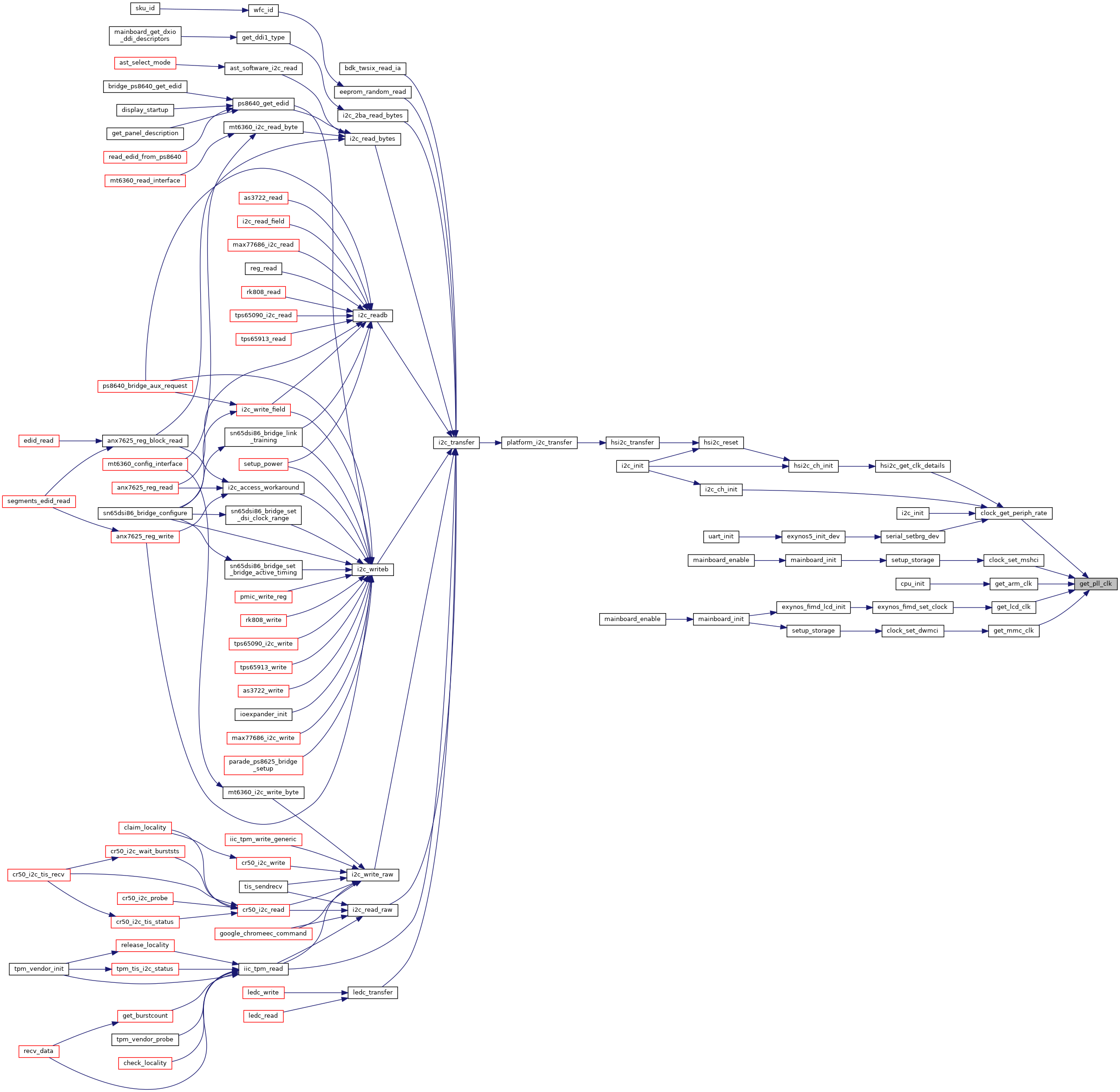

| unsigned long | get_pll_clk (int pllreg) |

| unsigned long | clock_get_periph_rate (enum periph_id peripheral) |

| get the clk frequency of the required peripheral More... | |

| unsigned long | get_arm_clk (void) |

| struct arm_clk_ratios * | get_arm_clk_ratios (void) |

| Get the clock ratios for CPU configuration. More... | |

| void | set_mmc_clk (int dev_index, unsigned int div) |

| void | clock_ll_set_pre_ratio (enum periph_id periph_id, unsigned int divisor) |

| Low-level function to set the clock pre-ratio for a peripheral. More... | |

| void | clock_ll_set_ratio (enum periph_id periph_id, unsigned int divisor) |

| Low-level function to set the clock ratio for a peripheral. More... | |

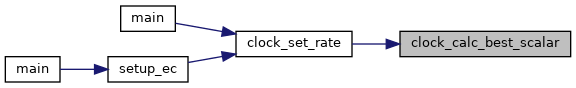

| static int | clock_calc_best_scalar (unsigned int main_scaler_bits, unsigned int fine_scalar_bits, unsigned int input_rate, unsigned int target_rate, unsigned int *best_fine_scalar) |

| Linearly searches for the most accurate main and fine stage clock scalars (divisors) for a specified target frequency and scalar bit sizes by checking all multiples of main_scalar_bits values. More... | |

| int | clock_set_rate (enum periph_id periph_id, unsigned int rate) |

| Low-level function that selects the best clock scalars for a given rate and sets up the given peripheral's clock accordingly. More... | |

| int | clock_set_mshci (enum periph_id peripheral) |

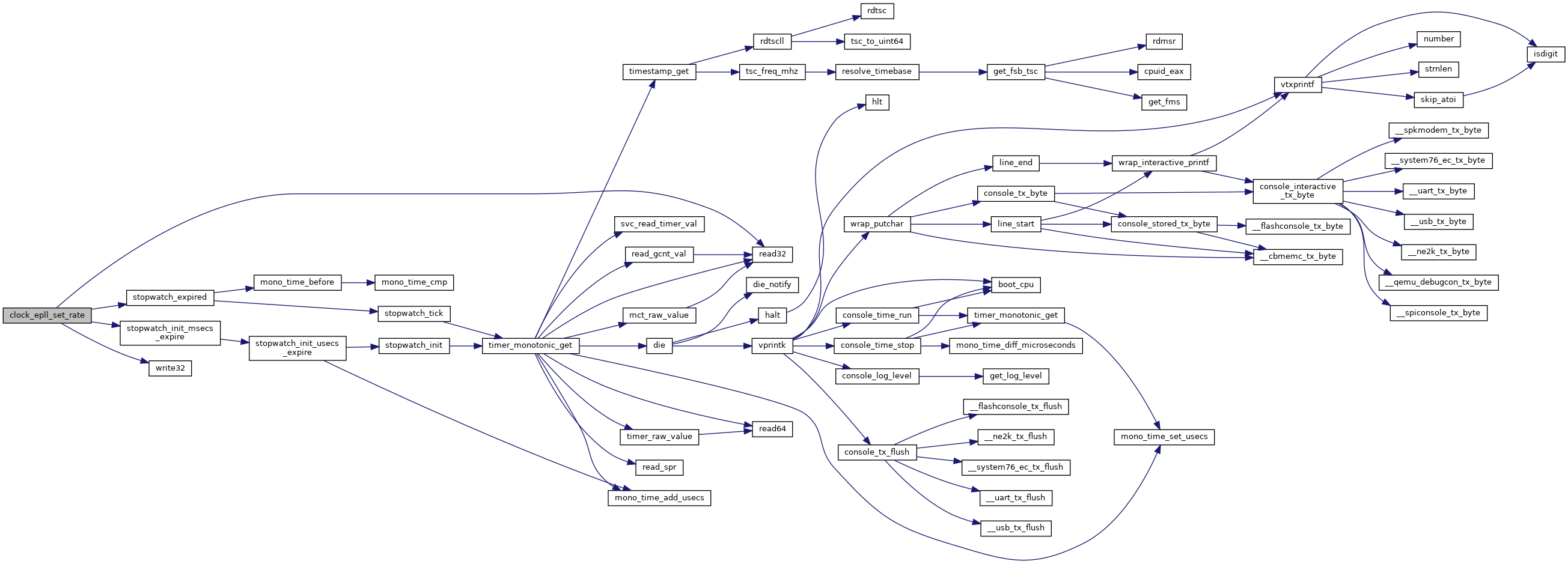

| int | clock_epll_set_rate (unsigned long rate) |

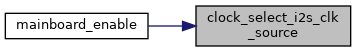

| void | clock_select_i2s_clk_source (void) |

| int | clock_set_i2s_clk_prescaler (unsigned int src_frq, unsigned int dst_frq) |

Variables | |

| static struct arm_clk_ratios | arm_clk_ratios [] |

| static struct clk_bit_info | clk_bit_info [PERIPH_ID_COUNT] |

| static struct st_epll_con_val | epll_div [] |

|

static |

Linearly searches for the most accurate main and fine stage clock scalars (divisors) for a specified target frequency and scalar bit sizes by checking all multiples of main_scalar_bits values.

Will always return scalars up to or slower than target.

| main_scalar_bits | Number of main scalar bits, must be > 0 and < 32 |

| fine_scalar_bits | Number of fine scalar bits, must be > 0 and < 32 |

| input_rate | Clock frequency to be scaled in Hz |

| target_rate | Desired clock frequency in Hz |

| best_fine_scalar | Pointer to store the fine stage divisor |

Definition at line 467 of file clock.c.

References ASSERT, BIOS_DEBUG, MAX, MIN, NULL, and printk.

Referenced by clock_set_rate().

| int clock_epll_set_rate | ( | unsigned long | rate | ) |

Definition at line 577 of file clock.c.

References ARRAY_SIZE, BIOS_DEBUG, st_epll_con_val::en_lock_det, exynos5_clock::epll_con0, EPLL_CON0_LOCK_DET_EN_MASK, EPLL_CON0_LOCK_DET_EN_SHIFT, EPLL_CON0_MDIV_MASK, EPLL_CON0_MDIV_SHIFT, EPLL_CON0_PDIV_MASK, EPLL_CON0_PDIV_SHIFT, EPLL_CON0_SDIV_MASK, EPLL_CON0_SDIV_SHIFT, exynos5_clock::epll_con1, epll_div, exynos5_clock::epll_lock, EXYNOS5_EPLLCON0_LOCKED_SHIFT, exynos_clock, st_epll_con_val::k_dsm, st_epll_con_val::m_div, st_epll_con_val::p_div, printk, read32(), st_epll_con_val::s_div, stopwatch_expired(), stopwatch_init_msecs_expire(), TIMEOUT_EPLL_LOCK, and write32().

Referenced by mainboard_enable().

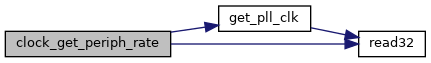

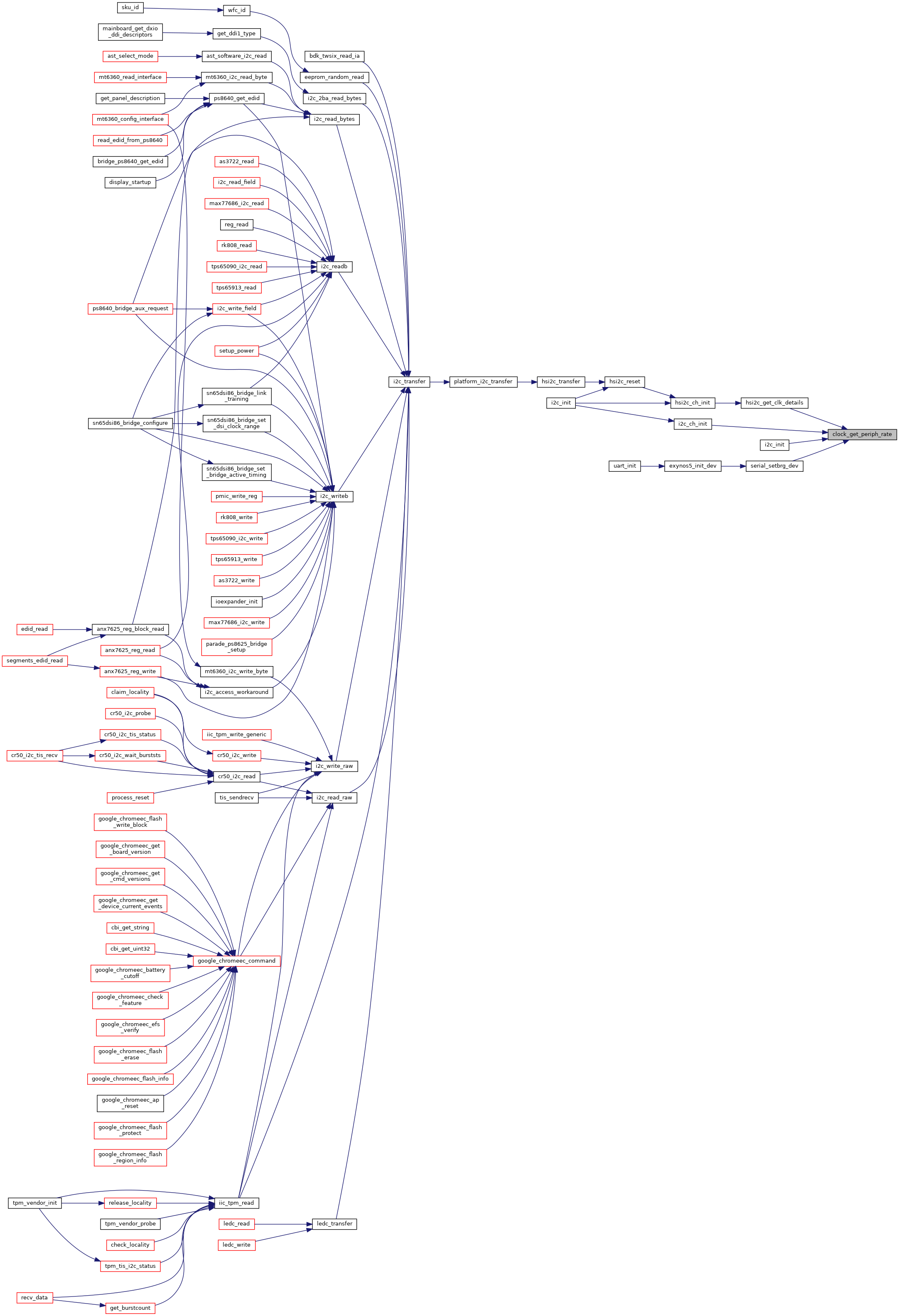

get the clk frequency of the required peripheral

| peripheral | Peripheral id |

Definition at line 220 of file clock.c.

References BIOS_DEBUG, BPLL, clk_bit_info::div_bit, exynos5_clock::div_fsys0, exynos5_clock::div_fsys1, exynos5_clock::div_peric0, exynos5_clock::div_peric1, exynos5_clock::div_peric2, exynos5_clock::div_peric3, exynos5_clock::div_top0, exynos5_clock::div_top1, EPLL, exynos_clock, get_pll_clk(), MPLL, clk_bit_info::n_src_bits, PERIPH_ID_I2C0, PERIPH_ID_I2C1, PERIPH_ID_I2C2, PERIPH_ID_I2C3, PERIPH_ID_I2C4, PERIPH_ID_I2C5, PERIPH_ID_I2C6, PERIPH_ID_I2C7, PERIPH_ID_PWM0, PERIPH_ID_PWM1, PERIPH_ID_PWM2, PERIPH_ID_PWM3, PERIPH_ID_PWM4, PERIPH_ID_SATA, PERIPH_ID_SDMMC0, PERIPH_ID_SDMMC1, PERIPH_ID_SDMMC2, PERIPH_ID_SDMMC3, PERIPH_ID_SPI0, PERIPH_ID_SPI1, PERIPH_ID_SPI2, PERIPH_ID_SPI3, PERIPH_ID_SPI4, PERIPH_ID_UART0, PERIPH_ID_UART1, PERIPH_ID_UART2, PERIPH_ID_UART3, clk_bit_info::prediv_bit, printk, read32(), exynos5_clock::sclk_div_isp, exynos5_clock::sclk_src_isp, clk_bit_info::src_bit, SRC_EPLL, exynos5_clock::src_fsys, SRC_MPLL, exynos5_clock::src_peric0, exynos5_clock::src_peric1, SRC_VPLL, and VPLL.

Referenced by hsi2c_get_clk_details(), i2c_ch_init(), i2c_init(), and serial_setbrg_dev().

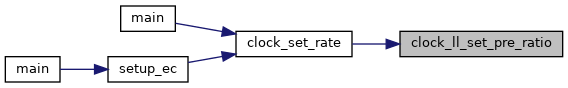

Low-level function to set the clock pre-ratio for a peripheral.

| periph_id | Peripheral ID of peripheral to change |

| divisor | New divisor for this peripheral's clock |

Definition at line 374 of file clock.c.

References BIOS_DEBUG, clrsetbits32, exynos5_clock::div_peric1, exynos5_clock::div_peric2, exynos_clock, mask, PERIPH_ID_SPI0, PERIPH_ID_SPI1, PERIPH_ID_SPI2, PERIPH_ID_SPI3, PERIPH_ID_SPI4, printk, and exynos5_clock::sclk_div_isp.

Referenced by clock_set_rate().

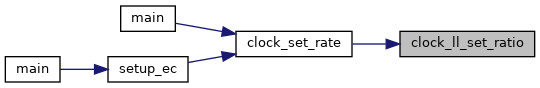

Low-level function to set the clock ratio for a peripheral.

| periph_id | Peripheral ID of peripheral to change |

| divisor | New divisor for this peripheral's clock |

Definition at line 417 of file clock.c.

References BIOS_DEBUG, clrsetbits32, exynos5_clock::div_peric1, exynos5_clock::div_peric2, exynos_clock, mask, PERIPH_ID_SPI0, PERIPH_ID_SPI1, PERIPH_ID_SPI2, PERIPH_ID_SPI3, PERIPH_ID_SPI4, printk, and exynos5_clock::sclk_div_isp.

Referenced by clock_set_rate().

Definition at line 631 of file clock.c.

References AUDIO1_SEL_MASK, CLK_SRC_SCLK_EPLL, clrsetbits32, exynos_clock, and exynos5_clock::src_peric1.

Referenced by mainboard_enable().

Definition at line 637 of file clock.c.

References AUDIO_1_RATIO_MASK, BIOS_DEBUG, clrsetbits32, exynos5_clock::div_peric4, exynos_clock, and printk.

Referenced by mainboard_enable().

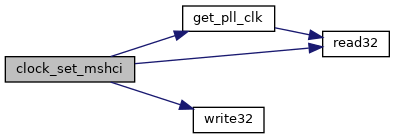

| int clock_set_mshci | ( | enum periph_id | peripheral | ) |

Definition at line 540 of file clock.c.

References addr, BIOS_DEBUG, exynos5_clock::div_fsys1, exynos5_clock::div_fsys2, exynos_clock, get_pll_clk(), MPLL, PERIPH_ID_SDMMC0, PERIPH_ID_SDMMC2, printk, read32(), and write32().

Referenced by setup_storage().

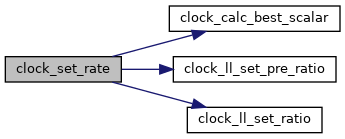

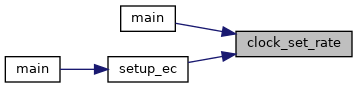

Low-level function that selects the best clock scalars for a given rate and sets up the given peripheral's clock accordingly.

| periph_id | Peripheral ID of peripheral to change |

| rate | Desired clock rate in Hz |

Definition at line 511 of file clock.c.

References BIOS_DEBUG, clock_calc_best_scalar(), clock_ll_set_pre_ratio(), clock_ll_set_ratio(), PERIPH_ID_SPI0, PERIPH_ID_SPI1, PERIPH_ID_SPI2, PERIPH_ID_SPI3, PERIPH_ID_SPI4, and printk.

Referenced by main(), and setup_ec().

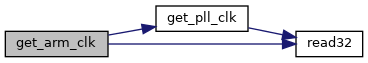

Definition at line 315 of file clock.c.

References APLL, exynos5_clock::div_cpu0, exynos_clock, get_pll_clk(), and read32().

Referenced by cpu_init().

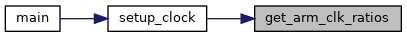

| struct arm_clk_ratios* get_arm_clk_ratios | ( | void | ) |

Get the clock ratios for CPU configuration.

Definition at line 334 of file clock.c.

References arm_clk_ratios::arm_ratio, ARRAY_SIZE, and NULL.

Referenced by setup_clock().

| unsigned long get_pll_clk | ( | int | pllreg | ) |

Definition at line 156 of file clock.c.

References APLL, exynos5_clock::apll_con0, BIOS_DEBUG, BPLL, exynos5_clock::bpll_con0, CONF_SYS_CLK_FREQ, EPLL, exynos5_clock::epll_con0, exynos5_clock::epll_con1, exynos_clock, m, mask, MPLL, exynos5_clock::mpll_con0, printk, read32(), s, VPLL, exynos5_clock::vpll_con0, and exynos5_clock::vpll_con1.

Referenced by clock_get_periph_rate(), clock_set_mshci(), get_arm_clk(), get_lcd_clk(), and get_mmc_clk().

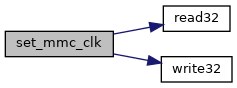

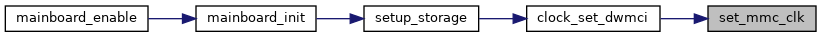

Definition at line 350 of file clock.c.

References addr, exynos5_clock::div_fsys1, exynos5_clock::div_fsys2, exynos_clock, read32(), val, and write32().

Referenced by clock_set_dwmci().

|

static |

|

static |

|

static |

Definition at line 1 of file clock.c.

Referenced by clock_epll_set_rate().